高端路由器内部的各种组件以及它们如何影响整体功耗研究

描述

高端路由器——基础知识

高端路由器通常有两种形式:独立系统或模块化系统。独立路由器通常是一个 1RU(机架单元)到 3 RU 高的盒子,其前面板具有固定数量的端口,主要用于中小型企业网络或数据中心内部。

随着网络 ASIC 占用的带宽越来越多,这些独立系统的吞吐量将达到 14.4Tbps。针对 400G 端口密度进行优化的 14.4Tbps 系统需要前面板容纳 36 个 400G 端口,这可能会占据前面板的大部分区域。大于 14.4Tbps 的路由器通常需要 800G 光学器件才能使系统带宽完全饱和。

线卡包含一个或两个网络 ASIC,用于接收来自前面板网络端口的流量。这些 ASIC 可以通过高速串行器/解串器 (SerDes) 和背板连接器与背板中的所有交换fabric卡进行通信。这提供了任意到任意的连接,其中线卡的网络端口可以发送和接收来自系统中任何其他线路卡的流量。

这些系统通常有 4-20 个插槽配置。它们的规模更大,客户可以根据需要灵活地购买线卡来升级带宽。如今,密度超过 14.4Tbps 的线卡并不罕见。对于 8 插槽机箱,这相当于 115Tbps 的系统带宽!在这样的规模下,向线路卡和结构卡内的各种组件供电以及冷却(消除这些组件产生的热量)是一项挑战。

路由器组件

为了更好地了解路由器功率,了解系统内不同组件的功能和功率要求非常重要,它们共同构成了总功率。

前面板/光模块

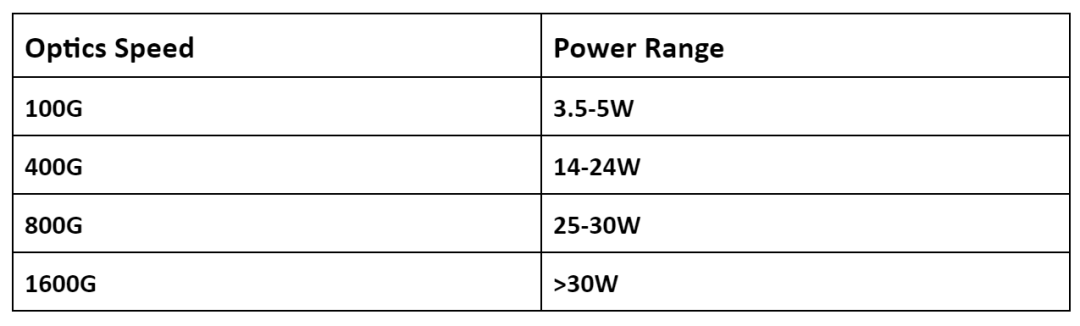

前面板附近有光笼,用于连接光模块。这些光模块承载进出系统的网络流量。光模块在较高速度下会消耗大量功率。这些模块所消耗的功率根据模块的类型和传输距离(光信号在没有信号衰减的情况下可以传输的时间)而有很大差异。在36 x 400G 端口的 14.4Tbps 线卡中,光模块本身在完全填充和加载时可能消耗 500-860W 的功率。类似的,一个 36 x 800G 端口的 28.8Tbps 线卡,光模块需要约 1100W 的功率。

降低光传输过程中的成本/功耗是近十年来研究的热点话题。

在这方面也不断有创新,一些供应商提供硅光子收发器,将分立元件集成在光子集成威廉希尔官方网站

中,以减少面积/成本和功耗。用于实现更高数据速率的 PAM4 信号传输、不主动传输时的低功耗模式以及改进的激光器、光电二极管、调制器和数字信号处理器 (DSP) 威廉希尔官方网站

都有助于降低光学器件的功耗。因此,当在特定范围内从 400G 光学器件变为 800G 光学器件时,功率仅增加了 1.5 倍,如上表所示。

Flyover cables

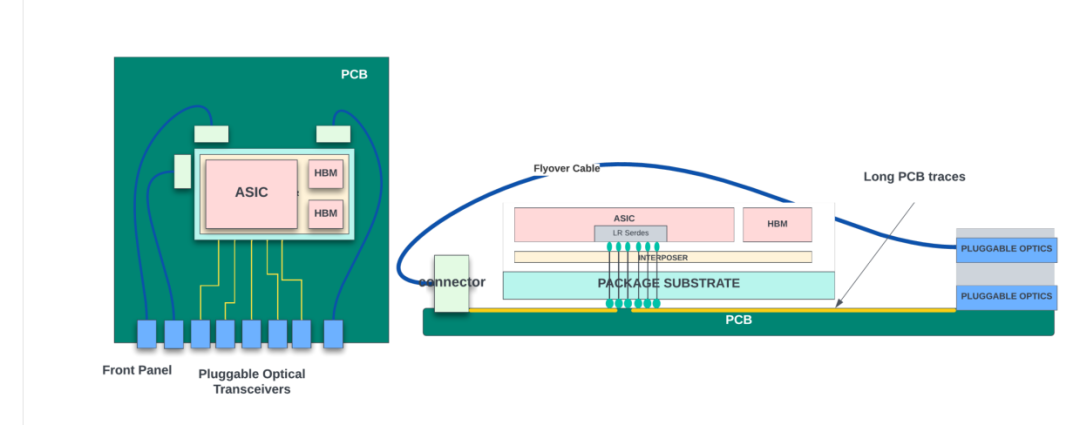

Flyover cables是高性能铜缆,可用于将 ASIC 的高速 SerDes 接口连接到前面板光学笼或背板连接器。

随着系统吞吐量的增加,威廉希尔官方网站 板上的空间有限,几乎不可能仅使用 PCB 走线来路由所有高速信号。Flyover cables可有效利用威廉希尔官方网站 板空间,不易受到电磁干扰,还可以通过减少信号路径的电容来帮助降低功耗。然而,如果放置和固定不当,它们可能会对气流造成一些阻碍,并可能给热管理系统带来一些挑战。

CPU复合

高端路由器中的 CPU 复合体提供在复杂网络环境中管理和操作路由器所需的控制平面处理、管理配置、安全、服务、监控和报告功能。它有自己的 DRAM 作为外部存储器。中档 Intel/AMD 处理器通常用于此复合。

网络 ASIC

这些芯片是路由器的核心。它们通过跨接电缆或威廉希尔官方网站 板上的 PCB 走线从连接到前面板端口的光模块接收网络流量,检查各种接头并采取措施。数据包处理描述了检查数据包标头并决定后续步骤的任务。

该操作可以是确定数据包必须通过其离开路由器的最终物理接口、排队并调度从该接口发出、在违反流量规则/检查时丢弃数据包,或者将数据包发送到控制平面以进行进一步处理、检查等。这些芯片包含数十亿个晶体管来执行这些功能。它们具有数百兆字节的片上内存,用于延迟带宽缓冲和数据结构,并且通常在封装中与高带宽存储器 (HBM) 集成。网络芯片消耗了路由器很大一部分功率。

在模块化系统线卡中使用的网络 ASIC 还具有连接到背板交换fabric的高速接口。

| 具有网络 ASIC 和光学器件的 PCB 板的概念图

可选重定时器

网络 ASIC 通过高速 SerDes 接收来自网络端口或背板的流量。这些高速 SerDes 将并行数据转换为串行格式,并通过铜介质(PCB 走线或Flyover cables)高速传输。高速信号在传输介质中存在信号衰减和退化的情况。

SerDes 的范围是 SerDes 在不使用信号调节或其他信号增强技术的情况下可以可靠地传输数据的最大距离。它由数据速率、传输介质类型和传输信号的质量决定。由于衰减、失真和噪声,信号质量在较高数据速率下可能会下降,这使得接收端的信号检测和解码变得更加困难,进而SerDes 无错误传输数据的最大距离也缩小了。

当网络ASIC向网络端口传输数据时,ASIC内部的SerDes只需将信号驱动至前面板光模块即可。这些光模块通常带有集成重定时器。重定时器是一种信号调节装置,有助于清理高速数据。它通过捕获输入信号并以正确的幅度和时间重新生成信号,从而实现重传。

在模块化系统中,当 ASIC 通过交换结构将信号传输到另一个线卡时,信号可能会通过线卡走线、连接线卡和交换结构卡之间的连接器以及通过交换结构的走线导致衰减很多。一些高速链路可能需要线卡或结构卡中的重定时器。这些重定时器非常耗电,并且它们基本上包含一对 SerDes,用于每个方向的发送和接收。

供电系统

供电系统通常由一个AC/DC转换器和多个本地降压DC/DC转换器组成。大多数系统为 AC/DC 转换器提供 1+1 冗余。这些转换器将墙壁插座的交流电转换为直流电,从而产生约 12-16V 的直流输出电压。转换过程中由于散热和电阻会造成一定的能量损失。典型转换器的效率损失在 5-10% 之间。因此,一个2200W AC/DC 转换器在满载时可能消耗 2300-2440W 的功率。

网络系统中的每个组件都需要特定的功率才能运行。所需功率由器件的电压和电流参数相乘计算得出。某些组件(例如网络 ASIC)需要多个电压轨。例如,在典型的网络 ASIC 中,数字逻辑需要比 SerDes 等模拟组件更小的电压(0.75-0.90V 之间),而模拟组件的运行可能需要 1-1.1V 之间的电压。同样,系统中的CPU和其他FPGA也有自己的电压和电流要求。

AC/DC转换器的直流输出电压通常为12V或更高。本地 DC/DC 转换器或负载点 (POL) 转换器用于将此电压降压至各种组件所需的 <1.5V。通过在靠近负载的位置提供电源转换,POL 转换器可以提高电源效率、减少电压降并提高整体系统性能。

这些 POL 转换器的效率在 90-95% 之间。此外,该系统还配备了热插拔转换器,可以保护内部组件免受电流和电压尖峰的影响。

通过使用高质量元件、最小化元件电阻以及优化开关频率,可以提高这些 AC/DC 和 POL 转换器的效率。

配电网络

电力输送(或在指定电压下向系统中的每个组件提供指定电流)通常是通过 PCB 板中的铜迹线完成的,这些铜迹线在电源单元 (PSU) 和 POL 转换器之间以及从转换器到系统的各个组件之间传输电流。这些铜迹线的电阻有限,因此当电流通过时,它们会耗散功率,这称为焦耳热。使用更宽的走线、优化更短的走线、减少过孔、多个电源层以及探索其他低电阻材料作为铜走线的替代品等方式都可以用来减少焦耳热。

转换器的低效率和通过铜迹线的功耗将要求为系统提供比所有组件消耗的总功率更大的功率。

热管理系统

所有组件(光学器件、CPU、ASIC、重定时器、转换器)在运行过程中消耗电能时都会产生热量。如果热量不能有效消散,可能会使组件内部过热并导致其失效或故障。

例如,在 ASIC 中,结温(晶体管结温)是晶体管内两种不同半导体材料相遇的接触点处的温度。结温随着晶体管功耗的增加而增加。结温影响晶体管的性能和可靠性。半导体制造商设定了最高结温,超过该结温 ASIC 就不再可靠,通常还会导致晶体管永久损坏。因此,任何热管理解决方案都应在结温超出规格之前有效地消除 ASIC 散发的热量,从而使 ASIC 的结温保持在规格范围内。同样的,其他系统组件也都有自己必须满足的温度规格。

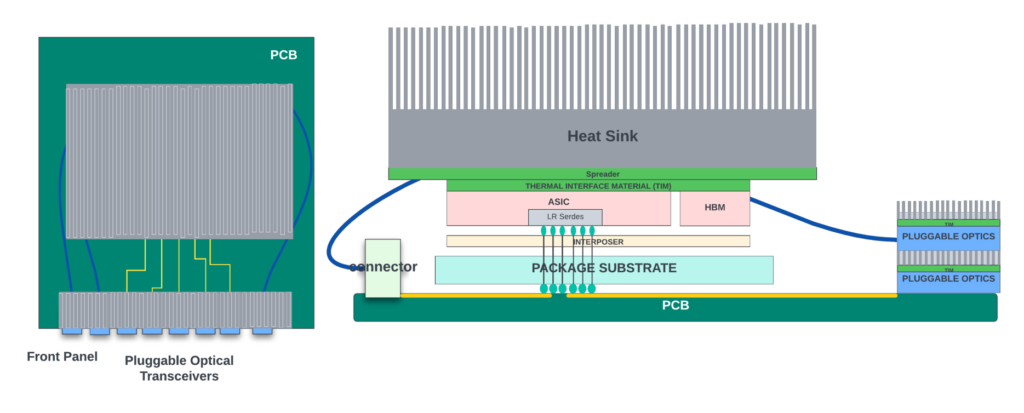

>散热片

热管理系统主要由散热器和风扇模块组成。散热器基本上由铜或铝等导热材料组成。它们直接位于芯片上方,与 ASIC 封装或无盖封装中的 ASIC 芯片本身直接接触,有助于将热量从芯片中散发出去。这些散热器的设计是为了最大化与ASIC的接触面积。

散热器也集成了顶部的均热板。均热板是一种由薄金属片制成的密封容器,里面装着少量工作流体,例如水或酒精。散热器将热量传递至均热板,这导致液体蒸发并变成蒸汽,然后蒸气移动到腔室的冷端,凝结成液体,将其吸收的热量释放到周围空气中。

液体被输送回腔室的加热端,在那里可以再次蒸发。通过将均热板集成到散热器中,可以显著提高散热器的散热能力。散热器表面有小而薄的矩形突出物,称为翅片。这些翅片平行排列,以增加散热器的表面积,有助于更快地散热。散热器是无源元件,不需要任何电源即可运行。

| 顶部附有散热器的 ASIC 概念图

网络ASIC不会在整个芯片区域均匀地耗散功率。有一些热点或功率密度非常高的区域。这是因为晶体管和存储器并不是均匀分布在整个芯片上,某些 IP/逻辑可以看到更高的晶体管活动(例如 SerDes 和数学密集型加密/解密逻辑)。热工程师使用软件来模拟存在这些热点的散热器性能,并提出散热器设计参数来处理这些它们。在某些情况下,这些 IP /逻辑的放置需要根据这些模拟的反馈在芯片平面中进行调整,以减轻热点效应。

>风扇模块

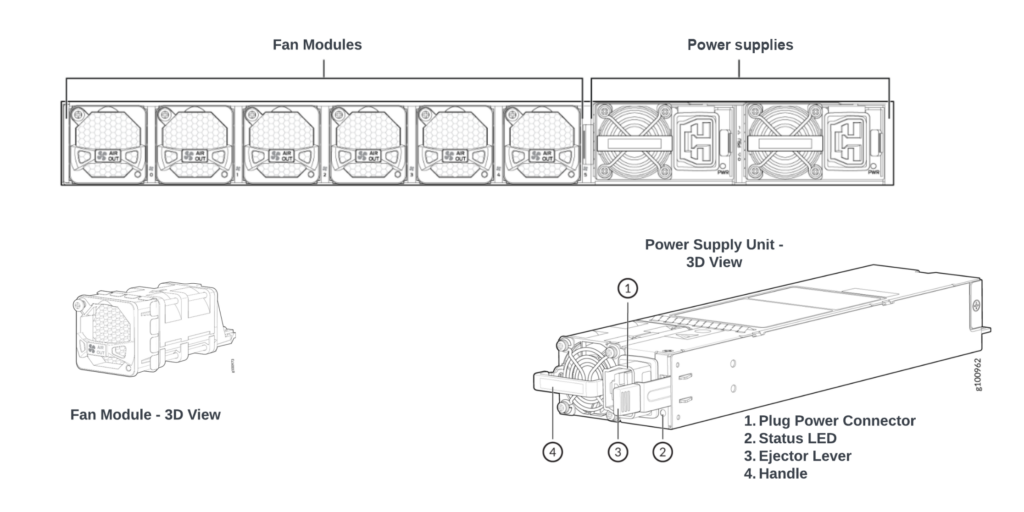

每个系统还包含多个风扇模块,用于排出产生的热量。当系统启动时,风扇开始旋转并产生空气流过机箱,冷却内部组件并排出热空气。风扇从机箱前部吸入冷空气,并通过后面板排出热空气。

风扇速度可根据内部组件的温度自动调节。温度传感器位于机箱的不同位置。网络 ASIC 和 CPU 还集成了热二极管,用于测量这些芯片的结温。如果组件的温度超过特定阈值,风扇将自动加速以提供额外的散热。为了使风扇有效工作,空气流动应畅通无阻。

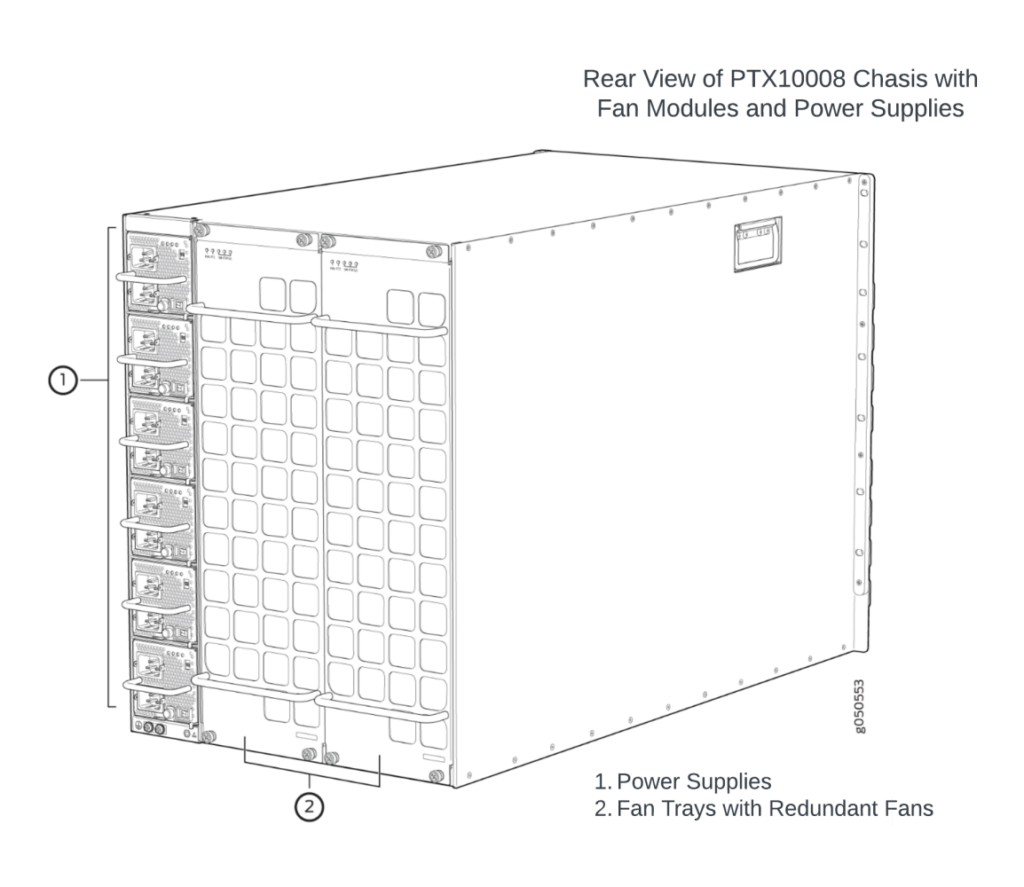

| 带有风扇模块和电源的独立路由器后面板

| 带有风扇和电源的模块化系统后面板

**液体冷却 ** (作为散热器/空气冷却的替代品)在消除高功率 ASIC 散发的大量热量方面更有效。在液体冷却中,液体冷却剂流过一系列与系统中的热部件直接接触的管道(闭环)。当液体吸收组件的热量时,它会变得更热。较热的液体流向散热器或热交换器,将热量散发到空气或其他冷却剂中。

然而,与空气冷却相比,液体冷却的前期成本更高,实施和维护起来也更昂贵、更复杂。并非所有电子元件都设计为与液体冷却系统一起使用,因为这就要求系统同时支持两种冷却模式,进一步增加了成本。

系统电源

>独立系统

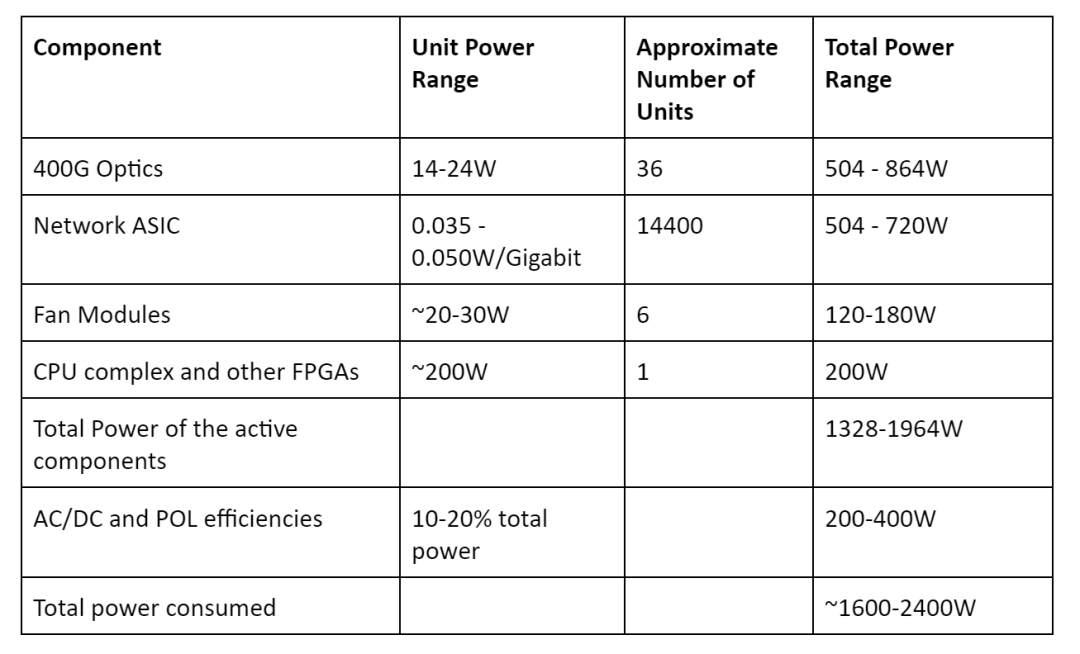

所有有源组件都贡献了系统消耗总功率的一部分,但他们之间的差异很大。为了了解功率故障,这里以一个具有14.4Tbps网络芯片和36 x 400G前面板端口的假设独立系统为例。每个组件的最小和最大功率通常在下表中列出的范围内。

| 网络 ASIC 占系统总功耗的很大一部分

从表中可以看出,网络 ASIC 的功耗占系统总功耗的很大一部分。一个典型的高端网络芯片在 7/5nm 工艺节点中可以获得 0.035 - 0.055W 的每 Gbps 功率。光学器件消耗的功率与网络 ASIC 相同或更高,具体取决于插入的光学模块的类型。AC/DC 和 POL 转换器的效率损失对总功率影响很大。如果为任何 WAN 端口添加重定时器和变速箱,也会增加功率。

请注意,系统消耗的总功耗在很大程度上取决于流量模式和网络端口上的总负载。但是,对于热电源设计,需要考虑最坏情况下的功耗。

>模块化系统

在模块化系统中,线卡中的网络 ASIC 可能比独立的对应器件消耗更多功率,因为它们可能需要通过高速 SerDes 接口向背板中的交换fabric卡发送/接收高达 100% 的流量。风扇模块和电源单元通常位于机箱背面,满足所有线卡和交换fabric卡的需求。交换fabric卡消耗的功耗在很大程度上取决于fabric交换芯片的设计。

基于单元的交换效率更高,需要的fabric交换机和高速接口数量更少。因此,对模块化机箱功率进行一般估计是很困难的。假设每个LC功率至少为2400W,16槽模块化系统中的16个线卡消耗高达38KW功率!各个组件之间的功率分配遵循与独立系统相同的趋势(ASIC 和光学器件消耗超过 60-70% 的系统功率)。

设计低功耗网络芯片

随着系统总吞吐量的增加,网络ASIC所占系统功率的比例也相应增加。网络芯片的高功耗面临着一些挑战。

能够高效地将电力传输至 ASIC,且在传输过程中不会出现重大损耗。

能够有效地散发 ASIC 产生的热量,使 ASIC 的结温保持在规格范围内。由于单芯片和多芯片封装内功能的大量集成,可能会产生高功率密度的热点,因此这一点变得越来越具有挑战性。

在下面的部分中,让我们看看网络芯片供应商用来降低功耗的不同技术。在引用 ASIC 功率时,我们经常使用“每千兆比特每秒功率”这个术语,因为绝对功率数可能会根据每个 ASIC 支持的总吞吐量(以 Gbps 为单位)而变化。

任何集成威廉希尔官方网站 消耗的功率都由三个主要部分组成:泄漏功率、有功功率和短路功率。

>泄露功率

泄漏功率是 ASIC 通电后、ASIC 内的任何时钟开始切换之前消耗的功率。即使晶体管没有开关,该功率也会由于流过晶体管的漏电流而消耗。

泄漏功率已成为使用先进工艺节点制造芯片中的一个重要问题。这是因为较小的晶体管具有较短的沟道长度和较薄的栅极氧化物,这可能导致较高的漏电流。随着晶体管尺寸的缩小,同一芯片区域中可以封装更多的晶体管,从而导致更多的漏电流。

漏电流还取决于晶体管的结构。FinFET晶体管结构(用于台积电7 nm和5nm工艺)比CMOS 结构具有更好的泄漏特性。台积电 3nm 工艺采用的全栅 (GAA) 晶体管架构提供了更严格的控制,因为栅极四面包围通道,并且电荷载流子泄漏的表面积较小,从而减少了泄漏电流。

泄漏功率是电源电压 (Vdd) 和泄漏电流的乘积,也就是说在较小的电源电压下可以降低泄漏功率,但当晶体管的阈值电压与电源电压之间的差值减小时,泄漏电流本身可能在较小的Vdd下增加。虽然漏电流略有增加,但电源电压的降低总体上降低了漏功率。然而过度降低电源电压可能会影响晶体管的性能。因此,在选择 ASIC 的工作电压时必须仔细权衡。

电源门控,其中电源电压在启动时被切断,用于未使用的逻辑部分(例如,如果某个功能可以针对某些网络应用被禁用),也可以消除通过未使用逻辑的泄漏电流。然而,这伴随着电压轨实施的额外复杂性,并且只有确保能明显节约的情况下才考虑。

>动态功率

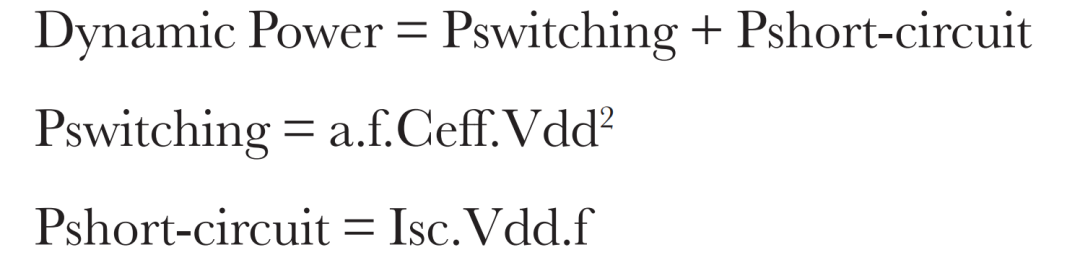

ASIC 的动态或有功功率由开关功率和短路功率组成。开关功率是芯片中的逻辑元件在开/关时消耗的功率。这是由于与晶体管和互连相关的电容的充电和放电造成的。该功率与晶体管和互连的电容 (Ceff)、逻辑元件的开关频率 (f) 以及电源电压 (Vdd) 的平方成正比。ASIC 的总开关功率是所有逻辑(组合门、触发器、模拟威廉希尔官方网站 和存储单元)开关功率的总和。

>短路功率

短路功耗是当数字威廉希尔官方网站 的输出从一种逻辑状态切换到另一种逻辑状态,并且 n 型和 p 型晶体管同时导通,从而为电流从电源到地创造了一条直接路径(Isc)而导致的功率损耗。短路功率是一种瞬态效应,仅在两个晶体管都导通的短暂时间间隔内发生。该间隔的持续时间取决于威廉希尔官方网站 的开关频率和供电电压水平。因此,该功率与电源电压 ( Vdd ) 和频率 ( f )成正比。仔细布局库元件可以减少晶体管之间的重叠并限制短路功率:

在降低功耗方面,主要关注的是降低动态功耗(因为在典型 IC 中动态功耗占总功耗的 75% 以上)。

降低动态功耗的方法包括降低时钟频率、总开关活动、互连和晶体管电容以及电源电压。所有这些都有各自的挑战和优缺点。让我们回顾一下这些功耗降低技术。

最佳电源电压 (Vdd) 选择

由于“平方”依赖性,降低工作电压会显著影响功率。二十年前,我们可以每两到三年将晶体管性能提高一倍,同时降低其运行所需的工作电压 (Vdd)。例如,180nm 工艺节点的典型电源电压约为 2.5V,而在 45nm 工艺节点则降至约 1.1V。在 14 nm工艺节点中,该电压进一步降至约 0.90V。

但是,随着转换器尺寸的缩小,要在不影响晶体管性能的情况下显著降低每一个新的处理节点的供电电压变得越来越困难。因此,从 7nm 工艺节点开始,工作电压的改进几乎停止了,工作电压徘徊在 0.75V - 0.85V 之间。大多数硅代工厂为每个电压轨提供一个范围)。

一些代工厂提供电压分级(voltage binning),根据芯片的工艺节点(快与慢),可以调整工作电压。快角的芯片具有更快的晶体管。我们可以利用这一点,降低工艺角落芯片的电源电压,使其在不降低性能的情况下消耗更少的功率。不过这需要制造商的支持,根据工艺特性对 ASIC 芯片进行分类。

工作频率选择

降低操作频率很显然是会降低功耗的,但同时它也会降低性能,因为 ASIC 无法足够快地处理数据包并通过现有数据路径移动它们。然后,为了从网络系统获得相同的总体吞吐量,我们必须在 ASIC 内部添加更多逻辑,或在线卡/系统中添加更多 ASIC。两者都会增加系统的总功率/成本。

具有每秒数十太比特带宽的高端网络芯片通常具有数据包处理单元和数据路径。数据包处理单元可以在固定管道架构中实现,也可以运行到完成架构中实现。

假设在固定管道架构中,一个数据包处理管道每个周期可以接收一个数据包。在 1.25GHz 时钟频率下,这相当于每秒 12.5 亿个数据包。如果我们希望将下一代处理管道的性能提高到每秒 14 亿个数据包,显而易见的选择是将时钟频率提高到 1.4GHz。在这个更高的时钟频率下,管道中的每个阶段都必须在更短的时间内完成相同数量的处理。

如果我们切换到下一代 ASIC 的新处理节点,预计逻辑速度至少会提高 20-30%。如果我们想保持 1.25GHz 频率以降低功耗怎么办?在这种情况下,要每秒获取 14 亿个数据包,管道每个周期需要处理 1.12 个数据包。这很难实现,因为它不是一个整数值。在这种情况下,设计人员倾向于将逻辑过度设计为每个周期处理2个数据包。这样做将需要几乎双倍的逻辑量,这将占用更多的芯片面积和功耗。

类似地,在数据路径内部,如果频率降低以获得相同的千兆/秒性能,则需要加宽在芯片内部承载数据包数据的总线(往返于 WAN 端口到中央缓冲区和其他结构),以便在每个周期承载更多的比特。当总线加宽时,会增加顶层的拥塞,需要通过提供更多的布线区域来缓解,从而增加芯片的尺寸。

内部存储器 (SRAM) 在频率决策中也发挥着关键作用。SRAM 性能可能不会随着频率的提高而扩展,因此为了实现逻辑存储器,我们将被迫使用多个堆叠在一起的较小 SRAM 结构,这增加了额外的开销和SRAM访问时间。在决定操作频率时,需要在多个不同的频率下对片上缓冲区和数据库、它们到库中的SRAM的映射以及每个逻辑内存如何分片进行详细分析。

ASIC 调度和 IP(实现特定功能的模块)重用也在频率选择中发挥作用。在某些情况下,重用现有IP以加快周转是非常可取的。在这种情况下,我们受到现有IP在没有任何设计更改的情况下可以运行的最大频率的限制。

因此,频率选择涉及到最佳功率、性能和面积设计点的多重权衡。在一个芯片中看到多个时钟域的情况并不少见,其中不同的子系统可以使用不同的频率进行计时。它增加了时钟树结构的复杂性,并增加了设计和验证时间,但与对 ASIC 的所有功能使用相同的频率相比,它可以提供更好的设计点。

减少开关活动

如前所述,ASIC 中的逻辑门和触发器在其输出改变状态时会消耗开关功率。关键的是要确保如果触发器的输出没有在特定的时钟周期中使用,它就不应该在该周期中切换。这可以通过时钟门控来实现,即在不使用触发器输出的周期中移除(或门控)触发器的时钟,因此触发器输出保持与前一个周期相同的状态。通过这样做,由该触发器提供的所有组合逻辑的切换也会减少,这被称为动态时钟门控。

当设计者以特定格式编写触发器的代码时,EDA工具在合成(将Verilog行为RTL代码转换为门)期间推断出动态时钟门控。但采用这种方法的时钟门控效率在很大程度上取决于设计者在识别所有时钟门控机会方面的专业知识。有一些功能强大的 EDA 工具可以识别设计中的所有时钟门控机会,有些甚至可以在 RTL 中自行进行时钟门控。使用先进的 EDA 工具,网络芯片的动态时钟门控效率可达到 98% 以上。

此外,某些功能/IP 可以进行静态时钟门控。例如,如果网络芯片提供集成的 MACsec,并且如果某些应用程序/客户不需要此功能,则整个模块可以从启动时间开始进行时钟门控。

工艺/技术节点选择

制造ASIC的半导体工艺在整体功耗中也起着关键作用。在十年之前,每个新的工艺节点都可以在相同的面积内封装双倍数量的晶体管,并获得比以前的工艺节点双倍或更高的功率效率。

过去几年这一趋势有所放缓。例如,当从 5nm 工艺节点转向 3nm 工艺节点时,功耗仅提高了 30%(对于相同的性能)或 1.42 倍。大部分的改进来自逻辑,而存储能力的改进微乎其微。这意味着即使我们可以通过从 5nm 升级到 3nm,将 ASIC 封装内的吞吐量提高一倍,也会多消耗 42% 的功耗。当网络系统的容量翻倍时,硬件工程师需要为 ASIC 的额外功耗做好预算。

随着工艺节点的缩小,制造变得更加复杂并且需要更高的精度。这可能导致设备和生产成本增加。由于更小的特征尺寸和更高的晶体管密度,成品率也会降低。这导致客户的每芯片成本增加,而且为新工艺节点开发 SerDes 和其他 IP 的成本可能会很高。此外,在较小的工艺节点上构建芯片通常需要使用更先进和更昂贵的材料,这会增加生产成本。

总的来说,与7nm芯片相比,5/3nm芯片的制造成本更高。但是,如果我们可以用下一代工艺节点将ASIC封装内的密度提高一倍,而不会使功率增加一倍,那么它仍然可以节省系统的整体成本(因为系统中其他组件的成本,如机箱硬件、CPU复合体、PCB板、热管理等,并不总是增加一倍)。因此,在决定过程节点时必须考虑整体系统成本和功率效率。

高能效数据路径/处理架构

正如在前一节中所看到的,在增加ASIC和系统的吞吐量时,仅改进工艺节点是不足以降低功耗的。高能效ASIC架构在降低网络ASIC整体功耗方面也起着重要作用。

网络 ASIC 架构随着时间的推移不断发展,以解决以下限制:

SRAM 的面积/功耗没有像新工艺节点上的逻辑那样扩展。

尽管晶体管密度不断提高,但新工艺节点的功耗并没有多大改善。

外部存储器的扩展速度也不够快,无法跟上逻辑扩展的速度。在这方面,虽然 HBM(ASIC 封装内的高带宽内存)供应商通过使用新的内存节点、堆叠更多芯片以及提高HBM和ASIC芯片之间的数据传输速率,大约每 3 年将这些内存的性能和密度提高一倍。但每个 HBM 部件提供的带宽远不及网络芯片所支持的数据吞吐量。

例如,每个 HBM3P部件理论上可以提供 8Tbps 的原始总数据速率。由于读/写周转和其他瓶颈导致总线效率损失 20%,这足以缓冲 3.2Tbps 的无线接入网络 (WAN) 流量。高端网络芯片供应商希望在每个 ASIC 封装中封装 >14.4Tbps。显然,并非所有流量都可以使用单个 HBM 部件进行缓冲。添加更多 HBM 部件可能会占用 WAN 端口所需的芯片边缘区域。

这意味着简单通过将数据路径切片加倍来使下一代 ASIC 吞吐量加倍的方式是不可行的。对片上和外部存储器的访问需要尽可能地优化。为了实现这一目标,网络供应商使用了各种技术:

# 具有浅片上延迟带宽缓冲器的超额订阅外部延迟带宽缓冲器

在这种架构中,数据包首先在片上缓冲区中排队,只有拥塞的队列才会移动到外部存储器。随着拥塞减少,这些队列移回到片上缓冲区。这减少了总体数据移动以及与之相关的功耗。

# 虚拟输出队列 (VOQ) 架构

在这里,所有延迟带宽缓冲都在入口数据包转发实体 (PFE) 或切片中完成。数据包在入口 PFE 的虚拟输出队列中排队。VOQ 唯一对应于数据包需要离开的最终 PFE/输出链路/输出队列。数据包通过出口处的复杂调度程序从入口 PFE 移动到出口 PFE,仅当它可以将数据包调度出其输出链路时,该调度程序才会从入口 PFE 提取数据包。与组合输入和输出队列 (CIOQ) 架构相比,VOQ 架构中的数据移动较少。这会导致开关功率降低。

# 固定管道数据包处理

处理网络协议标头时,在专用硬件中对解析/查找和标头修改进行硬编码可以实现高效的实现,从而节省数据包处理过程中的面积和功耗。为了获得面积/功耗优势,所有高端网络供应商都已转向固定管道处理。

# 共享数据结构

当在一个芯片中集成多个 PFE 或切片时,一些网络芯片供应商共享大型数据结构,这些数据结构在这些切片上保存路由表 (FIB) 和其他结构。这样做会增加对这些共享结构的访问次数。但是,在大多数情况下,这些大型逻辑结构是使用许多离散的 SRAM 组来实现的,并且访问可以在客户端和组之间静态复用。由于内存控制逻辑需要适应的热存储和无序读取返回,这可能导致访问时间不确定。通常,面积/功耗优势超过了控制逻辑的复杂性。

但是,当将数据结构移动到集中位置时,往返于集中内存的路由所消耗的功率有时可能超过内存访问功率。因此,架构师在共享数据结构时需要考虑权衡。

# 高速缓存(Cache)

高速缓存的层次结构可用于减少对具有时间或空间局部性的共享结构(片上或外部存储器)的访问。这减少了长电线上的数据移动,从而减少了功耗。

# 布隆过滤器

这是一种流行的方法,用于减少对驻留在外部内存中的哈希表或查找表的访问次数。布隆过滤器是一种节省空间的概率数据结构,用于测试元素是否是集合的成员。该数据结构通常保存在片上 SRAM 中。探测布隆过滤器中的“键”可以指示它是否存在于片外表中。使用这种方法可以将某些网络功能对中央和片外存储器的访问减少 70-80%。

# 压缩数据结构

某些数据结构可以被压缩和存储,以减少读取这些结构时的内存占用和切换功率。

# 系统级封装 (SiP) 与小芯片的集成

在过去的三到四年里,小芯片设计的发展势头迅猛,多个小芯片(ASIC核心)可以集成在一个具有低功耗芯片接口的封装中,如UCIE或短距离serdes(XSR)。

# 功能蠕变

最后,功耗与芯片设计以线速处理的功能数量成比例增加。一些可能不需要线速处理的功能可以转移到CPU复合体中,由软件来处理,以节省面积/功耗。这些网络通常具有较大的最大传输单元 (MTU),即可以在网络上发送的最大数据包大小。因此,核心网中很少需要对数据包进行分段。在这些情况下,网络芯片不需要在线实现此功能。然而,芯片应该检测到需要分段或重组的数据包,并将它们发送到 CPU 复合体进行处理。

同样,通过仔细分析用例和对利基功能使用替代方法来最大限度地减少功能蠕变对于降低功耗至关重要。

微架构注意事项

如果芯片模块没有采用高效的微架构,那么高效架构所提供的部分或全部节能优势就会丧失。块微架构在很大程度上取决于设计者的专业知识。以下是需要关注的部分:

# 过度流水线

添加比实现功能所需的更多的流水线阶段。

# SRAM 选择不当

单端口 SRAM 在功耗/面积方面比两个或双端口 SRAM 更高效。需要正确规划 SRAM 访问以选择正确的 SRAM 类型。类似地,使用算法存储器增加某些数据结构的端口数量以进行同时访问确实有助于降低面积/功耗。

# 没有优化逻辑内存以提高功耗

SRAM 库供应商通常提供内存编译器,让用户输入逻辑内存尺寸,编译器会为该内存提供不同的内存/平铺选项。这些编译器可以根据用户提供的权重在总体面积和功率之间取得平衡。

# 过度缓冲

一些设计倾向于在处理过程中多次缓冲数据/控制逻辑。而且缓冲区往往会被过度设计。需要详细检查缓冲区及其大小,以移除填充。

# 设计重用

设计重用有时可能会造成伤害。虽然重用有利于项目进度,但这些设计可能没有最佳的微架构或实现技术来节省电力。

物理设计考虑因素

在过去的十年里,用于芯片/模块布局规划和布局的EDA工具在优化网表和布局以降低功耗方面取得了长足的进步。这些工具通过物理设计感知 RTL 综合、优化数据移动的 P&R、位置感知时钟门控、回收非关键路径上的功率等来降低功耗。

这些工具可以接受用户输入的各种流量场景,并优化物理设计以降低峰值功率。利用 EDA 工具的进步进行物理设计可以比通过前面提到的其他技术实现的动态功耗额外降低 4-5%。

EDA 工具还支持功率门控、动态电压/频率降低或多电压/频率岛方法,并在RTL合成和物理设计阶段为实现这些技术提供自动化和检查。

电源监控

虽然提高能效对于高端 ASIC 来说是一件好事,但如果没有可量化的目标,它可能会导致架构和实施方面的各种变化,从而增加进度延迟和投片后问题的风险。必须与硬件和产品管理团队合作,为 ASIC 定义功率目标(每 Gbps 功率),并在整个开发阶段持续估计和监控功率,以保持正常运行。

在架构阶段,功耗估算通常使用基本技术来完成,例如从先前的设计进行推断以及使用新工艺节点的扩展。在设计实现阶段,多种 EDA 工具可以随着设计通过 RTL 和 P&R 的进展来估计和监控功耗,为工程师提供节能机会的选择和建议。

光学新趋势

在OFC 2023会议上,多家供应商展示了用于数据中心和企业应用的线性驱动(或直接驱动)非 DSP 可插拔短/中程光模块的原型系统。这些光模块没有耗电的 DSP 威廉希尔官方网站 ,并使用线性放大器来转换电信号和光信号。

这与传统的相干收发器形成鲜明对比,传统的相干收发器使用 DSP 和相位调制器进行这种转换。这些系统依赖于网络 ASIC 内部的长距离 (LR) SerDes 功能强大,以弥补光学器件内部 DSP 的不足。

线性驱动光模块非常节能,一些供应商声称与传统光收发器相比,节能高达 25%。在 800Gbps/1.6Tbps 速度下,使用线性驱动光学器件可以显著降低系统成本和功耗。

写在最后

尽管本文主要关注用于降低网络芯片和光学器件功耗的趋势和技术,但考虑每个新系统设计中所有系统组件的功耗以及冷却和热管理解决方案的效率同样重要。

例如,即使是AC/DC转换器效率的微小改进,也可以在高功率系统中显著节省功率。尽管最初的前期成本很高,但在每秒处理数百兆比特的模块化系统的生命周期内,投资液体冷却也可以显著节省成本。

随着ASIC架构师的优化选择用尽,技术节点的节能开始减少,探索降低系统功耗和冷却成本的替代解决方案至关重要。让我们继续推动 ASIC 内外的创新,使网络系统更高效,更具成本效益。

审核编辑:刘清

-

高端路由器供电系统的设计2008-09-10 0

-

低端路由器和高端路由的区别2010-06-26 0

-

路由器分类2017-06-15 0

-

路由器测试的类型和方法2018-12-12 0

-

设计高端路由器需要考虑哪些问题?2021-05-27 0

-

路由器的种类2022-03-17 0

-

快速路由器的路由查找和流分类算法研究2009-03-08 463

-

路由器原理及路由协议2009-08-01 831

-

路由器,路由器原理,路由器协议,路由器算法2010-03-29 1394

-

什么是软件路由器/高端路由器2010-04-03 684

-

小米路由器HD怎么样?小米路由器HD拆解图2017-05-05 20176

-

智能路由器和普通路由器的区别2018-01-04 1643

-

高端路由器和低端路由器有哪些区别呢?2023-12-27 1104

-

千兆路由器和百兆路由器的区别 万兆路由器有什么好处?2024-01-29 2183

全部0条评论

快来发表一下你的评论吧 !