基于FPGA的MicroBlade串口设计

电子说

描述

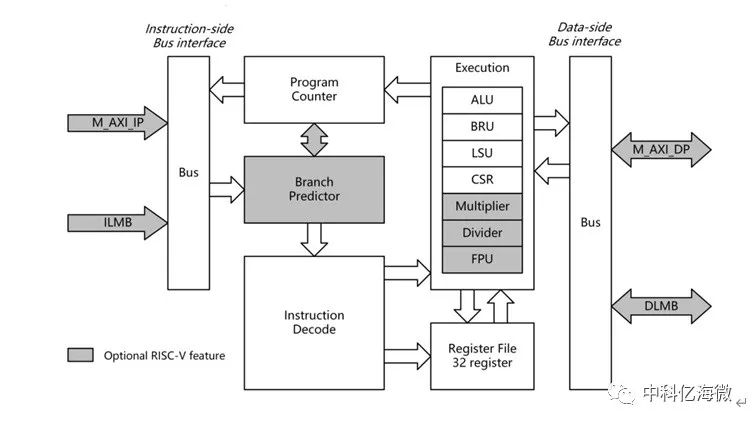

MicroBlade 处理器软核 IP是实现基于 RISC-V(Reduced Instruction Set Computer,精简指令集计算机)指令集架构的 32 位处理器软核,支持 RV32IM 指令集,支持 AXI4-Lite 接口,用于简化 FPGA 中复杂的控制逻辑。

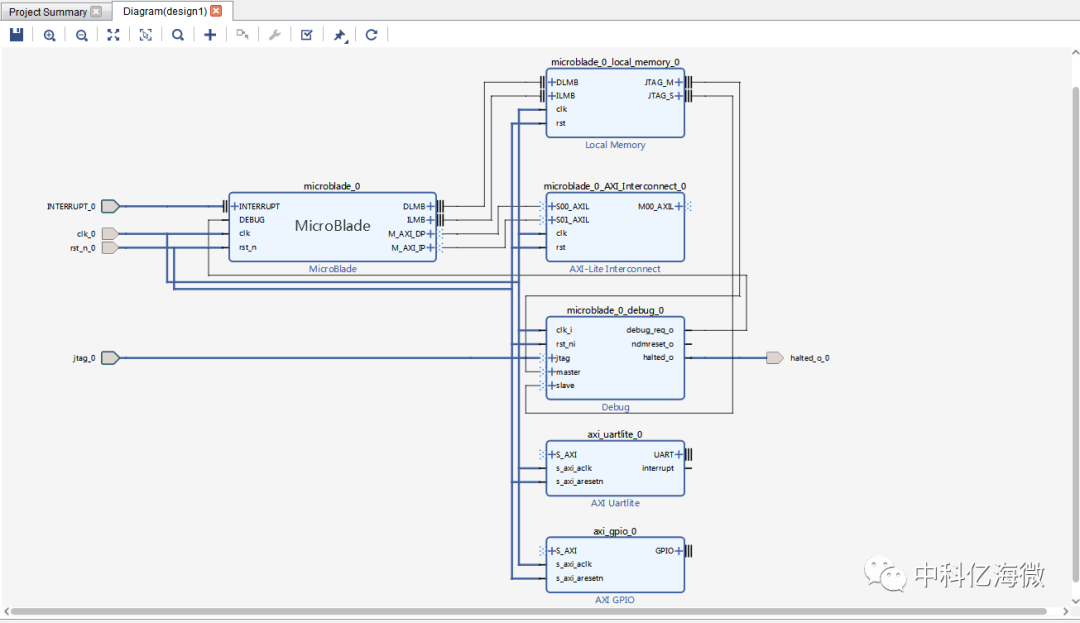

MicroBlade 处理器软核框架如下图所示:

MicroBlade 串口设计,开发板实现使用的是亿海神针系列EQ6HL45型FPGA。

本篇通过原理图设计,学习MicroBlade基本结构,通过创建简单的MicroBlade工程,实现MicroBlade调用AXI Uartlite模块和AXI GPIO模块,完成串口打印功能,掌握在模块化设计中,MicroBlade最小系统的组成,学会导出、建立以及运行基于SDK的工程。获取本篇相关源工程代码,可在公众号内回复“MicroBlade串口设计源工程”,提供下载路径。

设计原理

本系统中的MicroBlade模块通过AXI Lite总线与AXI Uartlite IP和AXI GPIO IP进行通信,完成led指示灯的状态改变以及串口打印功能。

操作步骤

基于GUI界面创建工程

1创建新的工程项目

1)双击桌面图标打开eLinx3.0;

2)点击Create Project,或者单击File>New Project创建工程文件;

3)将新的工程项目命名TEST_MICROBLADE,选择工程保存路径,勾选Create project subdirectory,创建一个新的工程文件夹,点击Next继续;

4)选择新建一个RTL工程,由于本工程无需创建源文件,故将Do not specify sources at this time(不指定添加源文件)勾选上。点击 Next继续;

5)选择目标FPGA器件:

Family:eHiChip6

Package:CSG324

Available devices: EQ6HL45

6)最后在新工程总结中,检查工程创建是否有误。没有问题,则点击Finish,完成新工程的创建。

2创建原理图,添加IP,进行原理图设计

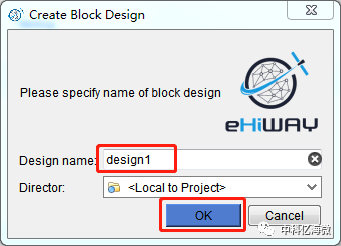

1)在Flow Navigator下,展开IP INTEGRATOR,选择Create Block Design创建新的原理图设计;

2)将新的设计命名为design1;

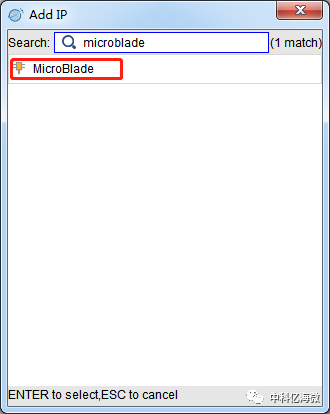

3)在Diagram中添加MicroBlade IP;

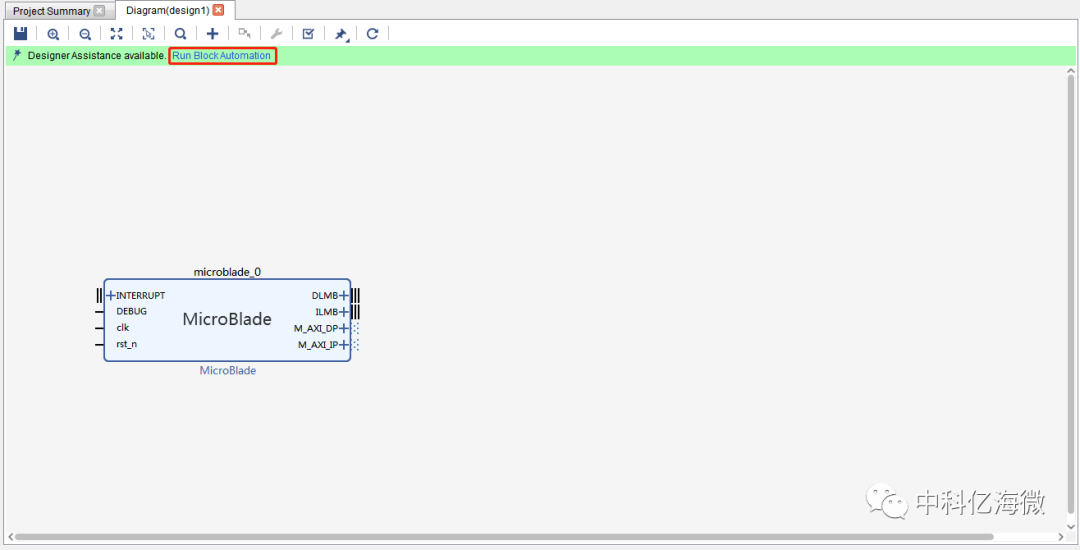

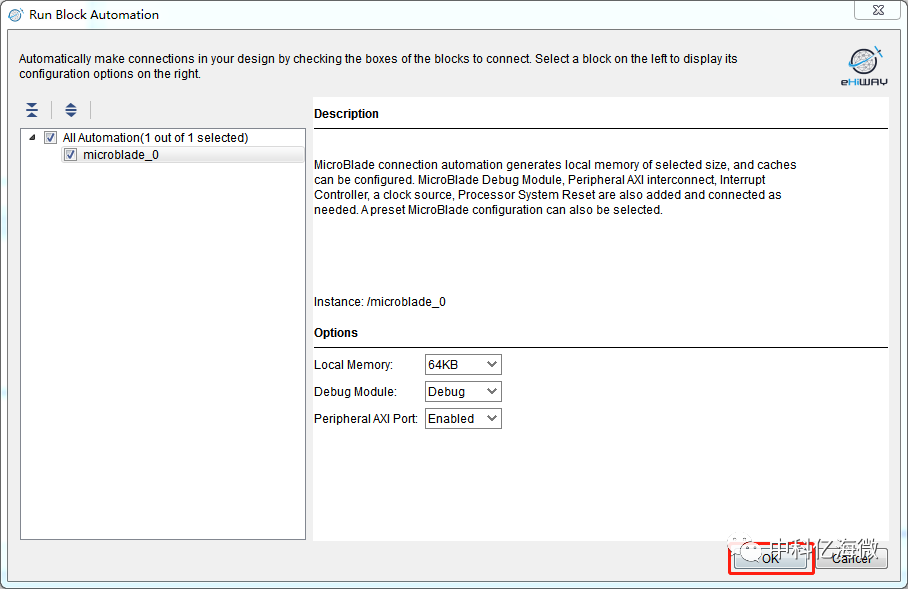

4)添加完成后如下图所示,点击Run Block Automation;

在弹出窗口中,使用以下设置替换默认设置:

Local Memory: 64KB

Debug Module: Debug

Peripheral AXI Port: Enabled

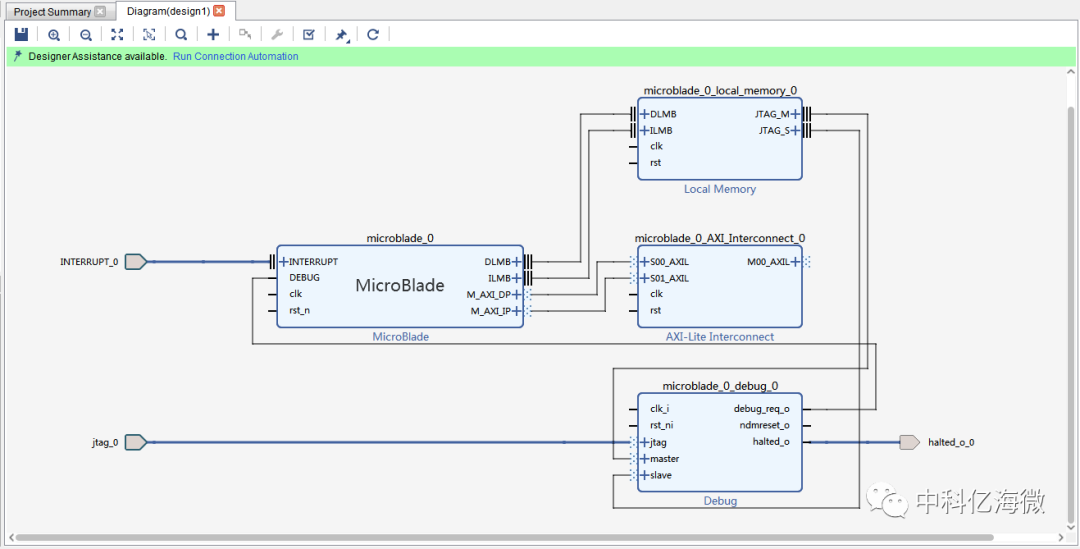

6)完成之后,eLinx会基于之前的设置自动生成一些额外的IP,并且会自动连接完毕,此时不要点击Run Connection Automation;

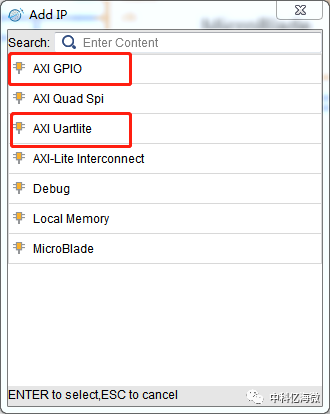

7)在Diagram中添加AXI Uartlite IP和AXI GPIO IP;

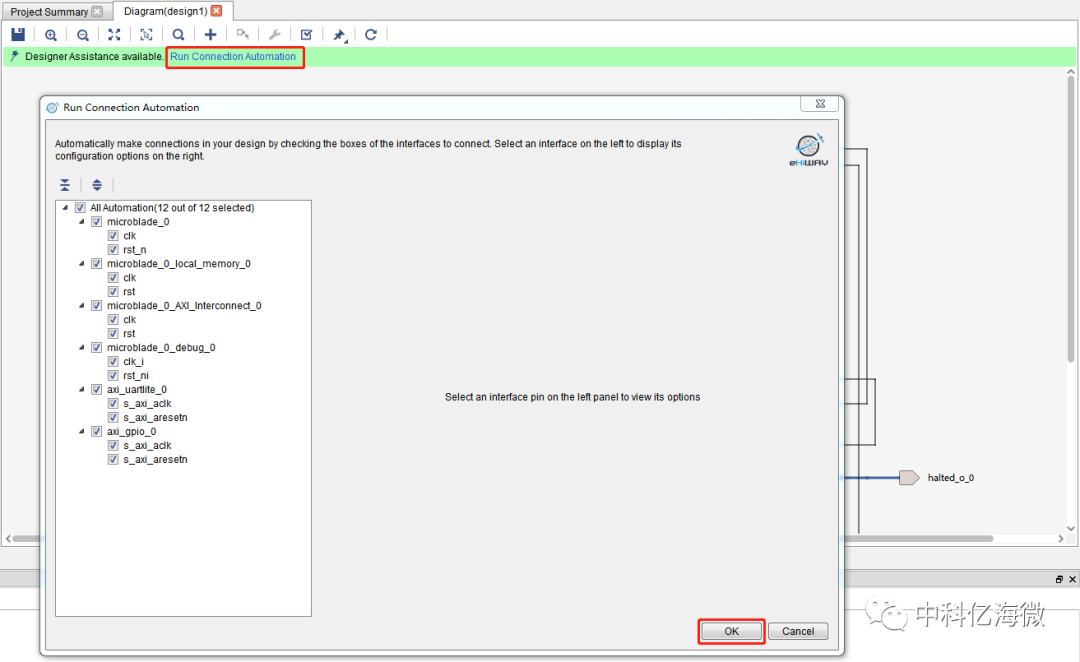

8)完成后,点击Run Connection Automation,在弹出窗口中勾选所有端口,点击OK继续;

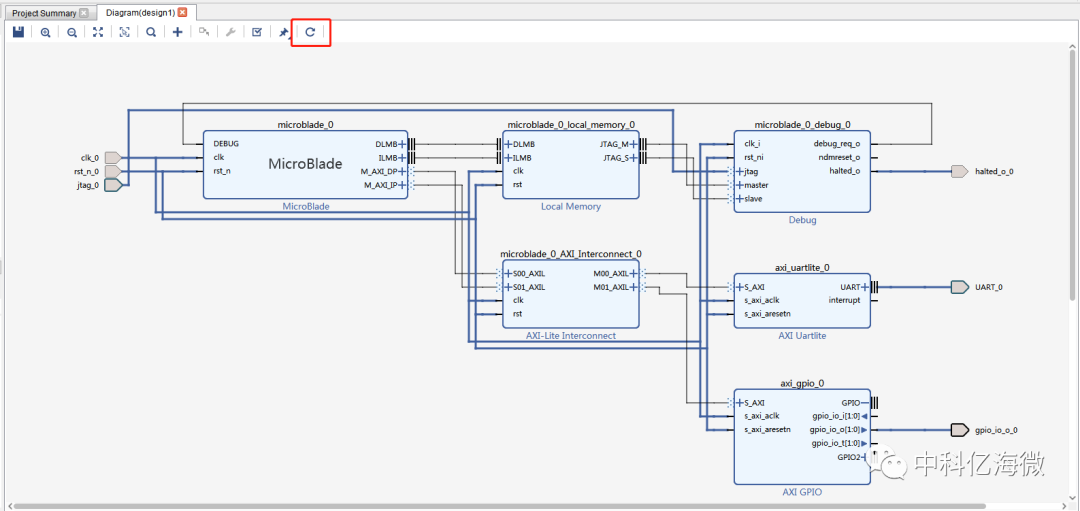

9)完成后,双击MicroBlade IP,打开界面,取消勾选Enable Interrupt隐藏Interrupt端口;

10)双击AXI_Lite Interconnect IP,打开界面,把master端口的数量修改为2。手动完成AXI_Lite Interconnect IP与AXI Uartlite IP,与AXI GPIO IP的连线;

11)双击AXI Uartlite IP,打开界面,把AXI CLK Frequency修改为50(板卡晶振为50M)。单击UART端口,引出外设IO;

12)双击AXI GPIO IP,打开界面,把GPIO通道GPIO Width修改为2,勾选Enable Dual Channel,把GPIO2通道GPIO Width修改为1。点击展开GPIO端口,点击gpio_io_o端口,引出外设IO;

13)完成后,点击布局重置按钮重新布局,如下图所示:

14)Ctrl+S保存设计。

3综合、实现、生成比特流文件

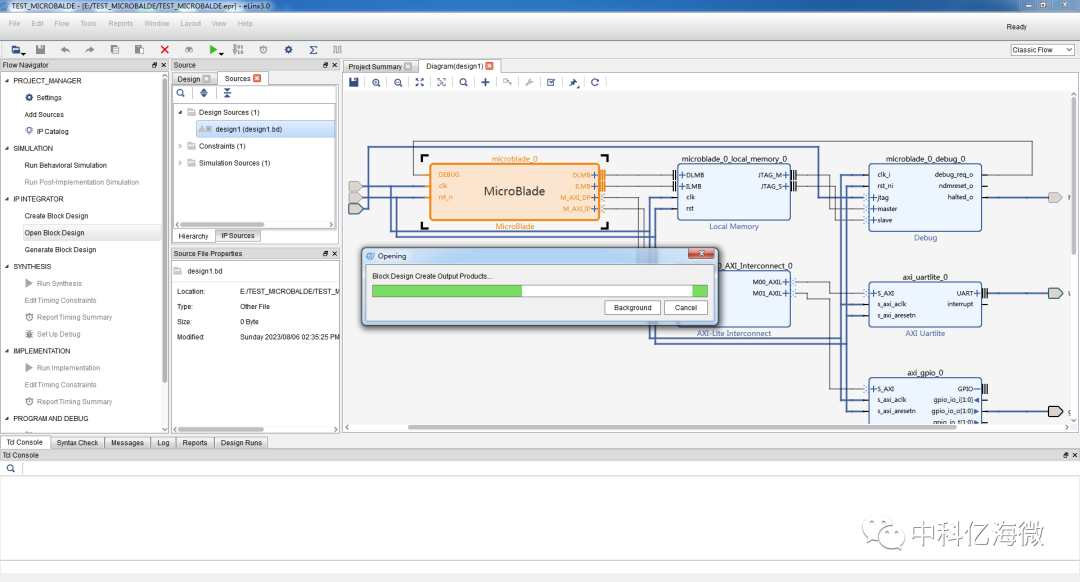

1)保存后,在Sources窗格中鼠标右键design1,选择Generate Output Products...,开始BD工程综合,如下图所示:

2)在Sources窗格中BD文件点击右键,选择Create HDL Wrapper,自动更新Sources列表,同时工程没有顶层,则自动设置为顶层;

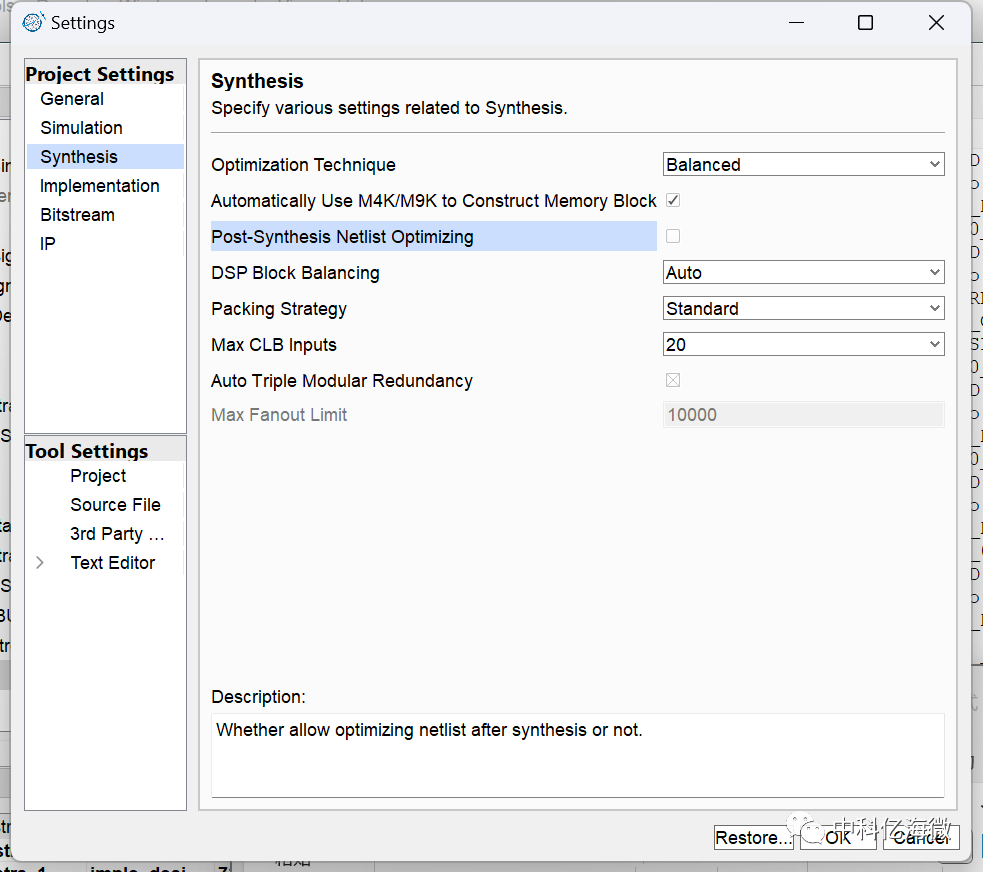

3)在界面上方工具栏中,选择Toos>Settings…在弹出的界面中点击Synthesis栏,取消勾选Post_Synthesis Netlist Optimizing;

4)完成后继续点击Flow Navigator中的SYNTHESIS栏中的Run Synthesis进行工程综合;

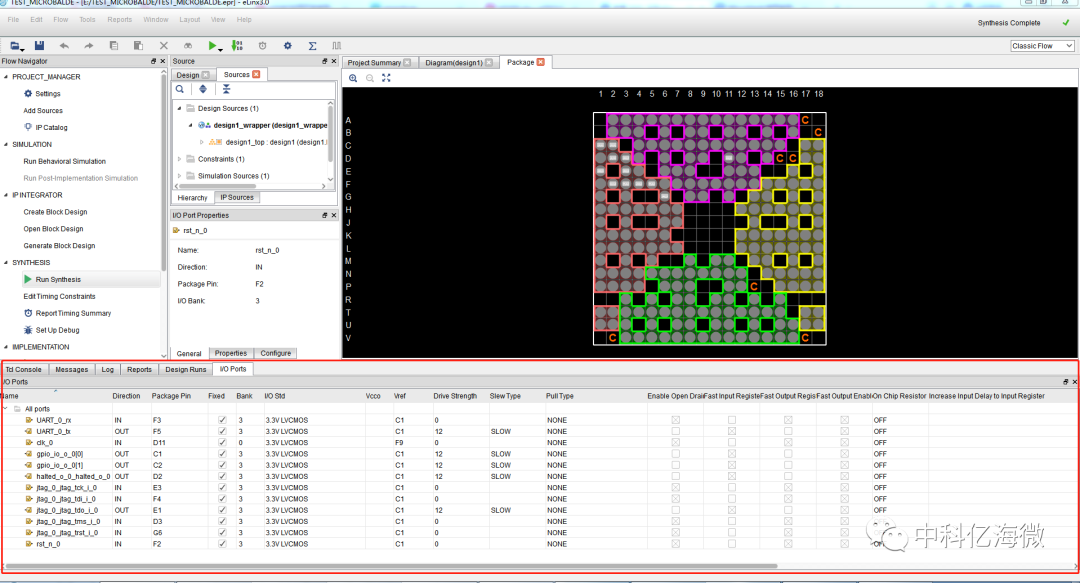

5)综合结束后在界面上方工具栏中,选择Toos >I/O Planning编辑管脚指定;

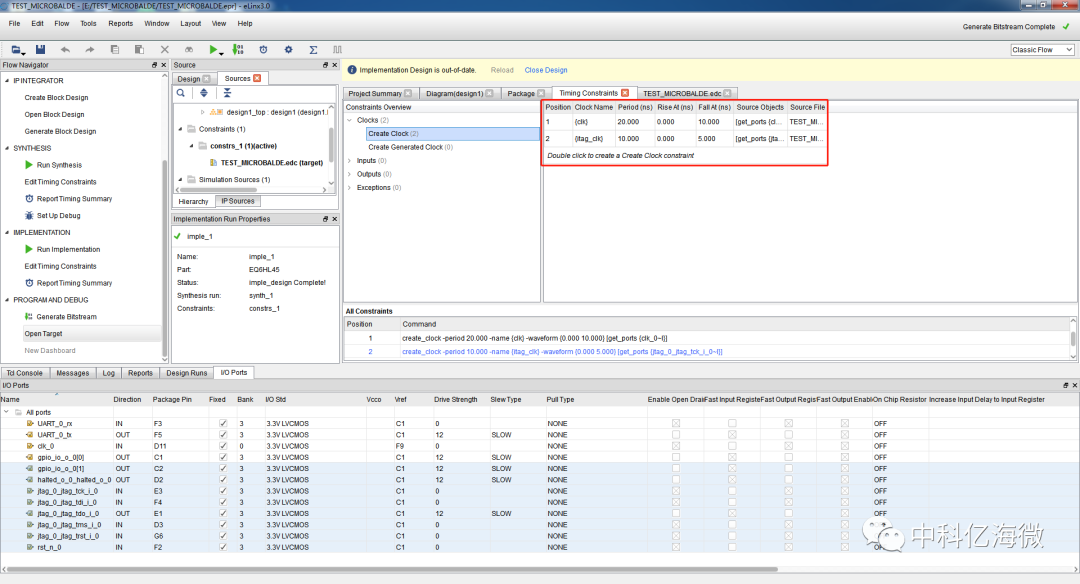

6)完成后在SYNTHESIS栏中点击Edit Timing Constraints添加2个时序约束后保存;

7)完成后继续点击左侧Run Implemenation按钮进行布局布线编译实现;

8)在PROGRAM AND DEBUG栏点击Generate Bitstream。连接开发板,完成后点击Open target启动Programmer下载码流。下载成功后默认状态为led1和led2交替闪烁。

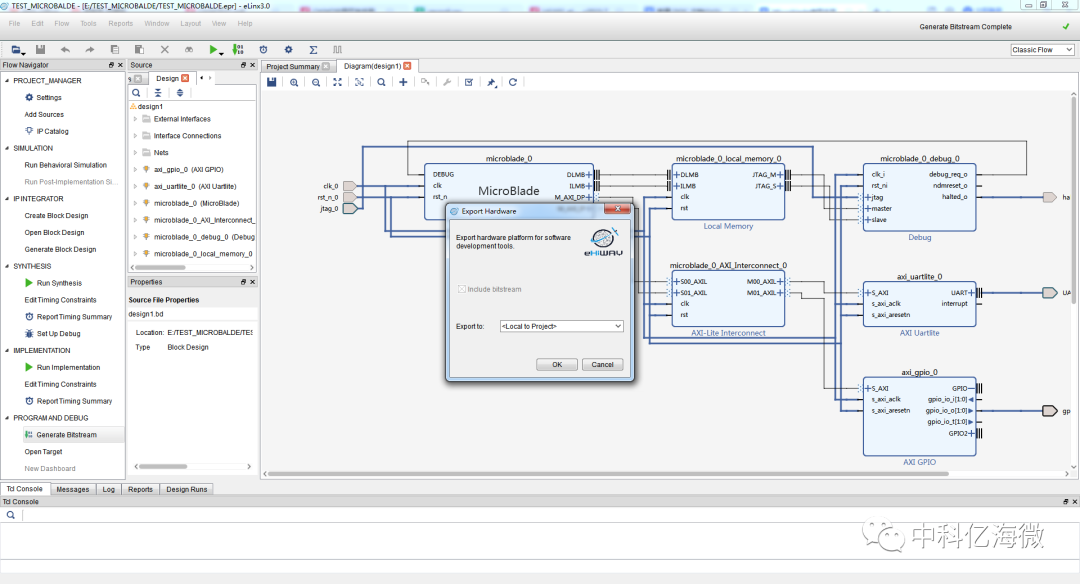

4导出SDK并启动

1)在顶部工具栏中,选择File>Export>Export Hardware导出硬件工程到SDK;

2)在工具栏中,选择File>Launch SDK,使用默认工程,启动SDK;

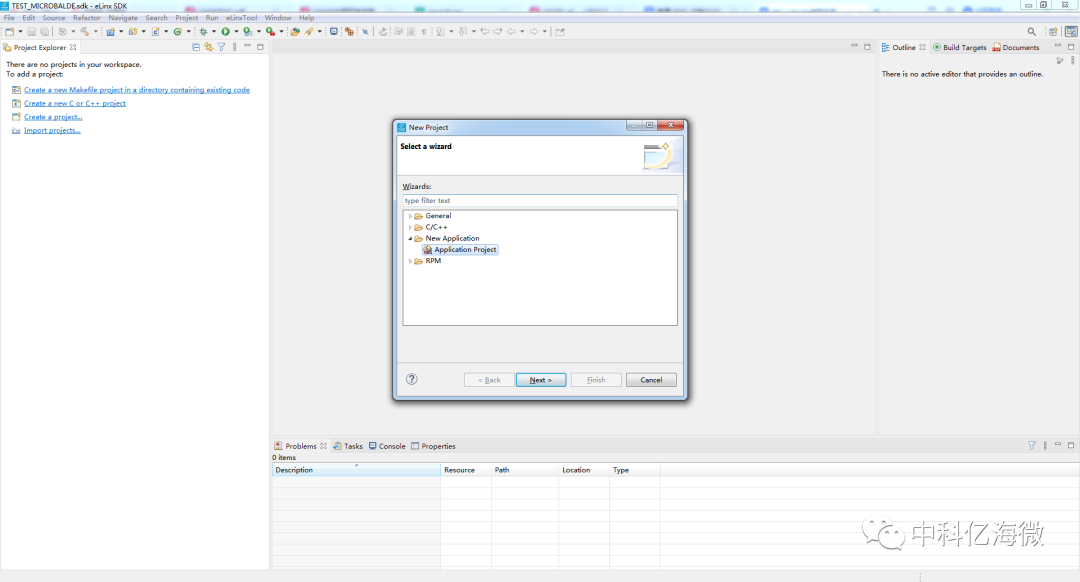

3)启动SDK后,如下界面,点击Create a project,弹出如下界面:

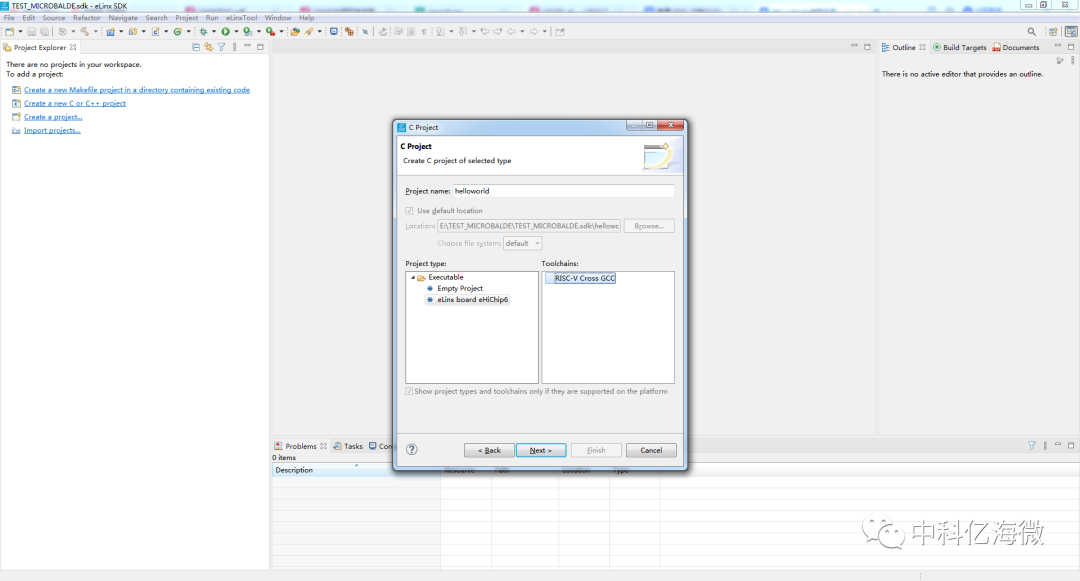

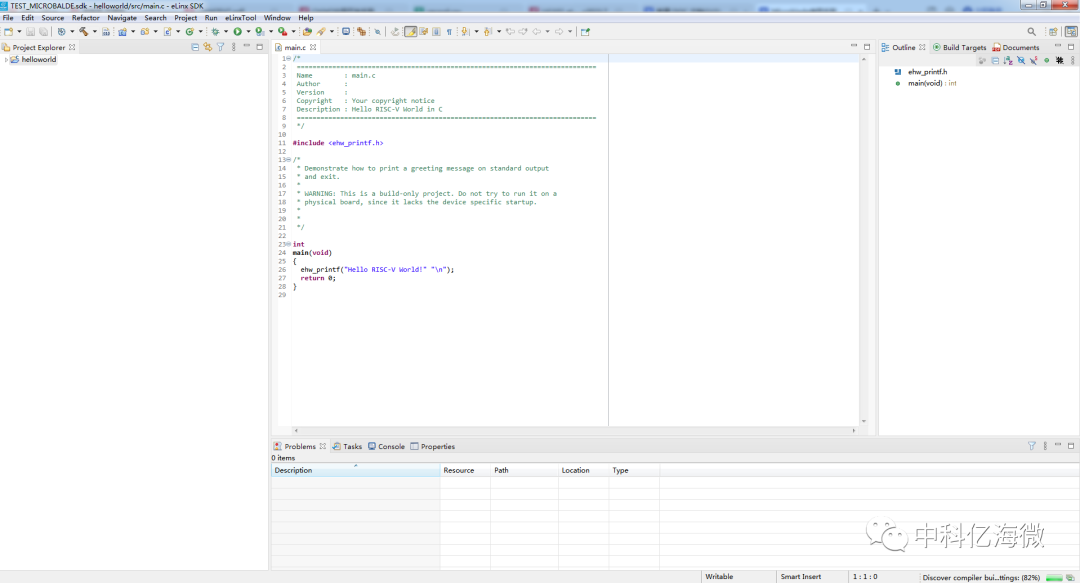

4)选择New Application->Application project,输入工程名helloworld,依次默认配置点击Finish完成创建;

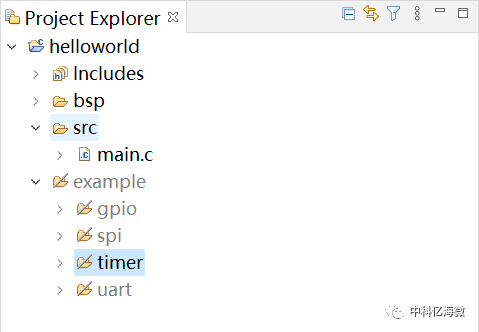

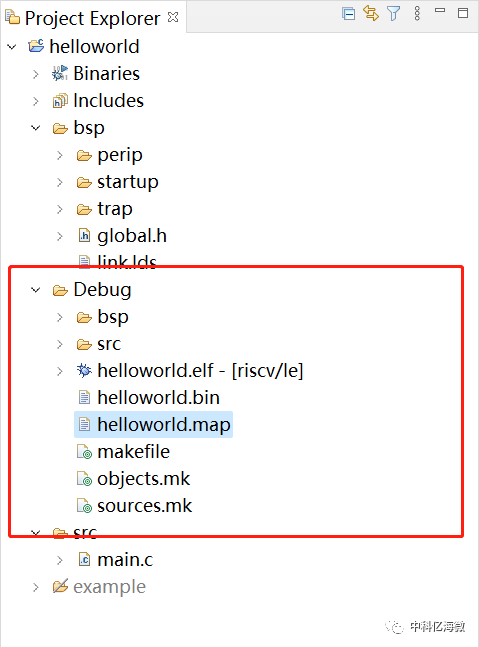

5)工程属性无需配置,工程中集成了例程,如下图:

6)构建。构建成功后左侧生成Debug文件夹

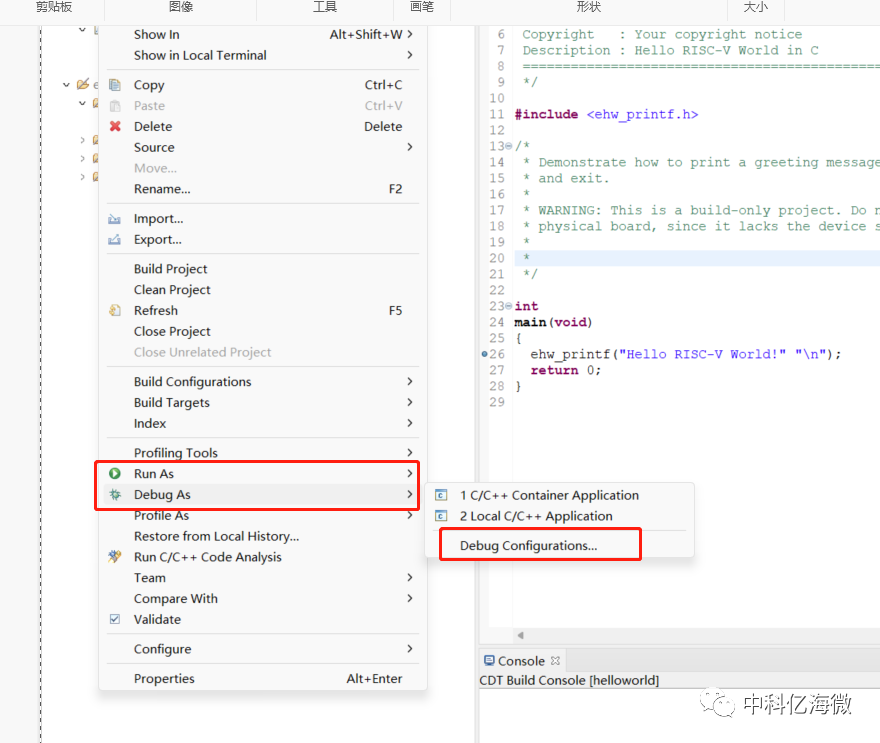

7)进行上板运行

a)在工程名称上点击右键,弹出界面选择run as

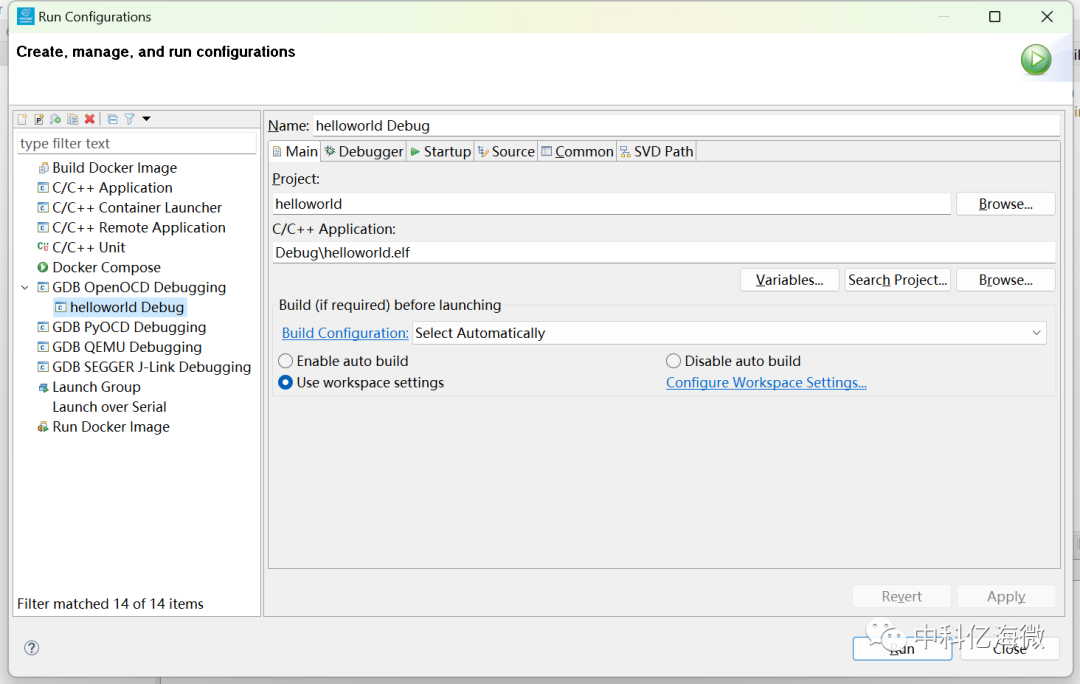

b)点击后弹出如下界面,在GDB OpenOCD Debugging按钮双击即可

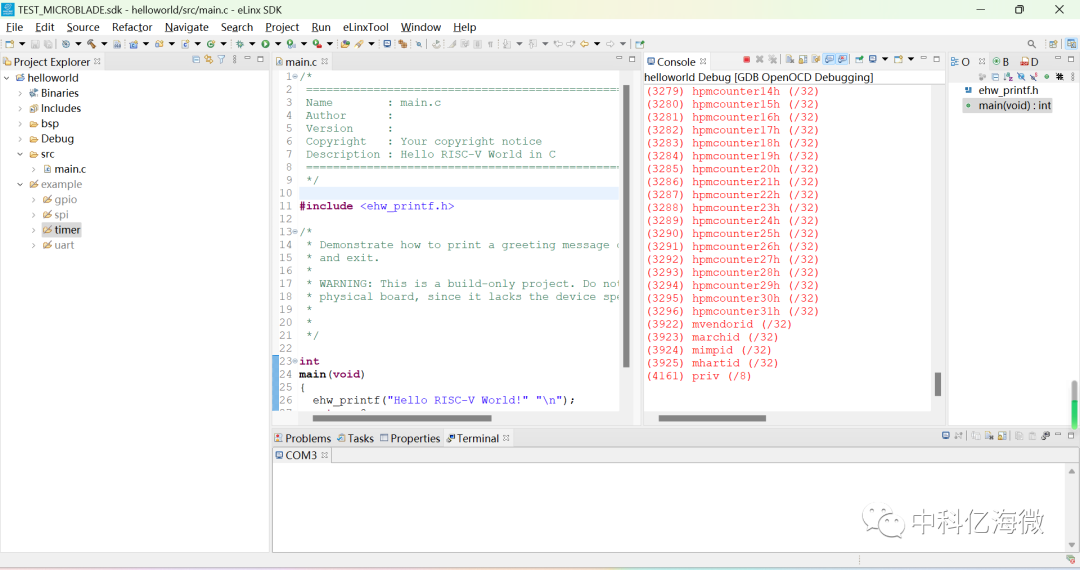

c)完成后,点击run可开始板卡联调,成功如下图所示:

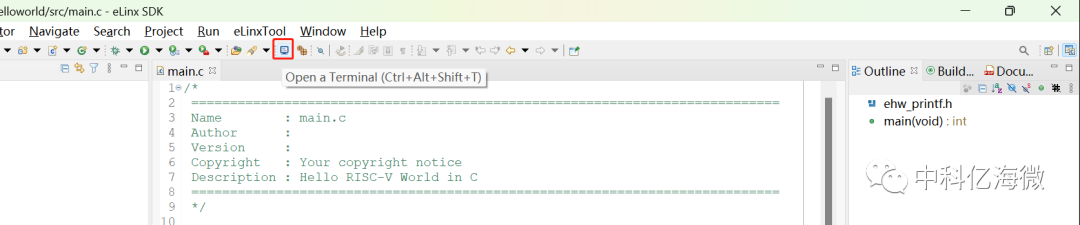

5)连接串口。选择SDK界面下方的Terminal窗口,点击下图的按钮

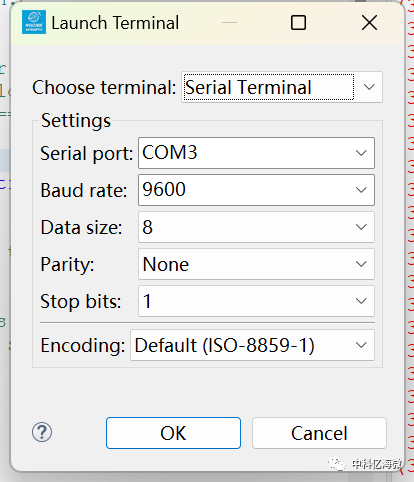

6)在弹出窗口中,进行如下配置:

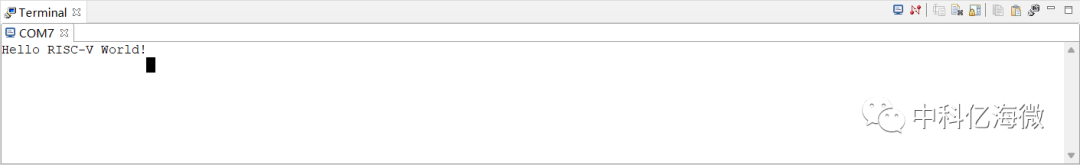

7)点击OK后,点击EQ6HL45板卡上的复位按钮(F2),Terminal界面出现了’Hello RISC-V World’字样。

中科亿海微

中科亿海微电子科技(苏州)有限公司,是中国科学院“可编程芯片与系统”研究领域的科研与产业化团队,按照国家创新驱动发展战略,发起成立的以“可编程逻辑芯片与可重构系统”为技术特色的高新技术企业。公司坚持全正向威廉希尔官方网站 路线,自主研制具有高可靠性的嵌入式可编程威廉希尔官方网站 IP核、可编程逻辑芯片、EDA软件与可重构系统,提供具有高性能和自适应计算的行业解决方案和集成威廉希尔官方网站 设计服务,具有较完善的知识产权保护体系。

审核编辑:汤梓红

-

基于EasyFPGA030的串口接收显示设计2010-03-11 803

-

基于Actel FPGA的多串口扩展设计2010-11-15 592

-

基于FPGA的SOC系统中的串口设计2010-02-08 715

-

采用Actel FPGA的多串口扩展方案2010-03-18 2696

-

基于CPLD/FPGA的多串口设计2011-04-27 917

-

基于FPGA的串口通讯与VGA显示2011-09-19 1302

-

基于FPGA的串口通信设计_王鹏2016-03-03 635

-

基于FPGA的串口通信威廉希尔官方网站 设计2017-01-24 724

-

基于FPGA Verilog-HDL语言的串口设计2017-02-16 1252

-

xilinx FPGA串口设计笔记2018-03-26 642

-

在FPGA中利用IP核实现SOC系统中的串口收发接口的设计2019-08-02 4483

-

FPGA频率计与串口通信的设计资料说明2021-03-07 598

-

基于FPGA的SDRAM串口实验2021-08-04 763

-

MicroBlade 串口设计2023-08-18 585

-

基于CPLD/FPGA的多串口扩展设计方案2023-10-27 254

全部0条评论

快来发表一下你的评论吧 !