EDA程序设计—计时器设计

电子说

描述

实训题目:计时器的设计

1 系统设计

1.1设计要求

1.1.1 设计任务

设计并制作一台计时器。

1.1.2 性能指标要求

① 用EDA实训仪的I/O设备和PLD芯片实现计时器的设计。

② 计时器能够显示时、分和秒。

③ 用EDA实训仪上的8只八段数码管显示时、分和秒(如00123625)。

④ 计时器具有复位和校准时、分、秒的按钮。

1.2 设计思路及设计框图

1.2.1设计思路

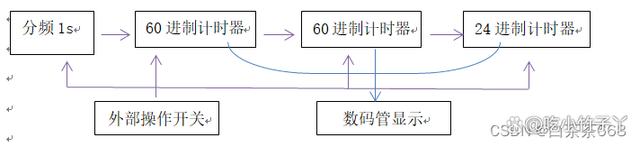

使用两个六十进制计数器和一个二十四进制计数器,设计出了一个24小时计时器系统。

输入CLK为1Hz(1s)的时钟,经过60分频后产生1分钟时钟信号,再经过60分频后产生1小时的时钟信号,最后进行24分屏得到1天的脉冲送cout输出。

将两个60分频和一个24分频的输出送8段数码管,得到24小时的计时显示。

1.2.2总体设计框图

CLK是1Hz时钟输入端。clrn复位输入端,低电平有效。jm,jf,js分别是秒,分,时的时输入端,下降沿有效。分别是秒分时的计时输出端。cout是脉冲输出端。

各个模块程序的设计

调试过程

在电脑上设计好的工程,进行编译,编译成功后进行仿真,仿真成功后生成元件并加入到bdf中,找出相应的输入输出并与模块连接好,置顶并编译,提前锁好相应的管脚。在实验室使用Quartus 软件调试,在软件中open project打开设计好的工程,还需要对bdf进行一次置顶编译下载到实验箱。

找到锁好的管脚的拨码开关或按键。拨动相应的拨码开关实现计时器的复位功能,按动jm,jf,js所锁的按键可实现时、分、秒校准。实训过程中也会出现一些错误,如无法实现23计数归0,后发现是因为程序问题,修改后调试成功。

4 功能测试

4.1 测试仪器与设备 计算机。 EDA实验箱。

4.2 性能指标测试

能按实验要求实现8只八段数码管显示(例如00235959)并具有复位和校准时、分、秒和23时亮灯警告。

附录1:仿真波形图(部分模块)

-

模拟计时器的程序和仿真资料合集2020-03-20 801

-

#硬声创作季 通电累加计时器小板设计成功,通电就计时,有市场吗?Mr_haohao 2022-10-14

-

基于STM32的正倒计时器程序设计2021-07-21 0

-

电话计时器2009-03-02 1441

-

暗室计时器2009-09-29 474

-

计时器,什么是计时器,计时器原理是什么2010-03-08 9477

-

一种实现计时器变为倒计时器的设计方案2014-01-07 8931

-

时钟计时器元件清单2015-11-18 1465

-

24秒计时器源程序2015-12-09 718

-

数字计时器Multisim设计2015-12-24 1481

-

电磁打点计时器和电火花计时器的区别2020-01-08 103361

-

电火花计时器工作原理_电火花计时器工作电压2020-01-08 23382

-

辩论赛计时器应用程序免费下载2020-05-19 598

-

EDA程序设计之计时器设计2023-08-22 420

-

光电计时器的原理和使用2023-09-22 4740

全部0条评论

快来发表一下你的评论吧 !