帧同步系统的工作原理及如何基于FPGA实现其设计

描述

1、 引言

数字通信时,一般以一定数目的码元组成一个个“字”或“句”,即组成一个个“帧”进行传输,因此帧同步信号的频率很容易由位同步信号经分频得出,但每个帧的开头和末尾时刻却无法由分频器的输出决定。为此,帧同步的任务就是要给出这个“开头”和“末尾”的时刻。通常提取帧同步信号有两种方法:一类是在信息流中插入一些特殊的码组作为每帧的头尾标记。另一类则不需要加入码组,而是利用数据码组本身之间彼此不同的特性实现同步。这里采取第一种方法——连贯式插人法实现帧同步。所谓连贯式插入法就是在每帧开头插入帧同步码。所用的帧同步码为巴克码,巴克码是一种具有特殊规律的非周期序列,其局部自相关函数具有尖锐的单峰特性,这些特性正是连贯式插入帧同步码组的主要要求之一。因此,这里提出帧同步系统的FPGA 设计与实现。

2 、帧同步系统的工作原理

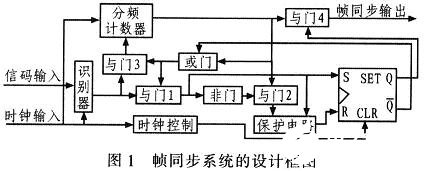

实现帧同步的关键是把同步码从一帧帧数据流中提取出来。本设计的一帧信码由39位码元组成。其中的巴克码为1110010七位码,数据码由32位码元组成。只有当接收端收到一帧信号时,才会输出同步信号。帧同步系统的设计框图如图1所示。

帧同步系统工作状态分捕捉态和维持态。同步未建立时系统处于捕捉状态,状态触发器Q端为低电平,一旦识别器输出脉冲,由于Q端为高电平,经或门使与门1输出”1”,同时经或门使与门3输出也为”1”,对分频计数器模块清零。与门1一路输出至触发器的S端,Q端变为高电平,与门4打开,帧同步输出脉冲。系统由捕捉态转为维持态,帧同步建立。

当帧同步建立后,系统处于维持态。假如此时分频器输出帧同步脉冲,而识别器却没有输出,这可能是系统真的失去同步,也可能是偶然干扰引起的,因此在威廉希尔官方网站 中加入一个保护威廉希尔官方网站 。该保护威廉希尔官方网站 也是一个分频计数器,只有在连续若干次接收不到帧同步信号时,系统才会认为同步状态丢失,由于丢失同步的概率很小,因此这里系统设置分频计数器值为5,也就是说连续5帧接收不到帧同步信号,系统才认为丢失同步状态。当然分频值可设置其他值,但该值越大,同步维持态下漏识别概率也越大。与门1的一路输出置5分频器的使能端,使之开始计数,当计数满时会输出一个脉冲使状态触发器置零,从而无帧同步信号输出,同步威廉希尔官方网站 又进入捕捉态。

3 、帧同步威廉希尔官方网站 功能模块的建模与实现

3.1 巴克码识别模块

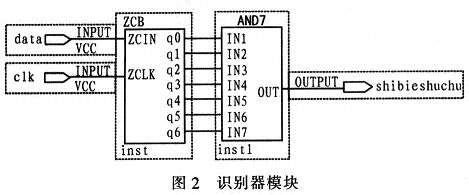

该模块的功能主要是把帧同步码巴克码从数据流中识别出来。识别器模块如图2所示。

图2中第1部分模块ZCB主要完成串并转换和移位功能,由7个D触发器和3个非门实现。第2部分模块AND7作用:只有当巴克码1110010准确输人时,识别器的输出才会为”1”。因为输出的巴克码识别信号将直接影响后续同步保护威廉希尔官方网站 ,因此准确地输出巴克码,才能避免产生假同步现象。AND7可简洁准确识别巴克码。图3为巴克码识别模块仿真图,其中,bakeshibie为识别器的输出;fenpin39为39分频计数器的输出端;zin为输入的数据;zclk为时钟信号。

帧同步系统的工作原理及如何基于FPGA实现其设计

3.2 分频计数器模块

本设计采用2个带清零的分频计数器,分别为39分频计数器和5分频计数器。其中,39分频计数器可满足7位巴克码+4字节数据的要求。当39分频器输出一个脉冲时,识别器也应输出一个脉冲,只要其相位对应输出,就能提取出帧同步信号。

39分频计数器的仿真图如图4所示,其中clk为时钟信号端;clr为时钟清零端;output为输出端。

帧同步系统的工作原理及如何基于FPGA实现其设计

3.3 同步保护模块

系统进入维持态时就需要同步保护威廉希尔官方网站 保护帧同步信号。这部分威廉希尔官方网站 由时钟控制模块、基本RS触发器模块和5分频计数器组成,其中,时钟控制模块和基本RS触发器模块的主要功能是状态转换和控制输出帧同步脉冲。对于RS触发器值得注意的是:如果R=0和 S=“0后同时发生由0至1的变化”,则输出端Q和Q都要由1向0转换,Q和Q端输出就会为任意态,这就是冒险竞争现象。当产生冒险竞争后,由于触发器的输出为任意态,就会导致整个系统的输出为任意态。解决方法是在系统中加入时钟控制模块控制触发器的复位端,确保不出现任意状态,使系统工作状态稳定。5分频器在识别器模块无输出时,这可能是系统真正失步也可能是偶尔干扰所致,只有连续5次这种情况系统才会真正认为失步。保护模块仿真图如图5所示,其中, zhengout为帧同步输出信号;clk为时钟信号;data为输入的信码;q为RS触发器的Q端;fenpin39为39分频计数器的输出端。

帧同步系统的工作原理及如何基于FPGA实现其设计

4、 帧同步系统顶层文件设计

所谓顶层文件设计就是把所涉及到的各个模块放在一起,形成一个便于阅读的图形方式,在编译各个模块时,如果设计没有错误。系统就会创建一个代表该模块的符号文件,可以被高层设计所调用。本设计中各模块通过VHDL语言进行设计,在 QuartusⅡ开发软件下编译通过。采用Altera公司Cvclone系列的EP1C12Q240C8器件,并且帧同步威廉希尔官方网站 仅用到该器件不到1%的逻辑单元。顶层设计图形如图6所示。图6中,ZCB和AND7(七输入与门)为巴克码识别器;CLKCONTR为时钟控制器;FENPIN5为5分频器计数器;FENPIN39为39分频器计数器;RS_CLK为RS触发器。

帧同步系统的工作原理及如何基于FPGA实现其设计

实验结果分析:在Quartus II环境下,时钟clk的周期为200μs,当时钟周期设定的值很小时,比如纳秒级别,系统则极易出现冒险竞争现象,因此要将时钟周期的值设定的大一些。data为输入的数据流,为了便于仿真,只在数据流中加入3组巴克码。bakeshibie为巴克码识别器的输出,当巴克码出现后,触发器的Q端变为高电平,系统进入维持态,此时5分频计数器开始计数,若在未计满5次时再次出现巴克码,则5分频计数器重新开始计数,若计满5次仍未出现巴克码,则系统彻底丢失同步状态,Q端变为低电平,系统进入捕捉态。总体设计时序仿真图如图7所示。由于此帧同步系统要应用在DPSK解调中,所以帧同步系统仿真的时钟频率要与DPSK解调的时钟频率一致。仿真时要注意码元的传输方向即巴克码是高位先发送还是低位先发送,这将影响到仿真质量。

帧同步系统的工作原理及如何基于FPGA实现其设计

5、 结论

详细阐述各模块功能,实现方法及仿真图形,系统对帧同步码(巴克码)作出严格限制,即系统只有在严格收到帧同步码后才会有帧同步信号输出,提高系统的可靠性。保护威廉希尔官方网站 设计有效降低漏同步和假同步的概率,时钟控制的RS触发器保证了同步系统状态的正确转换。同步系统各项技术指标均符合要求,工作正确可靠,有较高使用价值。

有你想看的精彩 至芯科技FPGA就业培训班——助你步入成功之路、8月12号西安中心开课、欢迎咨询! 基于FPGA的CNN加速项目案例解析 基于FPGA协处理器的算法及总线连接

扫码加微信邀请您加入FPGA学习交流群

欢迎加入至芯科技FPGA微信学习交流群,这里有一群优秀的FPGA工程师、学生、老师、这里FPGA技术交流学习氛围浓厚、相互分享、相互帮助、叫上小伙伴一起加入吧!

点个在看你最好看

原文标题:帧同步系统的工作原理及如何基于FPGA实现其设计

文章出处:【微信公众号:FPGA设计william hill官网 】欢迎添加关注!文章转载请注明出处。

- 相关推荐

- FPGA

-

FPGA设计中帧同步系统的实现2012-08-11 0

-

如何用VHDL语言实现帧同步的设计?2021-04-08 0

-

请问怎样去设计帧同步系统?2021-04-28 0

-

帧同步系统的FPGA设计2010-08-06 754

-

基于FPGA的光纤通信系统中帧同步头检测设计2010-10-26 619

-

基于FPGA的数字复接系统帧同步器设计2010-12-01 419

-

一种高速帧同步和相位模糊估计的方法及其FPGA实现2010-01-27 1469

-

VHDL语言实现的帧同步算法2010-07-02 1735

-

基于FPGA的帧同步系统设计方案2013-11-11 4905

-

基于FPGA的帧同步器的设计与仿真2016-01-04 542

-

采用FPGA实现同步、帧同步系统的设计2017-11-07 1091

-

集中式插入法帧同步系统的原理、工作流程及利用VHDL和FPGA进行设计2018-11-20 5430

-

帧同步系统的工作原理及如何基于FPGA实现其设计2020-01-08 12510

-

基于EP1C6T144C8 FPGA实现STM-1同步系统的应用方案2021-06-23 3222

全部0条评论

快来发表一下你的评论吧 !