半导体“三雄”抢攻下一代技术!

描述

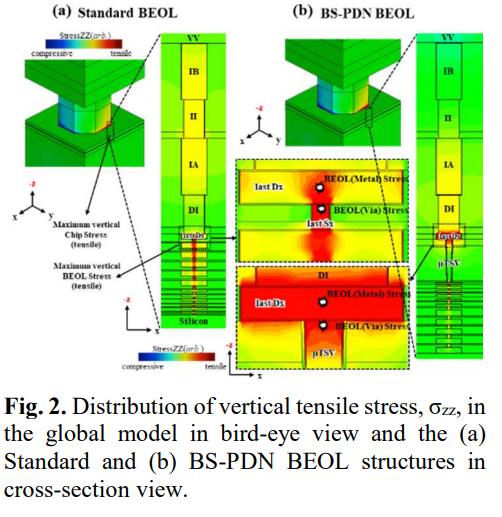

台积电、三星、英特尔等芯片大厂近期积极布局背面供电网络(BSPDN),像三星计划将BSPDN技术用于2纳米芯片,该公司近日也于日本VLSI研讨会上公布BSPDN研究结果。

根据比利时微电子研究中心(imec)的说法,BSPDN目标是减缓逻辑芯片正面在后段制程面临的壅塞问题,通过威廉希尔官方网站 协同优化(DTCO),在标准单元实现更有效率的导线设计,协助缩小逻辑标准单元的尺寸。

BSPDN 可解释成小芯片设计演变,原本将逻辑威廉希尔官方网站 和存储器模组整合的现有方案,改成正面具备逻辑运算功能,背面供电或讯号传递。

一般而言,通过晶圆正面供电的方法虽能完成任务,但会使功率密度下降、性能受损。

三星称跟传统方法相比,BSPDN可将面积减少14.8%,芯片能拥有更多空间,公司可增加更多晶体管,提高整体性能; 线长也减少9.2%,有助降低电阻、使更多电流通过,进而降低功耗,改善功率传输状况。

▲ 三星分享 BSPDN 研究成果 (Source:三星)

今年6月,英特尔也举办了BSPDN相关的发布会,并将其命名为PowerVia。该公司计划在英特尔20A制程中采用这方法,使得芯片利用率有望达到90%。

英特尔认为,PowerVia将解决硅架构中的互连瓶颈,透过晶圆背面提电来实现连续传输; 该公司预计在2024年推出的 Arrow Lake CPU 中采用这种新方法。

另有消息称,台积电如期2025年上线2纳米制程,2025年下半年在新竹量产,计划2026年推出N2P制程,这个制程将采用BSPDN技术。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

2016CES:Atmel下一代触摸传感技术亮相2016-01-13 0

-

半导体行业是否为下一代IVN协议的需求做好充分准备?2018-10-17 0

-

下一代SONET SDH设备2019-09-05 0

-

请问Ultrascale FPGA中单片和下一代堆叠硅互连技术是什么意思?2020-04-27 0

-

一文详解下一代功率器件宽禁带技术2020-10-27 0

-

下一代超快I-V测试系统关键的技术挑战有哪些?2021-04-15 0

-

Freescale:半导体技术的进步推动下一代医疗设备的发展2013-05-09 1384

-

Vuzix与Plessey半导体公司合作打造下一代AR智能眼镜2018-06-19 1731

-

探析下一代半导体材料在改造照明技术方面的潜力2019-02-13 2992

-

半导体氮化铟镓的红色LED,有望成为下一代显示技术的主流2020-07-10 5934

-

韩国2021年度下一代智能半导体研发计划发布2021-01-20 2407

-

下一代 NXP 低 VCEsat 晶体管:分立半导体的改进技术-AN110452023-03-03 244

-

三星电机宣布下一代半导体封装基板技术2023-09-08 814

-

意法半导体将推出基于新技术的下一代STM32微控制器2024-03-28 568

-

意法半导体下一代汽车微控制器的战略部署2024-11-07 412

全部0条评论

快来发表一下你的评论吧 !