如何最大限度地提高SiC MOSFET性能呢?

模拟技术

描述

在高功率应用中,碳化硅(SiC)MOSFET与硅(Si)IGBT相比具有多项优势。其中包括更低的传导和开关损耗以及更好的高温性能。

SiC MOSFET快速开关的挑战

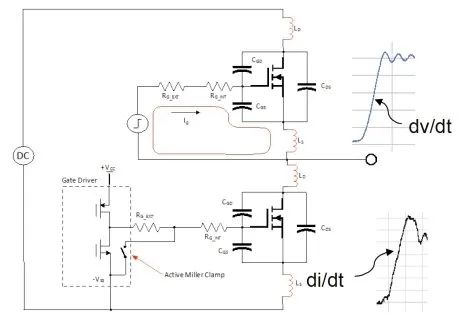

威廉希尔官方网站 布线中的器件电容、寄生电感和电容元件会极大地影响开关性能。图1显示,高开关di/dt会因栅极-源极回路中的寄生电感而在栅极驱动器中产生振铃和振荡。这会通过栅极-漏极电容(Cgd)耦合到关断状态的器件,并导致误导通。

图1:显示来自SiC MOSFET器件和威廉希尔官方网站 板布局中寄生元件的高压和电流尖峰

这些瞬变会降低设备性能和可靠性。例如,超过额定栅极电压的持续栅极过冲会损坏栅极氧化层并限制器件的使用寿命。

FET导通时的高栅极瞬变会使FET进入饱和状态,而不是首选的线性区域,从而产生更高的损耗并影响可靠性。

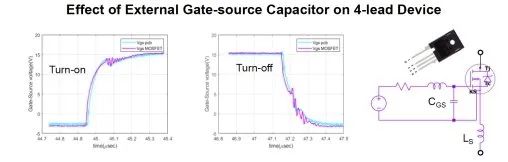

减慢开关瞬变,例如,通过增加更高的栅极电阻器或包括一个外部栅极-源极电容,可以减少此类过冲,但会带来更高的开关损耗。

因此,我们的目标是尽量减少这些瞬态效应,同时保持尽可能高的开关效率。让我们看看实现这一目标的一些潜在方法。

关于最大限度地提高SiC MOSFET性能的一些建议

使用源开尔文接法

如图2所示,添加一个源开尔文连接将电源和信号回路分开,即使在外部寄生电感Ls的情况下也能实现平滑的开关转换。此类4引线器件推荐用于大功率应用。

图2:通过使用源开尔文连接改进开关

分裂栅电阻的使用

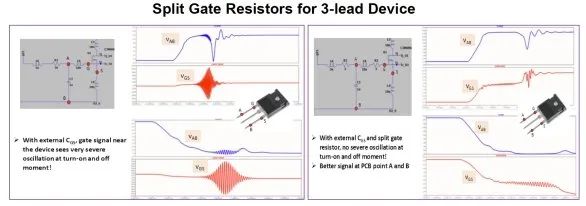

分裂栅电阻基本上可以形成一个RLC网络来抑制栅极振荡。栅极电阻RG在添加的外部CGS电容之前和之后一分为二,如图3所示。该外部CGS两端的电压VAB在开启和关闭期间具有更小的瞬态峰/谷过程。这导致器件栅极上的VGS信号更平滑,即使在3引脚器件中存在外部源电感的情况下也是如此。

图3:使用分裂栅电阻实现更平滑的栅极驱动

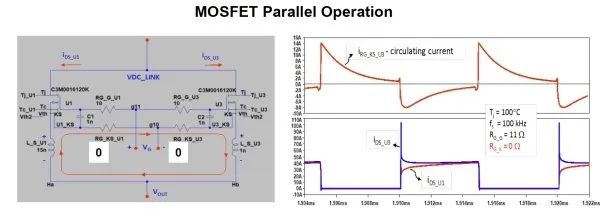

平衡并联器件中的寄生电感

并联SiC MOSFET是提高整体驱动电流的重要方法。匹配固有的MOSFET参数(例如阈值电压VTH)对于实现平衡电流共享很重要。同样重要的是平衡威廉希尔官方网站 板布局中的寄生路径。图4显示了源极电感不匹配的影响,导致2个MOSFET的漏极电流高度不平衡。对称布局可以改善负载分配和模块的整体安全工作区(SOA)。

图4:并联SiC MOSFET的源极电感失配的影响

平衡并联器件中的输入电容

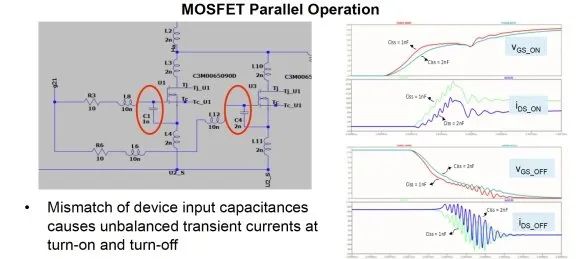

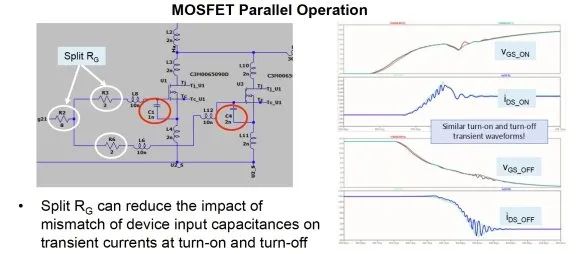

与上述电感的情况类似,输入电容的不匹配会延迟一个器件相对于另一个器件的开关转换,从而产生不平衡的瞬态电流,并可能超过其中一个器件的额定值。图5(a)说明了这种影响。如图5(b)所示,使用分裂栅电阻可以减少这种不匹配的影响。

图5:(a)显示并联连接的SiC MOSFET的器件输入电容不匹配的影响,而(b)显示即使在这种电容不匹配的情况下,使用分裂栅电阻也能改善平衡

还可以考虑几个其他因素来最大限度地提高SiC MOSFET性能:

- 如图1中低侧FET所示,有源米勒钳位为通过密勒电容CGD耦合的dv/dt瞬变产生的高栅极电压尖峰创建低阻抗路径。当器件在高温下运行(由于VTH的负温度系数),并且在关断时没有负栅极驱动时,此类钳位特别有用。它们还有助于在选择RG-OFF栅极电阻时考虑开关损耗EOFF而不是米勒引起的振荡。

- 将栅极驱动器放置在尽可能靠近MOSFET的位置。

- 使电源和栅极信号走线尽可能远离彼此

- 在输入栅极路径中使用铁氧体磁珠。铁氧体磁珠(例如由镍锌制成的磁珠)有助于耗散噪声范围内的频率,例如50–200MHz范围内的频率,而不会因为其在开关频率下的低阻抗而对开关性能产生负面影响。

- 为关断使用负栅极偏置会增加成本和复杂性,但会使关断对导致栅极振铃的开关瞬变更加鲁棒。

- 通孔器件应使用尽可能少的引线和其他布线技术,以尽量减少栅极回路电感。

- 使用具有较低CGD/CGS比值的设备将减少米勒反馈的影响。

结论

以数百kHz的频率切换1000V以上的高压电源轨是一项复杂的操作,需要优化功率器件、威廉希尔官方网站 板布局、栅极驱动器和外部无源元件。在本文中,我们重点介绍了一些可以大大改进单个和并联器件开关的技术。

-

为何使用 SiC MOSFET2017-12-18 0

-

SiC MOSFET SCT3030KL解决方案2019-07-09 0

-

通过精心的IF信号链设计最大限度地提高16位 105Msps ADC的性能2019-09-04 0

-

浅析SiC-MOSFET2019-09-17 0

-

如何最大限度提高Σ-Δ ADC驱动器的性能2021-01-06 0

-

机器监测:通过性能测量,最大限度提高生产质量2016-03-21 400

-

DN468-精心设计IF信号链,最大限度提高16位、105Msps ADC的性能2021-04-14 426

-

最大限度地提高高压转换器的功率密度2023-12-06 3203

-

如何最大限度地提高电子设备中能量收集的效率2022-12-30 1089

-

最大限度地提高数据库效率和性能VMware环境使用32G NVMe光纤渠道2023-08-07 267

-

最大限度地减少SIC FETs EMI和转换损失2023-09-27 486

-

最大限度提高∑-∆ ADC驱动器的性能2023-11-22 298

-

最大限度地提高GSPS ADC中的SFDR性能:杂散源和Mitigat方法2024-10-10 181

-

最大限度地提高MSP430™ FRAM的写入速度2024-10-18 112

全部0条评论

快来发表一下你的评论吧 !