【CVM01系列】| MCU硬件设计指南:时钟威廉希尔官方网站

电子说

描述

曦华科技CVM01xx系列芯片集成多个时钟源:

(1) 内部晶体振荡威廉希尔官方网站 ,可外接4MHz~40MHz晶体或陶瓷谐振器

(2) 外部方波输入时钟:最高可达50MHz

(3) 内部48MHz高速RC振荡器(FIRC)

(4) 内部8MHz低速RC振荡器(SIRC)

(5) 内部128kHz低功耗振荡器(LPO)

(6) 内部锁相环(PLL),提供高速的系统运行时钟

FIRC、SIRC是内部时钟源的,不必从硬件设计角度考虑。外部振荡器的工作范围为4~ 40MHz,为PLL及部分外设提供时钟源。

一、EXTAL和XTAL引脚

此类引脚为晶体提供接口,以控制内部时钟发生器威廉希尔官方网站 ,EXTAL是晶体振荡器放大器的输入,XTAL是晶体振荡器放大器的输出。Pierce振荡器提供了一个强大、低噪音、低功耗的外部时钟源,可为典型的晶体振荡器提供最佳启动余量。CVM01xx系列支持4~40MHz的晶体或谐振器。

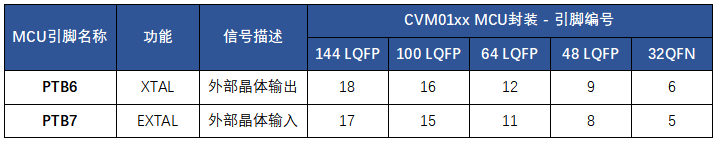

△表1 CVM01xx - EXTAL和XTAL引脚

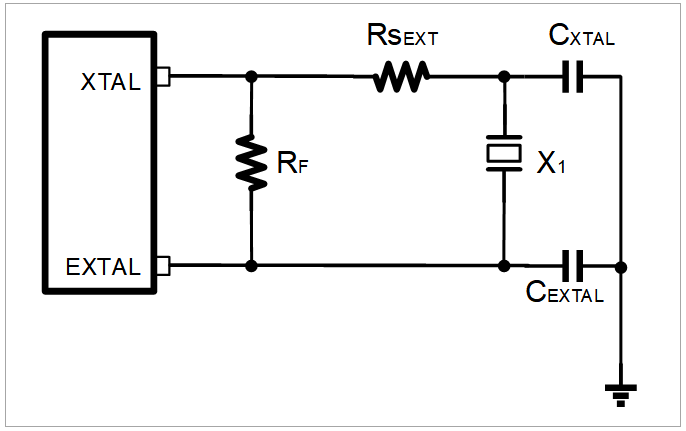

△图1 参考振荡器威廉希尔官方网站

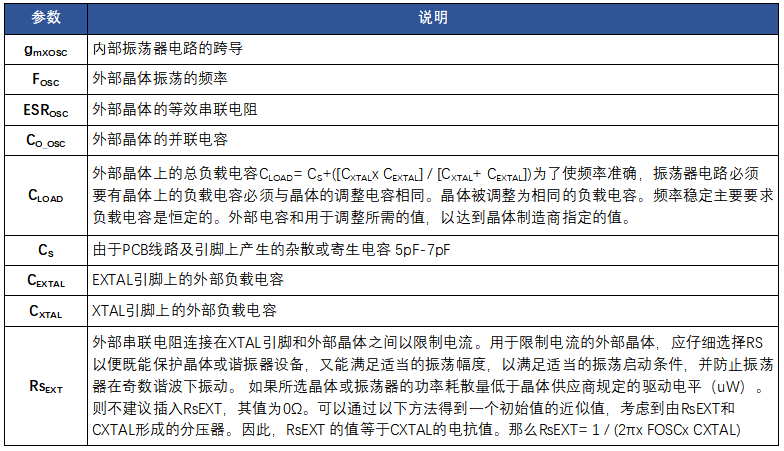

△表2 振荡器威廉希尔官方网站 的组成部分

二、关于振荡器威廉希尔官方网站 PCB布局的建议

晶体振荡器是一个模拟威廉希尔官方网站 ,必须根据模拟板布局规则仔细设计,具体如下:

(1) 建议将PCB板送至晶体制造商,以确定负向振荡余量及电容最佳值。数据表中包含对振荡回路电容的建议,这些值与预期PCB、引脚等杂散容量值一起,作为一个起点

(2) XTAL/EXTAL引脚、晶体和外部电容之间的信号走线须尽可能短,这些走线应只连接到所需振荡器元件,而不能连接到任何其他设备或元件。在MCU和外部振荡器之间的连接不应有超过一个接地的通孔,可最大限度减少寄生电容并降低对串扰和EMI的敏感性

(3) 尽量使其他数字信号线,特别是时钟线、模拟和频繁跳变的信号线远离晶体连接线,来自数字信号的串扰可能会对振荡器信号的低幅值造成影响

(4) 应在晶体振荡器区域下方放置一个接地区域,该地平面须是连接到CVM01xx的VSSx基准的干净地。切勿将接地保护环与威廉希尔官方网站 板上的任何其他接地信号相连,同时要避免实现接地环路

(5) 主要的振荡回路电流在晶体和负载电容之间流动,此信号路径(晶振到晶振)应尽可能短,并应有一个对称布局,因此两个电容器的地线应尽可能靠近

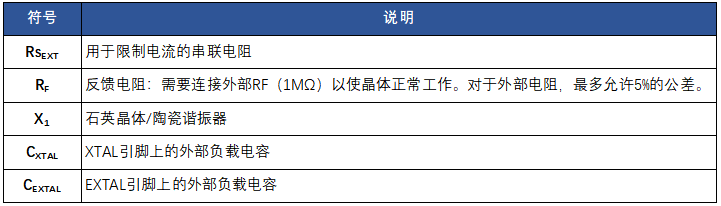

如下图所示,为振荡器布局的推荐位置和PCB走线。

△图2 建议的晶体振荡器布局

当gmXOSC>5 xgmcrit 时,晶体振荡器威廉希尔官方网站 提供非常安全的稳定振荡。

gmcrit 定义为:gmcrit = 4 x (ESROSC + RsEXT) x (2π x FOSC)2 x (CO_OSC + CLOAD)2

其中:

△表3 超导方程 - 参数

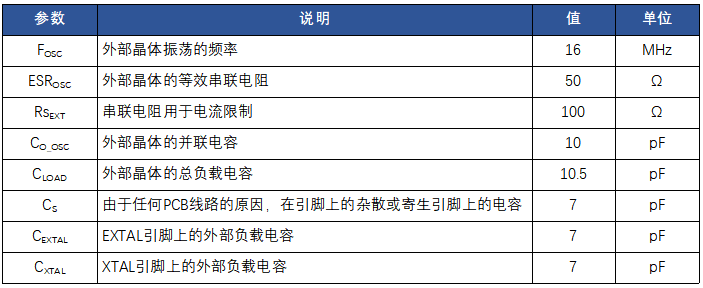

例如,在CVM01xx单片机中设计振荡回路,最大的放大器跨导值为gmOSCX=27 mA/V,频率范围为4 ~ 40MHz,选择晶体AT-16.000MAGE-x - 16MHz /TXC晶体。

该设计具有以下特性:

△表4 皮尔斯振荡器设计示例

gmcrit = 4 x (50 + 100) x (2π x [16 x 106])2 x ([10 x 10-12] + [10.5 x 10-12]2

gmcrit = 2.548 mA/V

5 x gmcrit = 12.742 mA/V

由于晶体振荡器的超导(27 mA/V)高于5 x gmcrit,因此对增益余量的估计足以启动振荡。预计振荡器将在数据手册中规定的典型延迟后达到稳定振荡。基于振荡器制造商的分析和特性,RsEXT以及CEXTAL和CXTAL的值可被调整或重新定义,以确保安全振荡余量。

频率计设备可用于检查和测量晶体振荡或任何其他信号特性,但一般不建议使用示波器和频谱分析仪,因为这此类设备通常不能区分主振荡和假振荡,同时,若示波器探针(尽管有些探针的阻抗很低)直接连接到振荡威廉希尔官方网站 ,它将停止并可能影响或削弱晶体振荡。

来源:深圳曦华科技

审核编辑:汤梓红

-

MSPM0 G 系列 MCU 硬件开发指南2023-04-12 0

-

【CVM01系列】| MCU硬件设计指南:用于CAN通信的FlexCAN硬件模块2023-09-18 751

-

【CVM01系列】| MCU硬件设计指南:用于LIN接口的UART模块2023-09-18 1848

-

【CVM01系列】| MCU硬件设计指南:模拟比较接口2023-09-18 741

-

【CVM01系列】| MCU硬件设计指南:调试和编程接口2023-09-18 1141

-

【CVM01系列】| MCU硬件设计指南:电源系统2023-09-18 955

-

曦华科技汽车MCU芯片CVM01系列典型应用案例2023-12-22 1319

-

曦华科技车规级电容触控型CVM012x系列MCU正式上市!2024-03-15 720

-

曦华科技车规级电容触控型CVM012x系列MCU正式上市2024-03-22 476

-

曦华科技推出首款车规级电容触控型CVM012x系列MCU2024-03-22 452

-

MSPM0 G系列MCU硬件开发指南2024-09-05 156

-

MSPM0 L 系列 MCU硬件开发指南2024-09-09 118

-

MSPM0 L系列MCU硬件开发指南2024-09-07 159

-

MSPM0 C系列MCU硬件开发指南2024-09-27 124

全部0条评论

快来发表一下你的评论吧 !