GIC是什么意思 GIC硬件原理

描述

GIC硬件原理

- ARM公司提供了一个通用的中断控制器

GIC(Generic Interrupt Controller),GIC的版本包括V1 ~ V4,由于本人使用的SoC中的中断控制器是V2版本,本文将围绕GIC-V2来展开介绍;

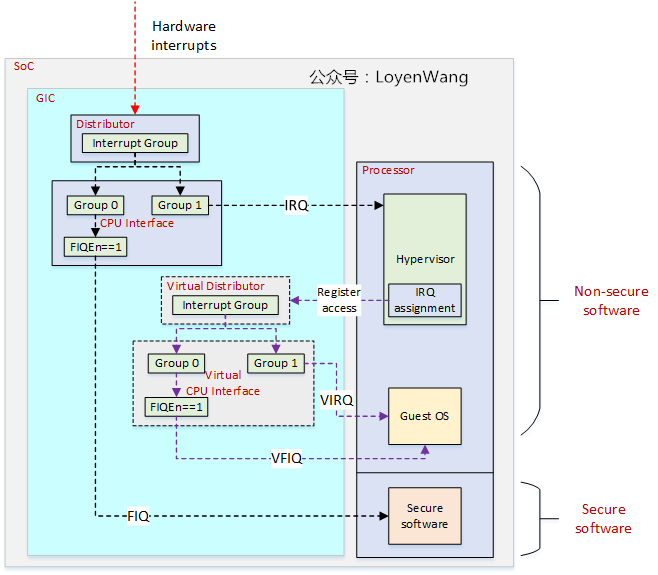

来一张功能版的框图:

GIC-V2从功能上说,除了常用的中断使能、中断屏蔽、优先级管理等功能外,还支持安全扩展、虚拟化等;GIC-V2从组成上说,主要分为Distributor和CPU Interface两个模块,Distributor主要负责中断源的管理,包括优先级的处理,屏蔽、抢占等,并将最高优先级的中断分发给CPU Interface,CPU Interface主要用于连接处理器,与处理器进行交互;Virtual Distributor和Virtual CPU Interface都与虚拟化相关,本文不深入分析;

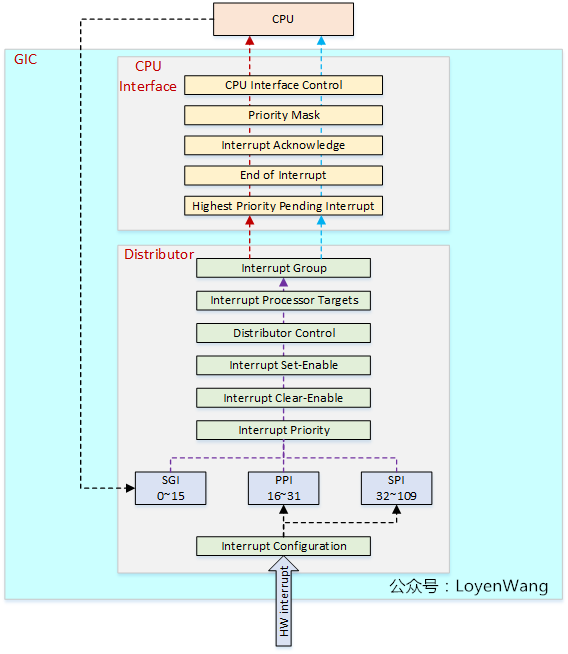

再来一张细节图看看Distributor和CPU Interface的功能:

GIC-V2支持三种类型的中断:SGI(software-generated interrupts):软件产生的中断,主要用于核间交互,内核中的IPI:inter-processor interrupts就是基于SGI,中断号ID0 - ID15用于SGI;PPI(Private Peripheral Interrupt):私有外设中断,每个CPU都有自己的私有中断,典型的应用有local timer,中断号ID16 - ID31用于PPI;SPI(Shared Peripheral Interrupt):共享外设中断,中断产生后,可以分发到某一个CPU上,中断号ID32 - ID1019用于SPI,ID1020 - ID1023保留用于特殊用途;

Distributor功能:- 全局开关控制

Distributor分发到CPU Interface; - 打开或关闭每个中断;

- 设置每个中断的优先级;

- 设置每个中断将路由的CPU列表;

- 设置每个外设中断的触发方式:电平触发、边缘触发;

- 设置每个中断的Group:Group0或Group1,其中Group0用于安全中断,支持FIQ和IRQ,Group1用于非安全中断,只支持IRQ;

- 将

SGI中断分发到目标CPU上; - 每个中断的状态可见;

- 提供软件机制来设置和清除外设中断的pending状态;

- 全局开关控制

CPU Interface功能:- 使能中断请求信号到CPU上;

- 中断的确认;

- 标识中断处理的完成;

- 为处理器设置中断优先级掩码;

- 设置处理器的中断抢占策略;

- 确定处理器的最高优先级pending中断;

中断处理的状态机如下图:

Inactive:无中断状态;Pending:硬件或软件触发了中断,但尚未传递到目标CPU,在电平触发模式下,产生中断的同时保持pending状态;Active:发生了中断并将其传递给目标CPU,并且目标CPU可以处理该中断;Active and pending:发生了中断并将其传递给目标CPU,同时发生了相同的中断并且该中断正在等待处理;

GIC检测中断流程如下:

- GIC捕获中断信号,中断信号assert,标记为pending状态;

Distributor确定好目标CPU后,将中断信号发送到目标CPU上,同时,对于每个CPU,Distributor会从pending信号中选择最高优先级中断发送至CPU Interface;CPU Interface来决定是否将中断信号发送至目标CPU;- CPU完成中断处理后,发送一个完成信号

EOI(End of Interrupt)给GIC;

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

Linux GIC驱动数据结构分析2023-09-28 556

-

ARM之中断GIC分析2018-11-26 0

-

GIC硬件原理是什么?2022-02-07 0

-

ARM GIC(一)之ARM soc中断的处理介绍2022-04-06 0

-

ARM GIC(二)之中断术语的定义2022-04-06 0

-

GIC ITS的ITS tables和Command Queue访问简析2022-12-20 0

-

基于GIC的物联网的应用方案2017-09-18 627

-

小电阻器对治理电网GIC的效果分析2018-01-04 798

-

应用K值算法的甘肃电网GIC-Q扰动计算2018-01-31 656

-

英特尔Altera系列cyclone V HPS GIC2018-05-29 9476

-

扒一扒GIC-600的相关知识2023-02-06 2739

-

GIC驱动的执行流程是什么2023-09-28 536

-

GIC-600的组件是如何连接的2023-11-07 689

-

GIC-600的内部结构组件2023-11-07 624

-

gic和ARM Core的连接2023-11-07 632

全部0条评论

快来发表一下你的评论吧 !