IBIS模型入门介绍

描述

IBIS(Input/Output Buffer Information Specification)是一个用于仿真的描述性文件,它从元件的行为出发描述了器件输入输出端口的电气特性,不会涉及具体威廉希尔官方网站 结构以及芯片的工艺参数等信息,半导体制造商很容易提供这种模型给客户,而不暴露自己的知识产权。

IBIS模型是由器件内部的电气参数数值构成的数据列表,这些数据可以反映器件的开关速度、驱动能力等特性。IBIS模型的核心是把器件简化为缓冲器(Buffer)模型,它的行为级特性主要描述一些V/I和V/t曲线,通过V/I曲线的形式表示缓冲器的输出阻抗,通过V/t曲线的形式表示高低电平转换特性。

如何建立IBIS模型

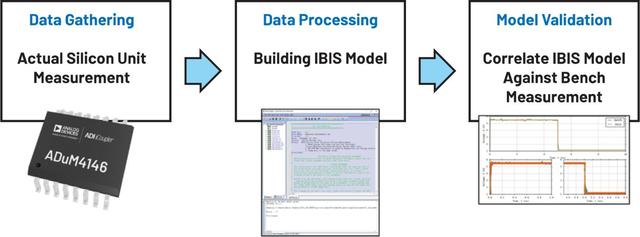

IBIS模型可以通过仿真器件的SPICE模型来获得,也可以用直接测量的方法来获得。如果选择前一种方法,可以使用SPICE进行仿真,收集每个输出/输出缓冲器的V/I和V/T数据。这样可以在模型中包含过程转折数据。然后,使用IBIS网站上的SPICE至IBIS转换程序可以由SPICE生成IBIS模型。

图片来源:Analog Device

IBIS模型结构

IBIS规范支持几种输入和输出,例如可建模为三态、集电极开路、开漏、I/O和ECL的输入/输出。第一步是识别器件上不同类型的输入和输出,确定设计中存在多少缓冲器。值得注意的是在IBIS文件中一个模型可用于表示多个输入或输出。然而,如果C_Comp(结电容)和封装参数不同,就需要不同的模型。

IBIS的模型结构输入和输出如下图:

1.输出结构,包含一个PMOS、一个NMOS、两个ESD保护二极管、芯片的电容和封装寄生参数:C_PKGR_PKGL_PKG是整个芯片的等效电容、电阻、电感特性,C_Comp为硅片上脚的压焊盘电容。

图片来源:芯语

2.输入结构,包含两个ESD保护二极管、芯片的电容和封装寄生数:C_PKGR_PKGL_PKG是整个芯片的等效电容、电阻、电感特性,C_Comp为硅片上脚的压焊盘电容。

图片来源:芯语

IBIS文件结构

IBIS文件不是可执行文件;它是收集所有描述器件电器性能数据的文件,能在仿真器中使用。IBIS文件包括三个主要部分:

1.头文件或关于文件、器件和公司的一般信息

2.器件名称、引脚排列和引脚到缓冲器映射

图片来源:Analog Device

3.模型数据,模型对应的Pulldown、Pullup、Power_Clamp、Gnd_Clamp的IlV数据表;Ramp数据;描述波形上升/下降沿的VIT数据表等

图片来源:CSDN

IBIS模型可包含多个器件的特征。在这种情况下,第2和第3点随包含的器件而重复多次。

IBIS在信号完整性中的应用

IBIS在信号完整性仿真中有不可或缺的作用,它可以作为一个源端和接收端。它可以被大多数的EDA软件识别,并且在有些仿真的软件中没有IBIS模型,是不能进行时域仿真的。在IBIS模型的基础之上,我们可以分析传输线上的信号完整性问题,包括源端到负载端的阻抗、串扰、反射、时延等时域问题。IBIS模型会把每个I/O或pin分为几种状态(输入、输出、浮空),把这几种状态配置成几种模型,通过调用I/O或pin的几种模型来模拟输入输出。

-

IBIS模型如何导入到LTspice中?2024-01-03 0

-

IBIS 模型2008-07-30 0

-

IBIS模型2013-11-06 0

-

请问有人知道IBIS模型怎么使用吗?2017-02-13 0

-

跪求ibis仿真模型2017-12-06 0

-

跪求IBIS模型2017-12-06 0

-

高速互连IBIS仿真模型概述2018-09-03 0

-

生成IBIS模型错误2019-05-27 0

-

哪里可以找到IBIS模型?2019-07-19 0

-

关于virtex-5的IBIS模型的问题如何解决2020-06-03 0

-

如何利用IBIS模型研究信号完整性问题?2021-04-21 0

-

不能把AD4003芯片的IBIS模型导入ADS怎么处理?2023-12-01 0

-

什么是IBIS模型?以及IBIS模型的仿真及优缺点2009-03-20 4979

-

AN-715: 走近IBIS模型:什么是IBIS模型?它们是如何生成的?2021-03-21 1003

-

IBIS建模:为何以及如何创建您自己的IBIS模型2023-06-15 2153

全部0条评论

快来发表一下你的评论吧 !