你想自己设计一个FPGA IP吗!

可编程逻辑

描述

开发和验证 FPGA IP 不仅仅是编写 HDL,而是需要更多的思考。让我们来看看如何做吧!

介绍

当我们开发基于 FPGA 的解决方案时,我们会尽可能利用手上的 IP,因为这会加速开发。然而,在某些情况下,我们需要使用自定义 IP 核,以应对新项目。

开发和验证此 IP 块会带来一些挑战,如果做得不正确,可能会让项目进度变得缓慢。

当然,在使用 FPGA 时,我们需要考虑的关键事情之一是需要首先考虑我们希望实现的功能,以及遵循正确的开发流程。

为了说明这个过程,我们以实际项目为示例,过程如下:

- 定义需求

- 创建微架构和接口

- 编写模块的RTL描述

- 开发 RTL 接口的总线功能模型

- 创建仿真平台进行验证

要求

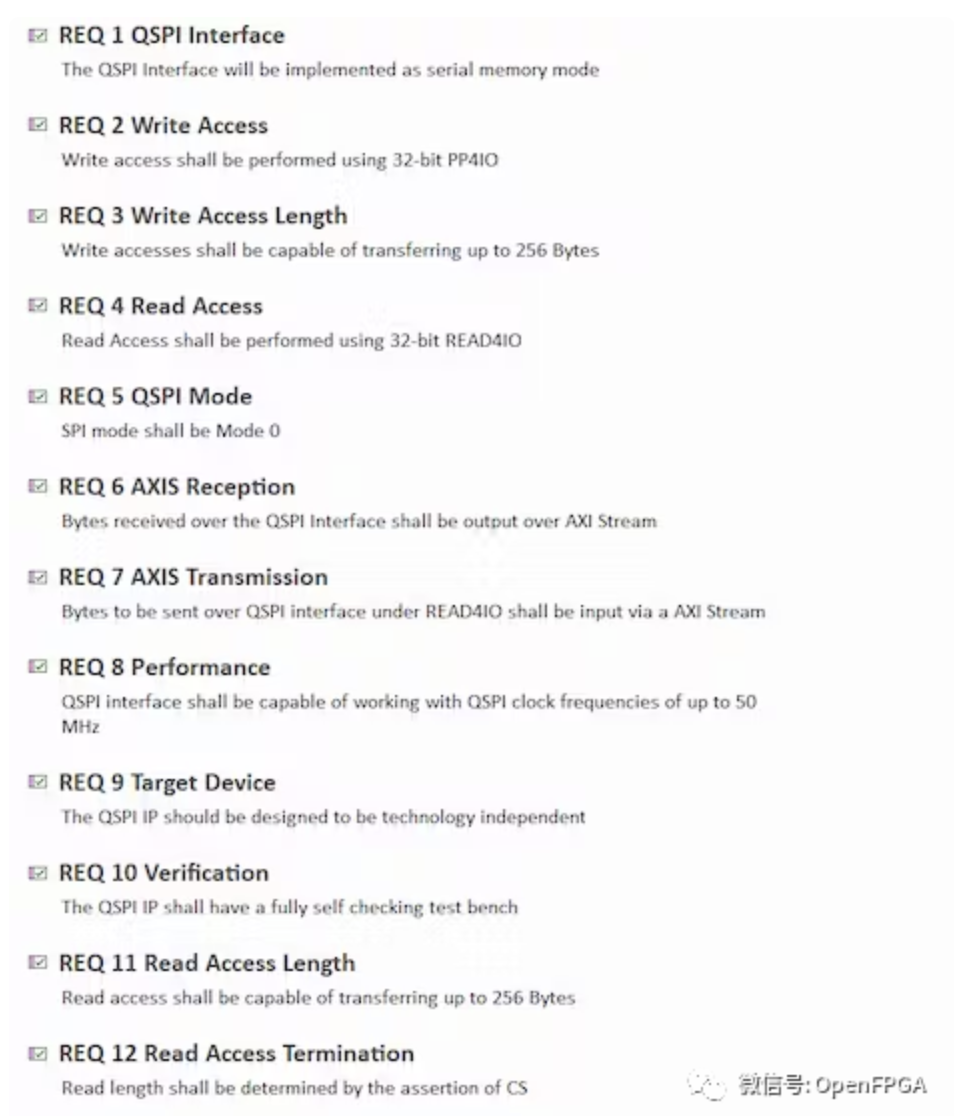

示例项目,我们将创建一个简单的 AXI Stream QSPI 从接口IP,具有以下要求:

创建IP的这些要求非常简单。然后,我们可以将该模块与之前的项目集成,例如:可以通过 QSPI 访问芯片内的AXI4总线。

微架构和接口

接下来我们需要创建微架构,这意味着我们需要了解串行存储器模式下的 QSPI 是如何工作的。

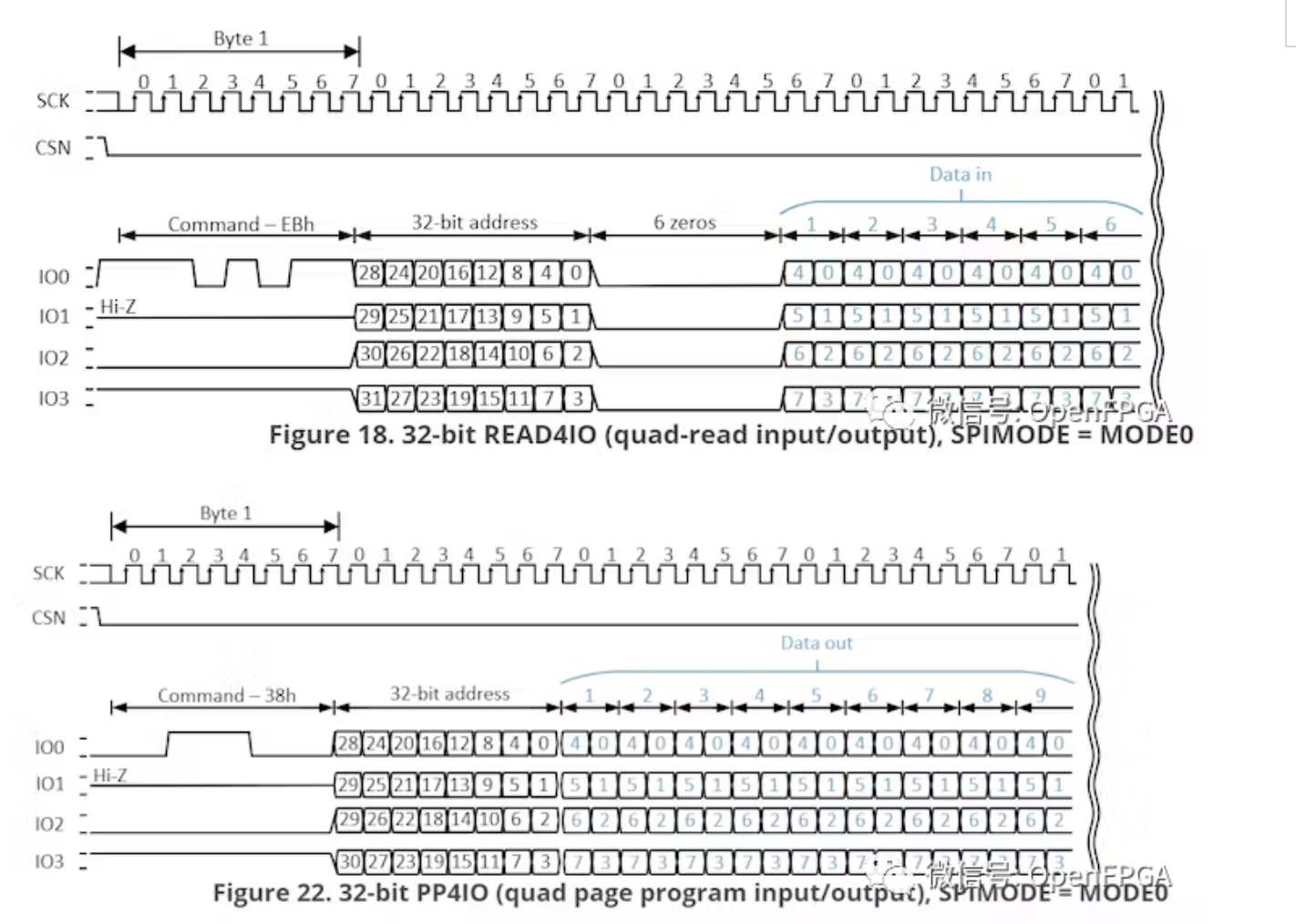

READ4IO 和 PP4IO 的波形如下所示

它们首先使用单线到 IO0 来发送命令 0x38(用于写入操作)或 0xEB(用于读取操作)。

命令发送后,将使用所有 IO 执行事务的其余部分。

对我们架构的影响是,我们需要一个 8 元素移位寄存器用于 IO0,2 元素移位寄存器用于 IO1-3。收到命令后,我们就可以仅使用 IO0 寄存器的较低两个元素。

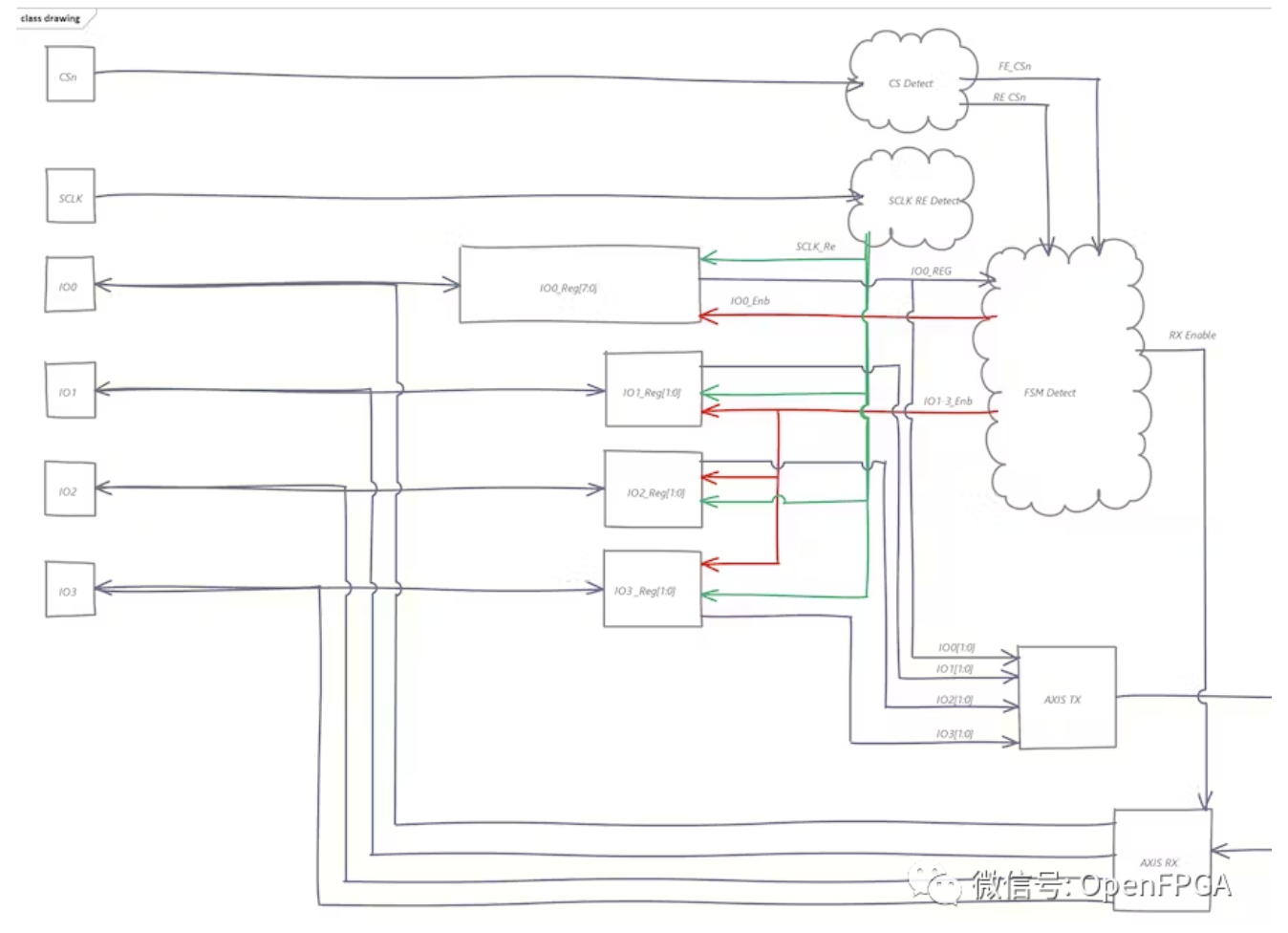

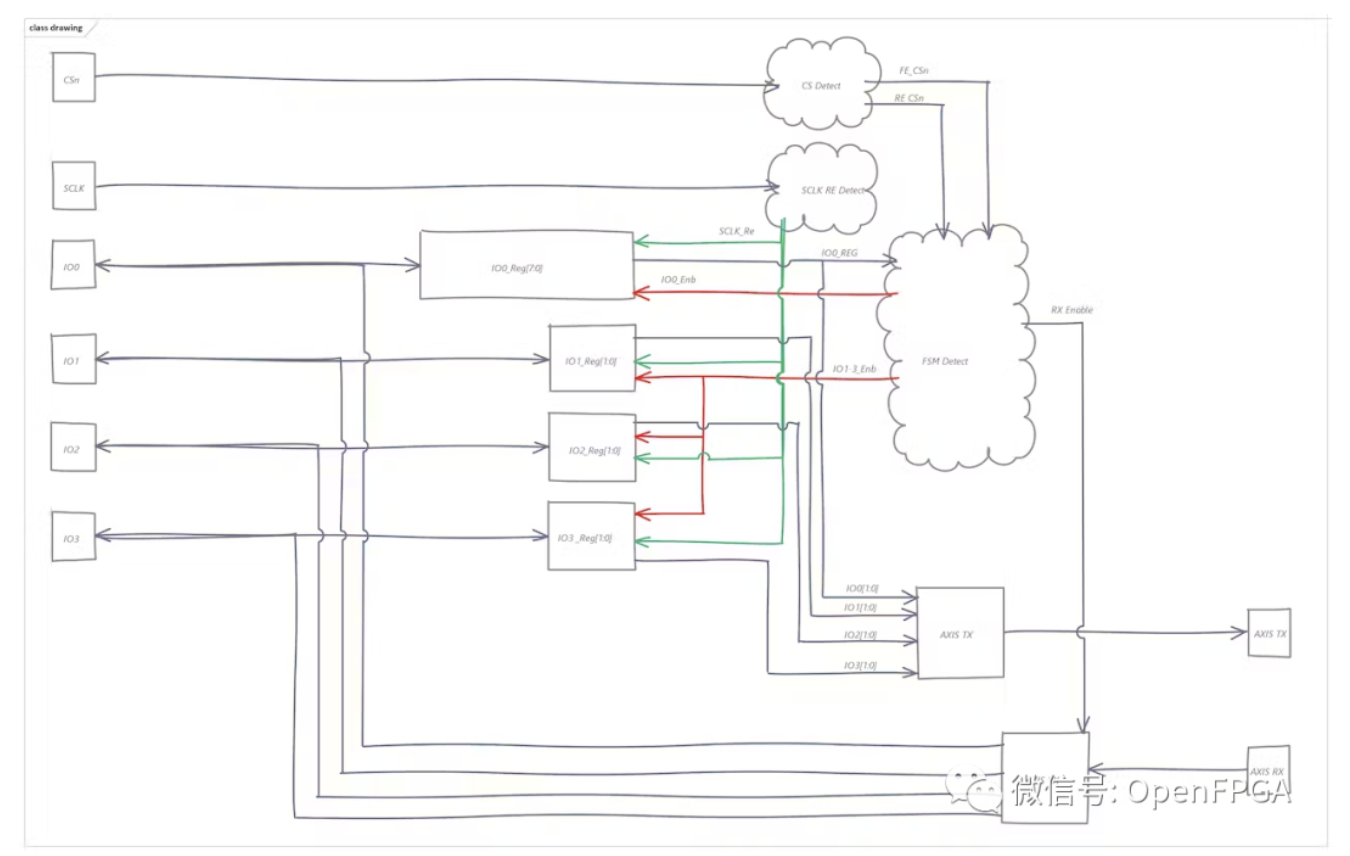

因此,我们的微架构需要能够执行以下操作

- 通过识别 CSn 的下降沿来检测新事务

- 启用新事务后检测 SCK 上的上升沿

- 使能数据移入 IO0 寄存器

- 一旦 8 位数据位于 IO0 寄存器中,具体取决于检查是否有效的读或写命令

- 对于写使能 IO1-3 以及 IO0 - 每两个 SCLK 在 AXIS 接口上输出一个字节的数据。确保 IO 驱动程序在该状态下处于三态。

- 对于读取,在虚拟时钟周期期间,从 AXIS 接口读取

- 对于在虚拟周期结束时读取,输出 IO0-IO3 上的数据

- CSn 的取消断言会停止事务并复位状态机等。

微代码架构完成后,我们就可以编写 HDL。

设计微架构时的关键要素之一是以合理的方式定义接口,尤其是 FPGA 内部与其他模块连接的接口。虽然定义自己的接口可能很爽,但是还是要选择行业标准,例如 AXI 等。这样不仅能够轻松定义接口,同时确保其他开发人员在集成时能够轻松使用它们。使用行业标准还简化了接口验证,因为可以使用标准 BFM,随着时间的推移,它还会建立一个有用的 IP 模块存储库,可以在多个项目中重复使用,从而减少开发时间和同类型项目成本。

因此,该块使用 AXI Stream 通过 QSPI 接口发送和接收数据。

HDL 设计

该设计的 HDL 可以在文末看到。

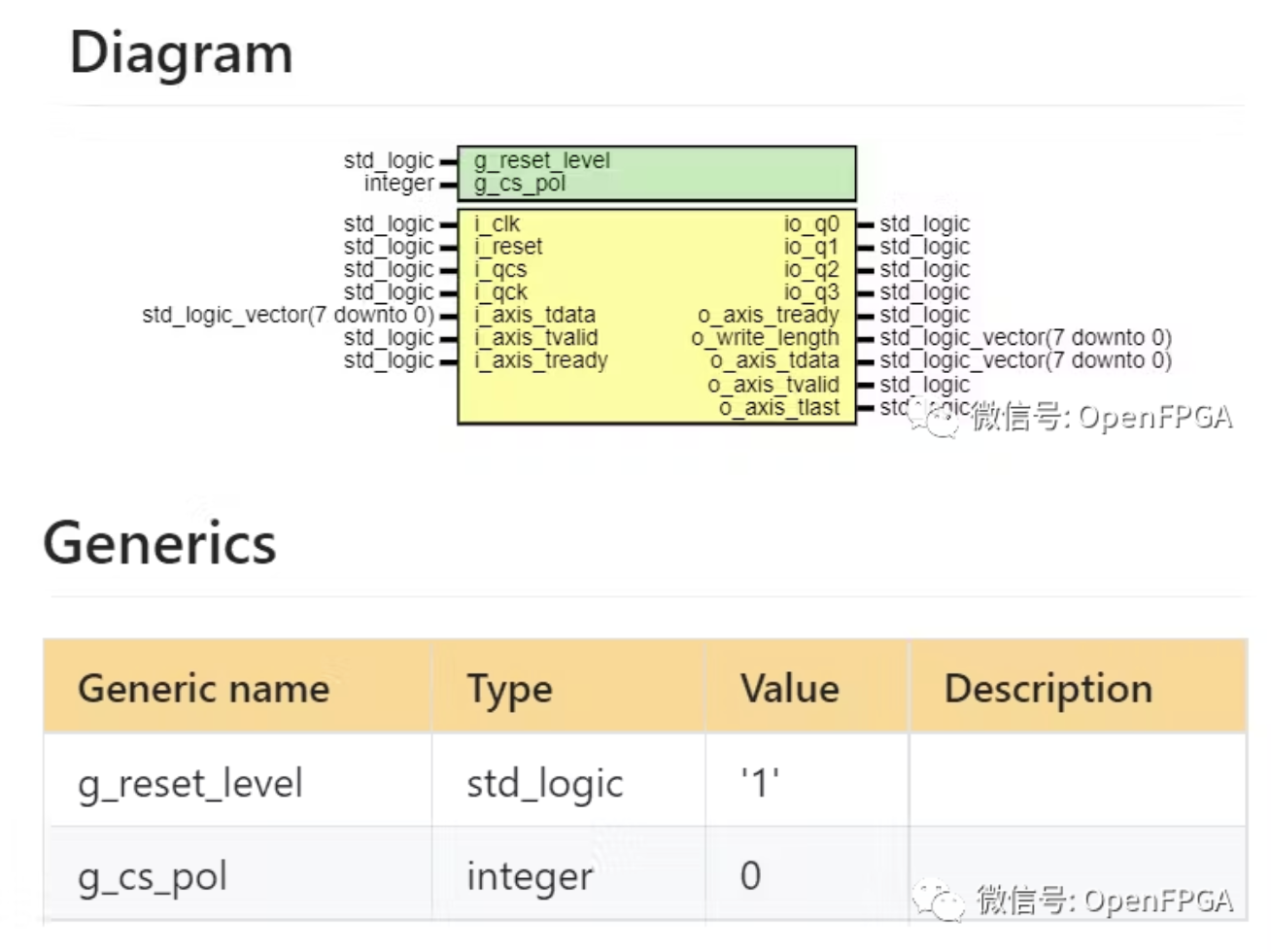

IP 的接口如下是:

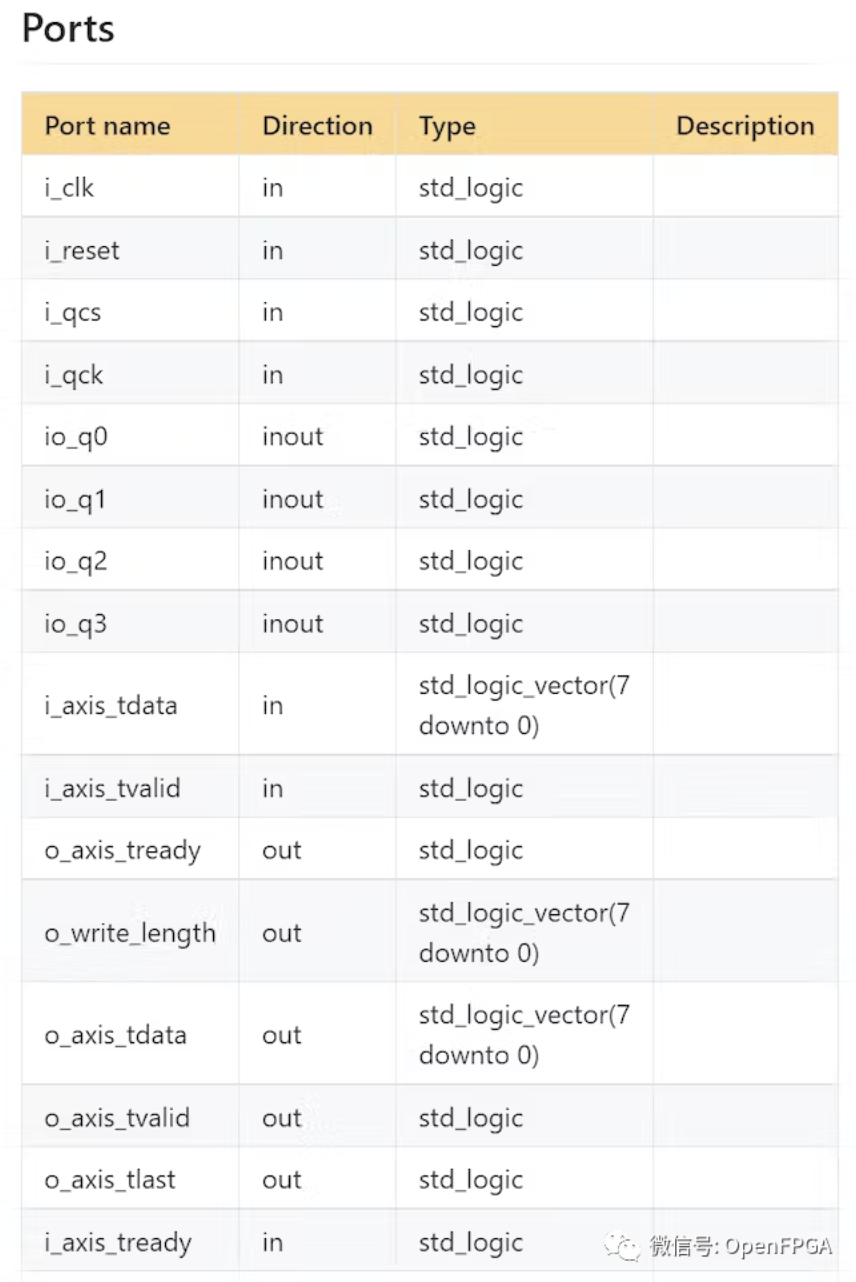

设计中的状态机:

HDL 完成后,下一步是仿真验证。

仿真

我们如何通过创建测试平台来验证 FPGA 设计是否按预期工作。测试台对被测单元 (UUT) 施加激励并观察 UUT 的输出,以确保其行为符合预期。

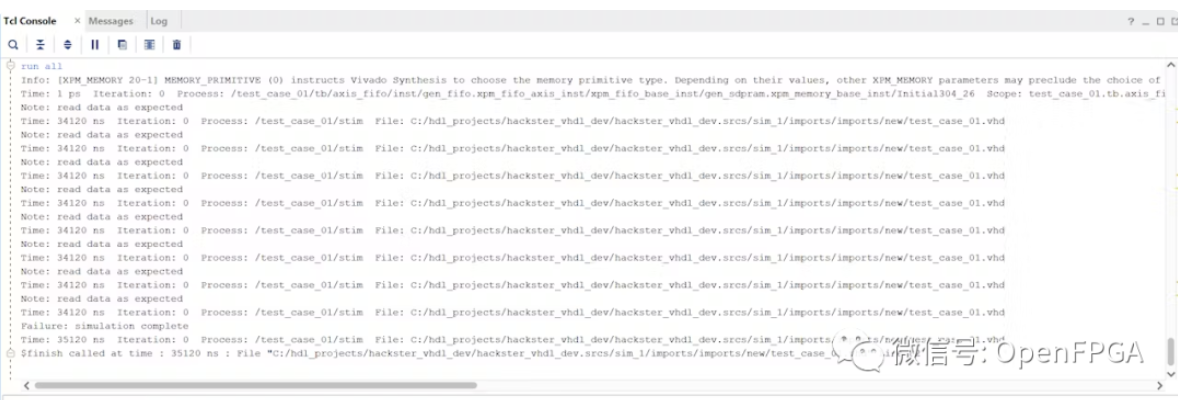

本次我们不想使用波形进行验证,我们检查 UUT 的行为并将其记录到文件中,验证其是否按照预期运行。

如果我们发现预期结果存在异常,我们再使用波形来调试 UUT。

每个测试用例都是一组独特的激励,它将特定测试应用于 UUT 以检查该激励的特定结果。

创建这些测试用例可能很复杂,并且是验证过程中最耗时的部分。根据 UUT 的复杂性,可能有少量测试用例,也可能有数十个甚至数百个。

因此,我们希望将测试平台与测试用例分开。我们使用几个不同的抽象层来实现这一目标,包括

- 测试用例 - 一个或多个测试用例,通过测试框架向 UUT 施加激励。

- 测试工具 - 包含 UUT 的映射以及 IP 模型(例如 RAMS、DDR 模型等)的连接

- UUT - 我们正在测试的单元。

为了以最简单的方式实现这一目标,我们将使用大量的总线功能模型 (BFM) 和事务级模型 (TLM)。

当然,我们可以将 UVM、UVVM 和 OSVVM 等框架用于这些应用程序,但是,由于该项目的目的是演示,因此我们将从头开始。

如果本次设计可以完美完成,将使测试用例成为一系列 BFM / TLM 级别的调用和相关检查。通过这种方式,测试用例看起来更像脚本而不是传统的 HDL 文件。

这样的灵活性非常重要,因为我们需要能够适应 UUT 功能的变化,这些变化会导致需要创建更多的测试用例。

对于此应用程序,我们有以下内容:

- 测试用例 - 应用激励 - 在这种情况下,我们有一个测试用例,其中包含一个简单的测试。

- 测试台 - 包含测试台的测试基础设施。这包括 UUT、AXIS FIFO 和时钟/复位威廉希尔官方网站 。

- UUT - 我们正在测试的 QSPI IP 核

- QSPI BFM 库 - 包含许多 BFM 的库,作为 QSPI 主设备通过接口执行读写操作。

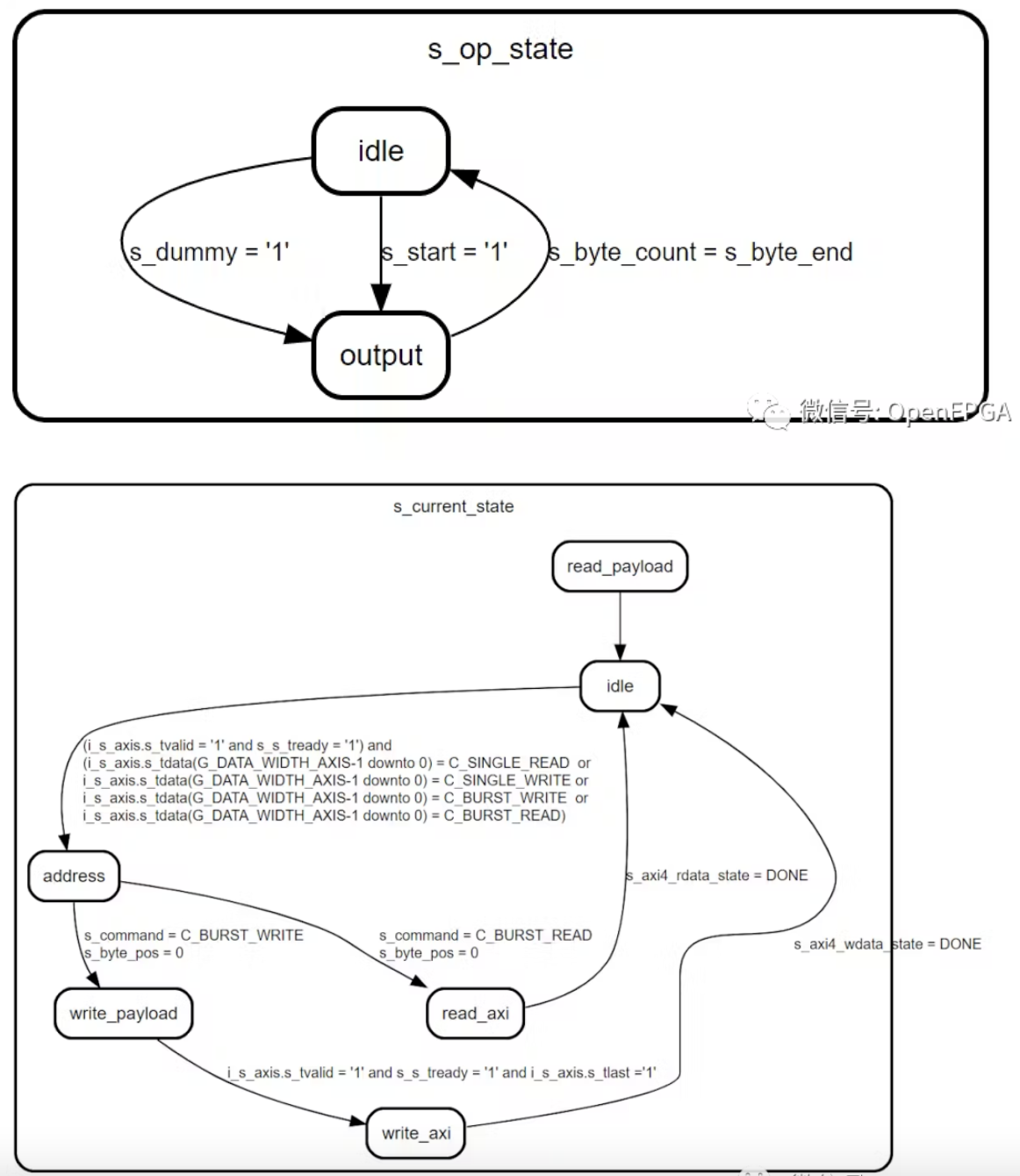

Vivado 项目

为了测试该项目,我们可以创建一个包含 HDL 和测试平台的 Vivado 项目。我们使用 Vivado 在测试台中提供 AXIS FIFO,允许循环回写入的命令,以验证读回。

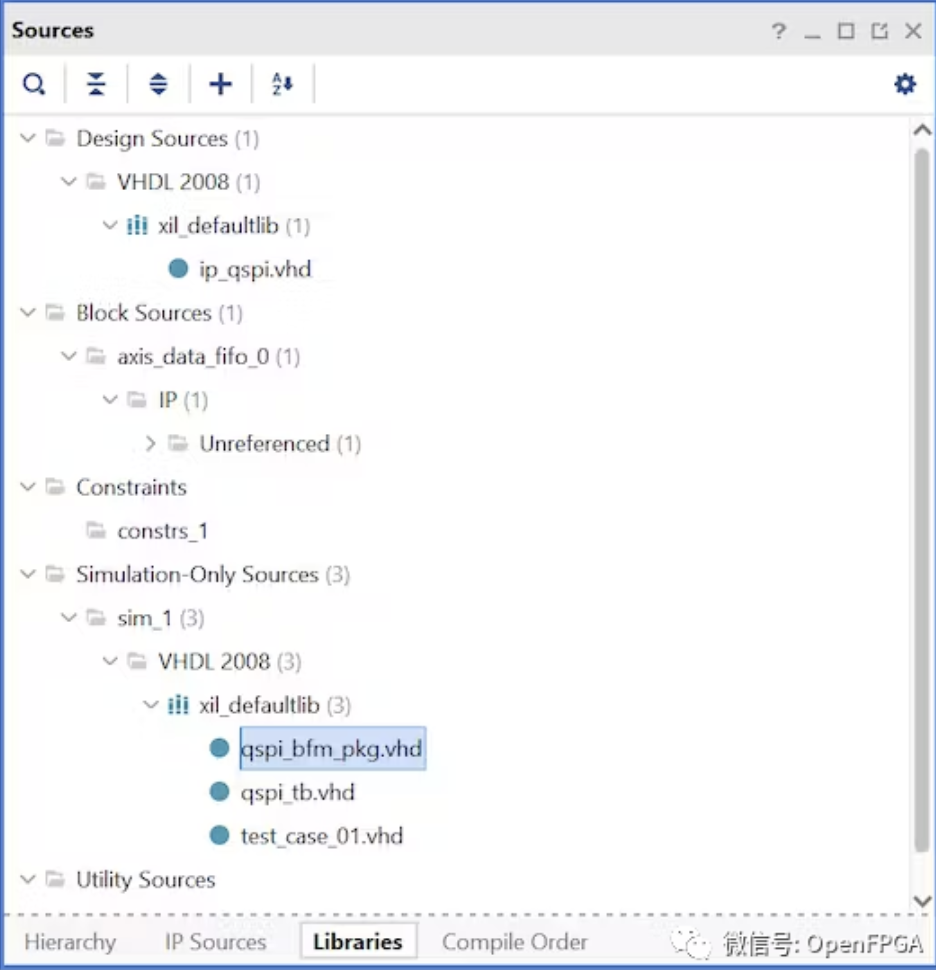

如果我们查看项目层次结构,我们将看到测试用例位于顶层的验证结构,下面的测试台包含 AXIS FIFO 和 UUT。

看不到该包,因为它仅在库视图下可用

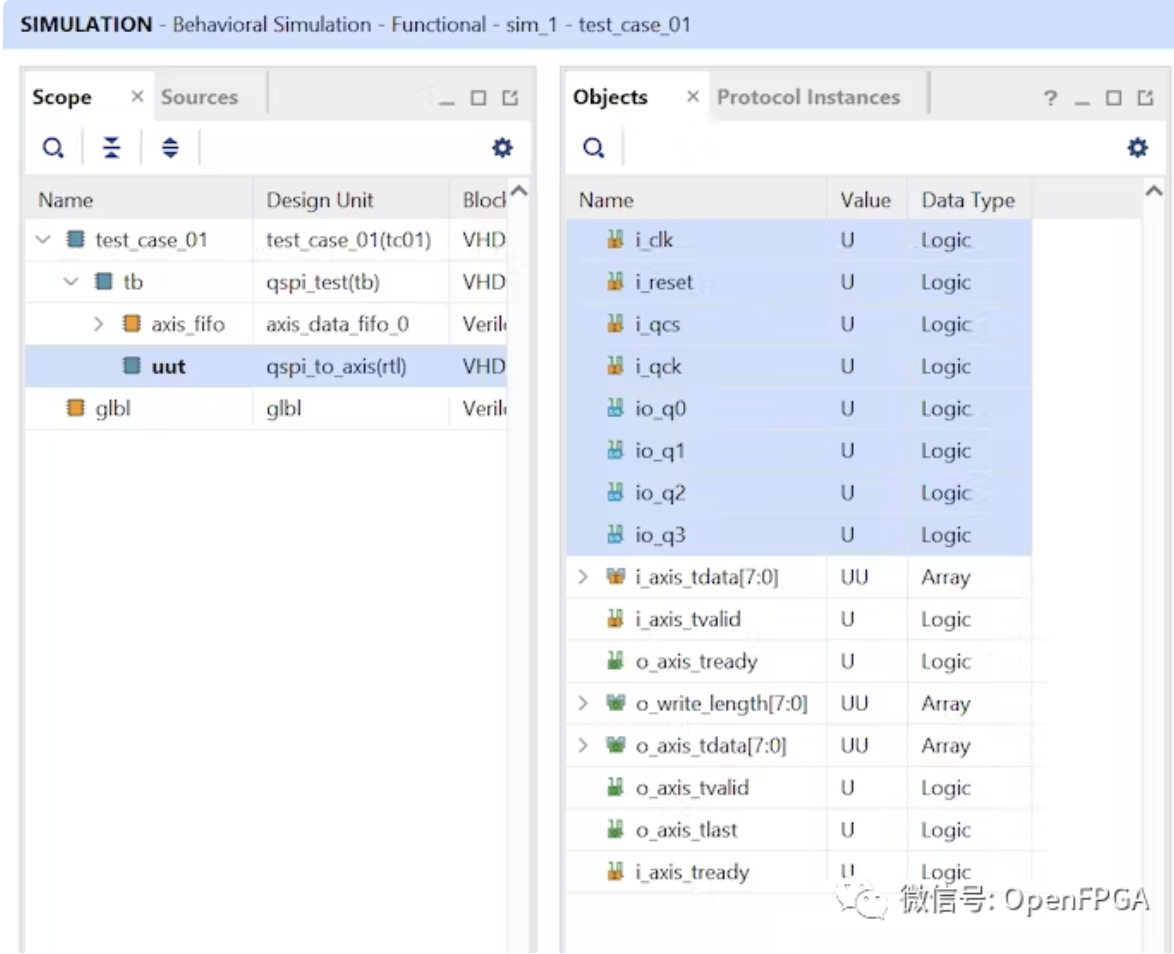

运行 HDL 行为仿真将打开波形视图。选择 UUT 并将信号添加到波形中。

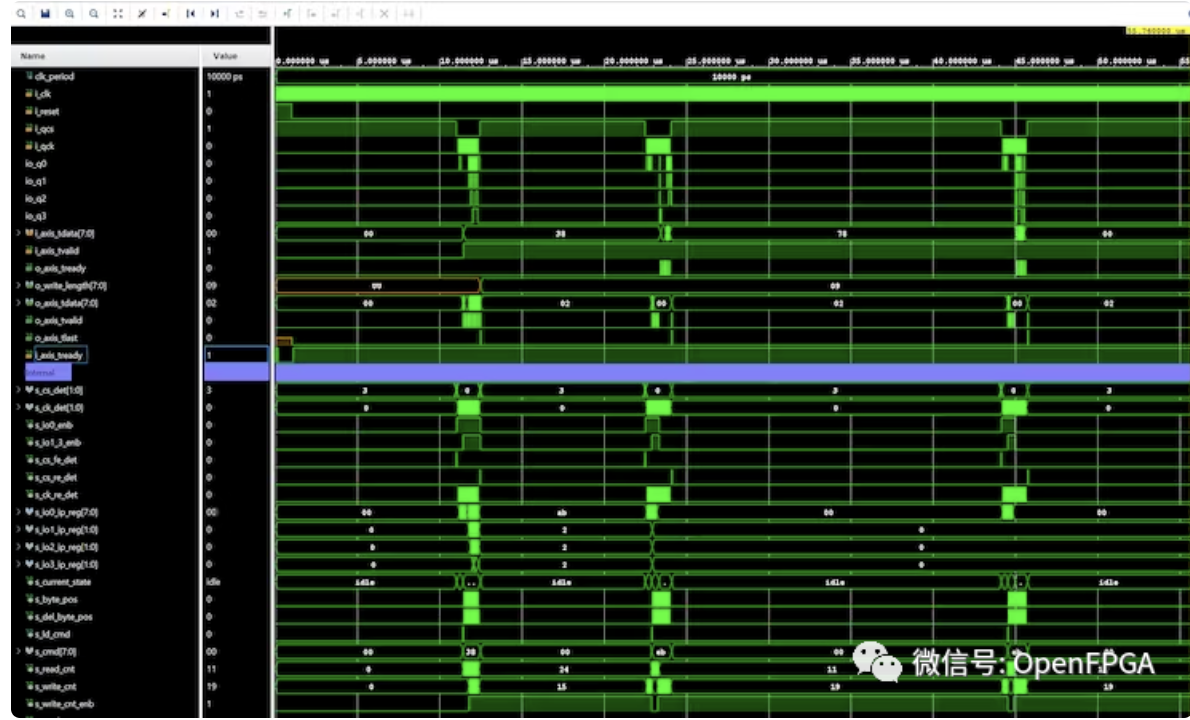

单击“run all”,仿真完成后将看到 IO 信号和内部信号的波形。

在这种情况下,我们期望的是,我们收到的每个写入值与测试平台执行此检查时返回的值相同。

对于关键应用,可能不同的工程师来执行验证并提供验证结果。

总结

在这个项目中,我们提供了 FPGA IP 核开发的流程概要。有些流程尚未涵盖,例如编码规则和静态分析等,但它为那些希望开始的人提供了很好的开端。

-

一文读懂eFPGA 选择是要注意的四个步骤2018-06-29 2283

-

FPGA IP核的相关问题2013-01-10 0

-

怎么修改别人的fpga 51ip内核的代码配套自己的能用2013-08-03 0

-

如何获得FPGA的ip地址2014-10-29 0

-

使用Vitis HLS创建属于自己的IP相关资料分享2022-09-09 0

-

使用一个FPGA构建自己的GameBoy虚拟卡带2023-09-26 0

-

FPGA中IP核的生成2015-11-30 790

-

VIVADO——IP封装技术封装一个普通的VGA IP-FPGA2017-02-28 1258

-

设计一个自己专用处理器该怎么完成?2017-05-17 4758

-

如何用DOS命令查看自己的IP地址2018-01-17 12351

-

建立用户自己的IP核2018-04-03 676

-

IP例化和几个基于FPGA芯片实现的Demo工程2020-12-24 1288

-

基于FPGA的TCP/IP协议的实现2021-04-28 1087

-

教你打包一个自己的Vivado IP核2022-02-16 2091

-

从零到一:搭建属于自己的海外IP代理池2024-11-15 382

全部0条评论

快来发表一下你的评论吧 !