基于信号完整性的电源分配系统设计

描述

在信号完整性分析中存在两类基本问题:

一类问题是与信号路径相关的反射问题和相邻路径间的串扰问题,这类问题都与信号的上升时间和时钟工作频率有关,称之为信号路径问题;

另一类问题则与信号路径无关,而是归因于电源路径和地路径,称之为电源分配系统问题,又叫电源完整性问题。

电源分配系统(PDS)的用途就是为每个用电芯片提供恒定的电压。根据用电芯片器件工艺的不同,该电压一般为5V、3.3V或2.4V,通常要求供给用电芯片的电压波动不超过5%。

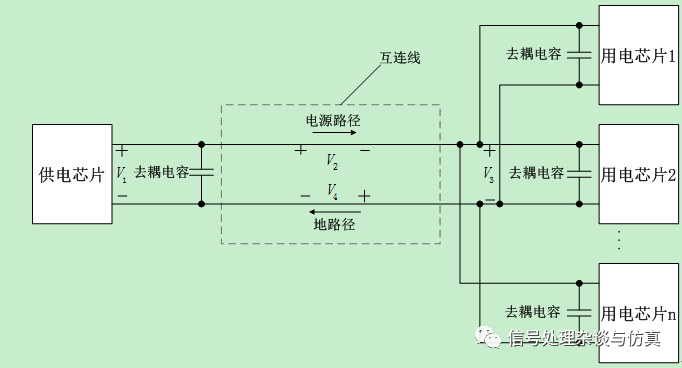

如图1所示,一个完整的PDS包括供电芯片、去耦电容、用电芯片和连接这些单元之间的互连线。

图1 电源分配系统组成

由于在PDS中,通过电源路径和地路径上的电流不可能是绝对的直流电流,都会或多或少的含有一定比例的交流电流在里边,由于在由电源路径和地路径组成的电流回路中存在回路电感L,根据V=Ldi/dt可知,交流电流会使整个电源分布路径上存在电压降,因此供给用电芯片的电压通常会降低,这问题称为轨道塌陷。

由图1可知,在电流返回路径上产生的电压降通常称为地弹噪声,地弹噪声问题是信号完整性中常见的一种问题。因此,要使电流变化引起的电压降最小,就要设法降低整个PDS的阻抗或者整个PDS电流路径的回路电感。

通常,降低整个PDS的阻抗可以分别围绕PDS的基本组成单元来进行设计。具体分为以下几个方面:

(1)在进行供电芯片和用电芯片的电源引脚及地引脚的封装设计时,尽量使由电源引脚和地引脚组成的回路电感最小。由于电源引脚和地引脚上通过的电流大小相等、方向相反,因此要减小回路电感,通常要使电源引脚和地引脚的局部自感尽量小,而电源引脚和地引脚之间的局部互感要尽量大。通常采用扁平导体带而非圆柱形金属作为封装引脚可以降低引脚的局部自感,降低电源引脚和地引脚之间的间距可以增大两者之间的局部互感。

(2)关于去耦电容的设计,通常有两条设计原则:低频时,添加阻抗值较低的去耦电容;高频时,使去耦电容与供电芯片和用电芯片焊盘之间的回路电感最小,以保证它们之间的阻抗低于一定值。

这里需要说明的是,位于供电芯片一侧的去耦电容的作用主要是为供电芯片输出的交流电流提供交流通路,从而避免电源电压的波动,这个电容典型值是10uF。

位于用电芯片一侧的去耦电容作用又因芯片种类不同而不同,用在模拟芯片一侧的去耦电容通常用于旁路电源上的高频信号,如果不加去耦电容,这些高频信号可能通过电源引脚进入敏感的模拟芯片。对于控制器和处理器这样的数字器件,同样需要去耦电容,但原因不同。这些电容的一个功能是用作“微型”电荷库。在数字威廉希尔官方网站 中由于执行门威廉希尔官方网站 状态的切换通常需要很大的电流,因而有额外的备用电荷是有利的。如果执行开关动作时没有足够的电荷,会使电源电压发生很大的变化。电源电压变化太大,会导致数字信号电平进入不确定状态,并很可能引起数字器件中的状态机错误运行。

(3)关于供电芯片和用电芯片之间互连线的设计,总的原则是使电源路径和信号路径的回路电感最小。详细情况关注笔者公众号,后续文章会进行详细分析。

总之,在以上三个方面设计中,威廉希尔官方网站 和PCB设计人员可以进行自主设计的只有后两个方面,供电芯片和用电芯片的选择更多的是出于功能性考虑,兼有一部分性能考虑,如信号完整性,电磁兼容性等。

-

信号完整性与电源完整性的仿真分析与设计2015-01-07 0

-

电源完整性PI仿真分析2020-07-07 0

-

信号完整性与电源完整性的相关资料分享2021-11-15 0

-

详解信号完整性与电源完整性2021-11-15 0

-

什么是电源和信号完整性?2021-12-30 0

-

介绍一种电源完整性的分析方法2023-04-11 0

-

电源完整性(PI)分析法2023-04-24 0

-

信号完整性与电源完整性仿真分析2011-11-30 1826

-

高速PCB电源完整性设计与分析2021-04-21 1253

-

信号完整性与电源完整性的仿真2021-09-29 1319

-

电源和信号完整性的分析与测试2022-01-07 851

-

信号完整性和电源完整性的分析2023-04-10 2413

-

如何利用全新互连系统提高电源完整性和信号完整性?2023-08-30 1197

-

信号完整性与电源完整性-电源完整性分析2024-08-12 996

全部0条评论

快来发表一下你的评论吧 !