一文详解四大芯片互连技术

电子说

描述

英特尔联合创始人戈登摩尔曾预言,芯片上的晶体管数量每隔一到两年就会增加一倍。由于图案微型化技术的发展,这一预测被称为摩尔定律,直到最近才得以实现。然而,摩尔定律可能不再有效,因为技术进步已达到极限,并且由于使用极紫外 (EUV) 光刻系统等昂贵设备而导致成本上升。与此同时,市场对不断完善的半导体技术的需求仍然很大。为了弥补技术进步方面的差距并满足半导体市场的需求,出现了一种解决方案: 先进的半导体封装技术。

尽管先进封装非常复杂并且涉及多种技术,但互连技术仍然是其核心。本文将介绍封装技术的发展历程以及 SK 海力士最近在帮助推动该领域发展方面所做的努力和取得的成就。

互连在先进封装中的重要性

首先,需要注意的是,互连技术是封装中关键且必要的部分。芯片通过封装互连以接收电力、交换信号并最终进行操作。由于半导体产品的速度、密度和功能根据互连方式而变化,因此互连方法也在不断变化和发展。

除了开发各种工艺以在晶圆厂实现精细图案外,还全面努力推进封装工艺中的互连技术。因此,开发了以下四种类型的互连技术:引线键合、倒装芯片键合、硅通孔 (TSV) 键合以及小芯片混合键合。

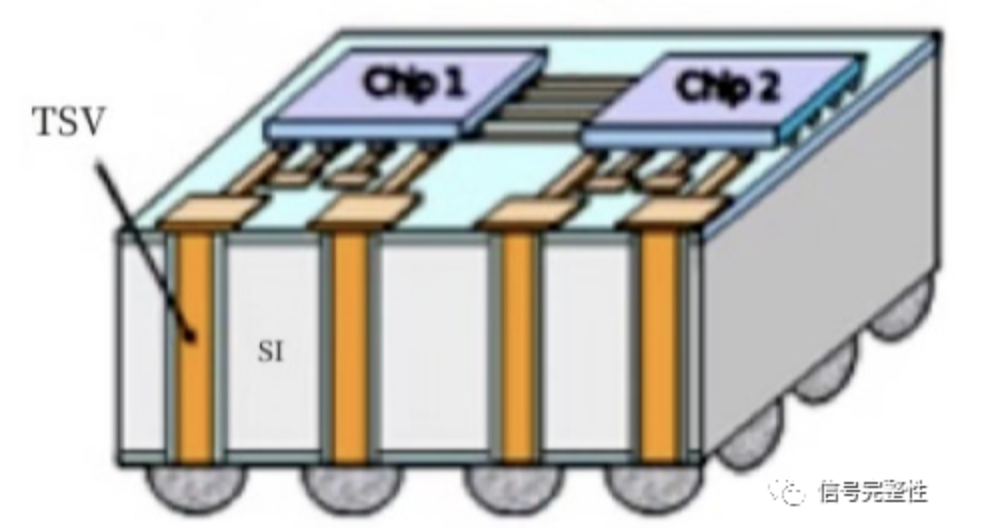

1硅通孔 (TSV):一种垂直互连通路(通孔),完全穿过硅芯片或晶圆,以实现硅芯片的堆叠。

2 Chiplet:按用途(例如控制器或高速存储器)划分芯片并将其制造为单独的晶圆,然后在封装过程中重新连接的技术。

3下述产品未采用混合键合。规格为估计值。

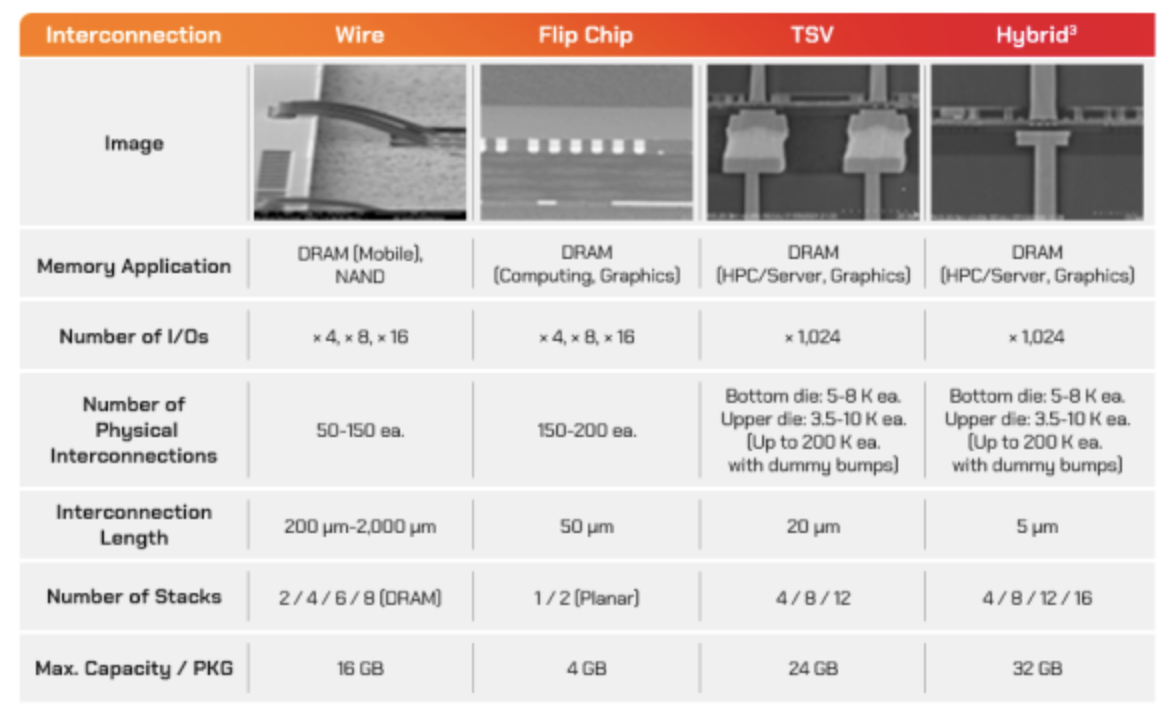

图 1. 互连方法规格表。(这些规格是应用每种互连技术的主要产品的示例。)

引线键合

引线键合是第一种开发的互连方法。通常,具有良好电性能的材料(例如金、银和铜)被用作连接芯片和基板的导线。这是最具成本效益且可靠的互连方法,但由于其电气路径较长,因此不适合需要高速操作的较新设备。因此,这种方法被用于不需要快速操作的移动设备中使用的移动 DRAM 和 NAND 芯片。

倒装芯片接合

倒装芯片接合 克服了引线键合的缺点。其电气路径的长度是引线键合的十分之几,使其适合高速操作。与在芯片级执行的引线键合相比,在晶圆级进行处理的倒装芯片键合还提供了卓越的生产率。因此,它被广泛应用于CPU、GPU和高速DRAM芯片的封装。此外,由于可以在芯片的整个侧面形成凸块,因此可以比引线键合拥有更多的输入和输出 (I/O),从而有可能提供更高的数据处理速度。然而,倒装芯片接合也有其自身的缺点。首先,难以进行多芯片堆叠,这对于需要高密度的存储产品来说是不利的。此外,尽管倒装芯片键合可以比引线键合连接更多的 I/O,和有机 PCB 间距阻止连接更多数量的 I/O。为了克服这些限制,开发了 TSV 键合技术。

硅通孔 (TSV) 键合

TSV不采用传统的布线方法来连接芯片与芯片,而是通过在芯片上钻孔并填充金属等导电材料以容纳电极来垂直连接芯片。制作带有TSV的晶圆后,通过封装在其顶部和底部形成微凸块,然后连接这些凸块。由于 TSV 允许凸块垂直连接,因此可以实现多芯片堆叠。最初,使用 TSV 接合的堆栈有四层,后来增加到八层。最近,一项技术使得堆叠 12 层成为可能,并于 2023 年 4 月SK hynix 开发了其 12 层 HBM3。虽然 TSV 倒装芯片接合方法通常使用基于热压的非导电薄膜 (TC-NCF),但 SK hynix 使用 MR-MUF 4 工艺,可以减少堆叠压力并实现自对准。5这些特性使 SK hynix 能够开发出世界上第一个 12 层 HBM3。

4大规模回流模塑底部填充(MR-MUF):将半导体芯片堆叠起来,并将液体保护材料注入芯片之间的空间,然后硬化以保护芯片和周围威廉希尔官方网站 的工艺。与在每个芯片堆叠后应用薄膜型材料相比,MR-MUF 是一种更高效的工艺,并提供有效的散热。

5自对准:在 MR-MUF 工艺期间通过大规模回流将芯片重新定位到正确的位置。在此过程中,热量被施加到芯片上,导致相关凸块在正确的位置熔化并硬化。

如上所述,引线、倒装芯片和 TSV 键合在封装工艺的各个领域中发挥着各自的作用。尽管如此,最近出现了一种新的互连技术,称为铜对铜直接键合,它是混合键合的一种。

与小芯片的混合键合

术语“混合”用于表示同时形成两种类型的界面结合6。界面结合的两种类型是:氧化物界面之间的结合和铜之间的结合。这项技术并不是新开发的技术,但多年来已经用于 CMOS 图像传感器的大规模生产。然而,由于小芯片的使用增加,它最近引起了更多关注。Chiplet技术将各个芯片按功能分离,然后通过封装将它们重新连接起来,在单个芯片上实现多种功能。

6界面键合:相互接触的两个物体的表面通过分子间力结合在一起的键合。

尽管小芯片的功能是该技术的一个明显优势,但采用它们的主要原因是成本效益。当所有功能都在单个芯片上实现时,芯片尺寸会增加,并且不可避免地导致晶圆生产过程中良率的损失。此外,虽然芯片的某些区域可能需要昂贵且复杂的技术,但其他区域可以使用更便宜的传统 技术来完成。因此,由于芯片无法分离,制造工艺变得昂贵,因此即使只有很小的面积需要精细技术,也要将精细技术应用于整个芯片。然而,小芯片技术能够分离芯片功能,从而可以使用先进或传统的制造技术,从而节省成本。

虽然chiplet技术的概念已经存在十多年了,但由于缺乏能够互连芯片的封装技术的发展,它并没有被广泛采用。然而,芯片到晶圆 (C2W) 混合键合的最新进展显着加速了小芯片技术的采用。C2W 混合键合具有多种优势。首先,它允许无焊料键合,从而减少键合层的厚度、缩短电气路径并降低电阻。因此,小芯片可以高速运行而无需任何妥协——就像单个芯片一样。其次,通过直接将铜与铜接合,可以显着减小凸块上的间距。目前,使用焊料时很难实现 10 微米 (μm) 或更小的凸块间距。然而,铜对铜直接键合可以将间距减小到小于一微米,从而提高芯片设计的灵活性。第三,它提供了先进的散热功能,这一封装功能在未来只会继续变得越来越重要。最后,上述的薄粘合层和细间距影响了封装的形状因数,因此可以大大减小封装的尺寸。

然而,与其他键合技术一样,混合键合仍然需要克服挑战。为了确保稳定的质量,必须在纳米尺度上改进颗粒控制,而控制粘合层的平整度仍然是一个主要障碍。同时,SK海力士计划使用最高功率的封装解决方案来开发混合键合,以便将其应用于未来的HBM产品。

利用 SK 海力士的混合键合推进封装技术

虽然SK海力士目前正在开发混合键合,以应用于其即将推出的高密度、高堆叠HBM产品,但该公司此前已在2022年成功为HBM2E采用混合键合堆叠八层,同时完成电气测试并确保基本可靠性。这是一项重大壮举,因为迄今为止大多数混合键合都是通过单层键合或两个芯片面对面堆叠来完成的。对于 HBM2E,SK 海力士成功堆叠了 1 个基础芯片和 8 个 DRAM 芯片。

混合键合是封装行业中最受关注和关注的键合技术。集成器件制造商、代工厂以及任何能够生产先进封装的公司都专注于混合键合。如上所述,尽管该技术具有众多优势,但仍有很长的路要走。通过其领先的 HBM技术,SK海力士将开发除混合键合之外的各种封装技术,以帮助封装技术和平台解决方案达到前所未有的水平。

-

芯片封装键合技术各种微互连方式简介教程2012-01-13 0

-

请问Ultrascale FPGA中单片和下一代堆叠硅互连技术是什么意思?2020-04-27 0

-

光互连技术2016-01-29 0

-

视频图像处理的四大技术2016-07-23 0

-

一文详解芯片逆向工程的设计与流程2018-09-14 0

-

LoRa天线威廉希尔官方网站 设计四大要点2021-12-07 0

-

一文了解赛灵思四大技术趋势2018-06-29 3743

-

RFID标签的四大主流应用场景2019-08-20 11862

-

小米电视官方详解电视芯片Amlogic T972,共具有四大“杀手锏”2019-09-27 53965

-

一文详解精密封装技术2022-12-30 1667

-

一文详解半导体封装的封装互连技术2023-02-20 1672

-

一文详解封装互连技术2023-04-03 5165

-

一文详解pcb和smt的区别2023-10-08 3359

-

一文详解pcb的msl等级2023-12-13 9693

-

一文详解硅通孔技术(TSV)2024-01-09 16899

全部0条评论

快来发表一下你的评论吧 !