借助GPT4理解仿真中竞争处理的方法

描述

上周微信群里的一个小伙伴提到的一个关于仿真中不达预期的一个问题,其中牵涉到关于仿真中信号竞争等问题。这个问题之前算是不求甚解。这周经一位大佬的提点,结合GPT4的帮助,来好好梳理下这个问题。

由于本人对底层不求甚解,仅做总结与梳理,真实细节还需扒代码底层,有感兴趣的可自行去探索。

不得不说科技改变生活,GPT确实强大。

不达预期的仿真行为

先来看一个简单的威廉希尔官方网站 :

case class Test() extends Component {

val pc=out UInt(8 bits) setAsReg() init(0)

val inst=in UInt(8 bits)

pc:=pc+1

}

小伙儿的需求很简单。在仿真中根据当前的pc值加1后反馈给inst输入引脚。不假思索即可写出下面的仿真代码:

object TestApp extends App {

SimConfig.withFstWave.compile(bootTest()).doSim{dut=>

dut.clockDomain.forkStimulus(10)

fork{

while(true){

dut.clockDomain.waitSampling()

dut.inst#=dut.pc.toInt+1

}

}

dut.clockDomain.waitSampling(10)

}

}

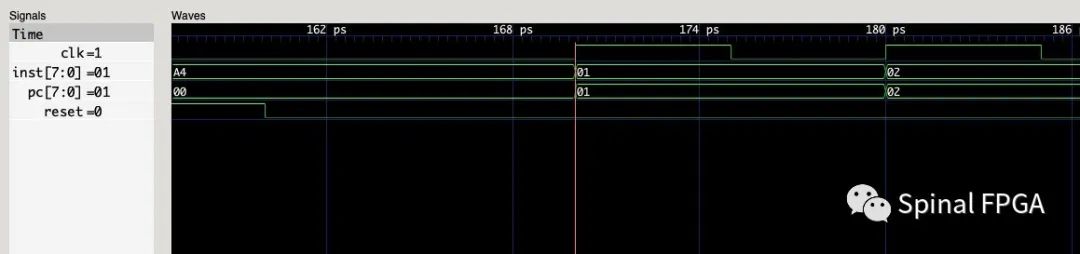

看起来没啥毛病是吧,时钟上升沿之后将pc+1驱动给dut.inst。然而仿真结果却并不如人意:

按照正常的理解,这里面inst的值应该等于pc的值加1才行对吧,然而仿真波形却显示inst的值和pc的值一致。仿真器脑抽了?

在执行inst赋值前加上一行打印:

object TestApp extends App {

SimConfig.withFstWave.compile(bootTest()).doSim{dut=>

dut.clockDomain.forkStimulus(10)

fork{

while(true){

dut.clockDomain.waitSampling()

println(s"time:${simTime()} pc:${dut.pc.toInt} isnt_in:${dut.inst.toInt} clk:${dut.clockDomain.clockSim.toBoolean}")

dut.inst#=dut.pc.toInt+1

}

}

dut.clockDomain.waitSampling(10)

}

}

仿真执行时打印信息如下:

time:170 pc:0 isnt_in:64 clk:true time:180 pc:1 isnt_in:1 clk:true time:190 pc:2 isnt_in:2 clk:true time:200 pc:3 isnt_in:3 clk:true time:210 pc:4 isnt_in:4 clk:true time:220 pc:5 isnt_in:5 clk:true time:230 pc:6 isnt_in:6 clk:true time:240 pc:7 isnt_in:7 clk:true time:250 pc:8 isnt_in:8 clk:true

这就有点意思了,在170时刻,明明clk已经是高电平,按道理来时钟上升沿已然产生,然而pc打印出来的值仍然是0!

先说这里如何修复这个问题,你只需添加一个sleep(0):

object TestApp extends App {

SimConfig.withFstWave.compile(bootTest()).doSim{dut=>

dut.clockDomain.forkStimulus(10)

fork{

while(true){

dut.clockDomain.waitSampling()

sleep(0)

println(s"time:${simTime()} pc:${dut.pc.toInt} isnt_in:${dut.inst.toInt} clk:${dut.clockDomain.clockSim.toBoolean}")

dut.inst#=dut.pc.toInt+1

}

}

dut.clockDomain.waitSampling(10)

}

}

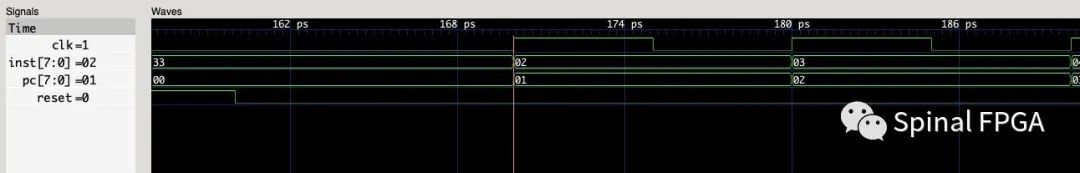

如此,即可符合仿真预期:

Log打印:

time:170 pc:1 isnt_in:51 clk:true time:180 pc:2 isnt_in:2 clk:true time:190 pc:3 isnt_in:3 clk:true time:200 pc:4 isnt_in:4 clk:true time:210 pc:5 isnt_in:5 clk:true time:220 pc:6 isnt_in:6 clk:true time:230 pc:7 isnt_in:7 clk:true time:240 pc:8 isnt_in:8 clk:true time:250 pc:9 isnt_in:9 clk:true

如果觉得能用即可,那么针对这种问题看到这里就可以了~

审核编辑:刘清

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

FRED在背光板仿真中的应用2010-12-22 751

-

电子元器件在威廉希尔官方网站 仿真中如何建模2010-04-12 12070

-

saber仿真中的问题处理方法2011-04-21 12792

-

PSpice教程:PSpice仿真中收敛问题的研究2013-04-07 1141

-

三菱PLC模拟仿真中文软件2016-01-14 1645

-

浅谈ChatGPT的最新“升级版本”——GPT4模型2023-03-22 3091

-

用GPT4搞电机?2023-04-06 1416

-

GPT4做Leetcode的能力2023-04-28 2305

-

GPT-4 的模型结构和训练方法2023-05-22 2637

-

你考虑用GPT4搞电机吗?2023-07-05 346

-

gpt-4怎么用 英特尔Gaudi2加速卡GPT-4详细参数2023-07-21 870

-

chatGPT和GPT4有什么区别2023-08-09 3104

-

ChatGPT Plus怎么支付 GPT4得订阅吗?2023-10-10 1781

-

MATLAB威廉希尔官方网站 仿真中能讲电流汇总的元件2024-04-21 3287

-

股价久违飙涨,商汤要用自己的Scaling law挑战GPT42024-05-08 276

全部0条评论

快来发表一下你的评论吧 !