关于MUX时序约束的两个例子

电子说

描述

在不同的资料上看到关于MUX 的时序约束的两个示例,分享一下

例子1

一、MUX前没有逻辑威廉希尔官方网站 的时钟结构

时钟设计的一般原则是在靠近时钟源头的地方将各种所用频率时钟都产生,再引给内部逻辑使用,并且最好用一个模块单独处理,所以两个输入时钟一般来自端口输入或PLL输出,在经过MUX前不驱动任何数字逻辑;

首先创建两个源时钟:

create_clock –name clk1 –period $clk_period $clk1_src_pin –add

create_clock –name clk2 –period $clk_period $clk2_src_pin –add

对于MUX后面的约束,分为同步异步两种情况分开讨论:

异步

如果MUX的两个输入时钟是MUX后都可以不创建生成时钟,工具基于两个时钟分别进行时序分析,只需用set_clock_groups设定一下两个时钟的异步关系:

set_clock_groups –asynchronous –name clk_async –group “clk_1” –goup “clk2”

同步

对于MUX的两个输入时钟同步的情况,可以抽象成如下的结构:

由于时钟只能穿过时序逻辑,对于时序逻辑的输出,STA工具认为是数据,所以分频reg的Q端必须要创建分频时钟;

由于该时钟定义点是时序器件,此时不能加-comb选项:

create_generated_clock –name clk_div $clk_div_pin –divide_by N –master clk_src –source $clk_src_pin –add

对于MUX后面的约束,存在以下几种约束方法:

1.MUX后面不创建生成时钟

由于MUX任何时候只能让一路通过,MUX后可不创建时钟,此时将clk_scr和clk_div设置为logical_exclusive即可;

set_clock_groups –logical_exclusive –name clk_div_logi_async –group “clk_src” –goup “clk_div”

由于时钟树的Last common point在MUX后,PT(prime time)会自动进行CRPR补偿,即使不设逻辑互斥,根据PT的分析结果看,也不会引入悲观分析;

2.MUX后创建一个生成时钟

由于clk_src的频率更高,所以以clk_scr为master_clock

此时加与不加-comb的区别:

(a)加-comb选项

create_generated_clock –name clk_mux0_clk_scr $mux_y_pin –devide_by 1 –master clk_scr –source $clk_scr_pin –add –comb

此时工具在追clk_mux0_clk_scr的source时会强制走组合路径,即通过MUX/I0,PT计算clock latency的时候MUX只分析MUX/I0;

(b)不加-comb选项

对于clk_mux0_clk_src这个生成时钟,PT计算其时钟树延迟(clock latency)时,会分别计算MUX的两个输入路径,选择对时序结果更悲观的,会引入过度的悲观;

在进行setup检查时,对capture clock latency计算会采用ckl_src → MUX/I0这条路径;在进行hold检查时,对capture clock latency 计算会采用ckl_src → DIV_N → MUX/I1的路径;对于launch 时钟latency的计算也会出现上述情况;

3.MUX后创建两个生成时钟

MUX后创建两个生成时钟,并且设physical_exclusive,这是更常见的做法

create_generated_clock –name clk_mux0_clk_scr $mux_y_pin –devide_by 1 –master clk_scr –source $clk_scr_pin –add –comb

create_generated_clock –name clk_mux1_clk_div $mux_y_pin –devide_by N –master clk_div –source $clk_div_pin –add

set_clock_groups –pysical_exclusive –name clk_mux_phy_async –group “clk_mux0_clk_scr” –goup “clk_mux1_clk_div”

二、MUX前有逻辑威廉希尔官方网站 的时钟结构

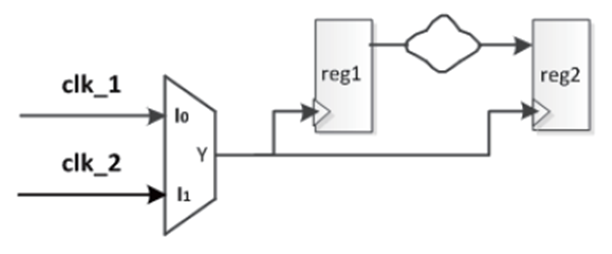

如下图:时钟源clk_src在MUX前已经驱动部分逻辑,又对此时钟进行分频和选择,后面逻辑reg1、reg2的时钟需要切换,而且reg0跟reg1、reg2之间有路径交互;

1.上述第一种约束方法,即MUX后面不创建生成时钟

会存在将reg0和reg1设成异步的问题,导致部分同步路径没有进行时序检查;

当MUX/I1选通的时候,reg0的时钟为clk_src,reg1的时钟为clk_div,而这两个clk是logical_exclusive的;

2.上述第二种约束方法,即MUX后面只创建一个生成时钟

由于生成时钟的master_clock设为I0传来的clk_src,会将I1传来的clk_div时钟挡住,工具无法用clk_div时钟进行分析和优化;

此时所有时钟树的Last common point在MUX前,工具无法进行 CRPR 补偿;

此时加与不加-comb的区别:

(a)加-comb选项

对于从reg0到reg1这条timing path的capture clock latecy,工具只会去分析经过MUX/I0的情况;

当MUX切换到I1时,由于经过寄存器DIV_N分频的路径一般比MUX/I0的路径延时要长,reg1的时钟树可能变长,这就可能导致setup不满足时序要求;

(b)不加-comb选项

同样对于reg0到reg1这条timing path,工具按照悲观原则去分析;

3.上述第三种约束方法,即MUX后面创建两个个生成时钟

虽然麻烦,但是最准确;

4.方法四

除了上述三种方法外,还有一种方法;如下图所示,在MUX/I0这一路插入一个buffer,在buffer后面创建一个生成时钟,然后和clk_div设置logical exclusive即可,MUX后面不需要再创建时钟;

create_generated_clock –name clk_buffer $buffer_pin –devide_by 1 –master clk_src –source $clk_src_pin –add

set_clock_groups –logical_exclusive –name clk_buffer_div_logi_async –group “clk_buffer” –goup “clk_div

5.更复杂的情况

如果是比上述更复杂的情况,例如下图,DIV_N还有一路单独驱动reg3;对于这种结构,上述方法(4)就不适用了,因为当MUX选择I0的时候,存在reg2和reg3为异步的问题;

总结

正确的约束,能让工具看到正确的路径;

但是当clk_src到MUX的两个输入延时几乎一致的时候,工具无论选择走哪路,差别都很小,也就几乎不会影响时序检查的结果了;所以威廉希尔官方网站 真正实现还是要靠将两路做等长;

因此,尽量将时钟产生逻辑放在一个模块里面,且尽量放在功能逻辑之前;

例子2

如下图这个例子:

约束1

create_clock -period 10 CLK

create_generated_clock -name CLKdiv2 -divide_by 2 UMUX/Y -source FFdiv2/CK –master CLK –add

create_generated_clock -name CLKdiv4 -divide_by 4 UMUX/Y -source FFdiv4/CK -master CLK –add

set_clock_groups -physically_exclusive -group {CLK} -group {CLKdiv2} –group {CLKdiv4}

这样约束会有几个问题:

(a)timing report中缺少master clock的group

这是因为每个create_generated_clock约束都会覆盖该点存在的任何其他时钟,除非它们也在该点创建了生成时钟并使用 -add 选项;

(b)Clock Source Latency Path问题

例如一条从FF1到FF2的setup timing path:launch path经过UMUX/C,capture path经过UMUX/A,如示例一中所述,悲观分析了;

这是因为create_generated_clock的-source选项指定的pin/port处,工具会查找上面存在的所有Clock以及它的相位关系,然后来确定哪个是master clock以及它的相位和generatedclock是否满足定义的相位关系(同相或反相),但它不会控制source latency path;

尽管我们为CLKdiv2_mux指定了“ -source FFdiv2/CK”,但它不会强制source latency path通过该引脚。相反,PT观察到在引脚FFdiv2/CK处存在与generated clock同相位的时钟CLK。然后,工具将搜索所有可能的同相路径,使其返回时钟源CLK,时钟源是名为CLK的输入端口;

由于这些是setup路径,因此返回输入端口CLK的最慢同相路径是通过FFdiv4的路径,最快的同相路径是通过未分频的路径;

约束2

引导生成时钟的source latency路径的最佳方法是直接在分频reg的Q创建生成时钟;

create_clock -period 10 CLK

create_generated_clock -name CLKdiv2 -divide_by 2 FFdiv2/Q -source FFdiv2/CK

create_generated_clock -name CLKdiv4 -divide_by 4 FFdiv4/Q -source FFdiv4/CK

set_clock_groups -physically_exclusive -group {CLK} -group {CLKdiv2} –group {CLKdiv4}

约束3(crosstalk问题)

在上面的约束中,CLKdiv2和CLKdiv4不会同时出现,因此PT也不会分析他们之间的SI(物理互斥不会计算SI);然而在这两个时钟在MUX前是可以同时出现的;

修改约束如下:

create_clock -period 10 CLK

create_generated_clock -name CLKdiv2 -divide_by 2 FFdiv2/Q -source FFdiv2/CK

create_generated_clock -name CLKdiv4 -divide_by 4 FFdiv4/Q -source FFdiv4/CK

create_generated_clock -name CLK_mux -combinational UMUX/A -source UMUX/A

create_generated_clock -name CLKdiv2_mux -combinational UMUX/B -source UMUX/B

create_generated_clock -name CLKdiv4_mux -combinational UMUX/C -source UMUX/C

set_clock_groups -physically_exclusive

-group {CLK_mux}

-group {CLKdiv2_mux}

-group {CLKdiv4_mux}

-

关于时序约束2015-02-03 0

-

请教时序约束的方法2012-07-04 0

-

学习时序约束 遇到的问题,求助2014-03-20 0

-

关于时序约束的文件2014-07-17 0

-

时序约束与时序分析 ppt教程2010-05-17 773

-

FPGA时序约束方法2015-12-14 824

-

FPGA中的时序约束设计2017-11-17 2560

-

时序约束的步骤分析2019-12-23 2152

-

Vivado进行时序约束的两种方式2020-03-08 19621

-

时序约束中如何精确找到匹配的template?2021-04-10 1981

-

两个例子讲解现场压力变送器应急调校方法,加深理解资料下载2021-04-27 1505

-

VIVADO时序约束及STA基础2022-03-11 9747

-

约束、时序分析的概念2023-05-29 784

-

浅谈时序设计和时序约束2023-07-04 1403

-

深度解析FPGA中的时序约束2024-08-06 652

全部0条评论

快来发表一下你的评论吧 !