车载以太网交换机硬件设计指南

描述

SJA1105P/Q/R/S 系列是 NXP 推出的一款 5 端口车载以太网交换机,支持IEEE 音视频桥接(AVB)和时间敏感网络(TSN)标准。这五个端口中的每一个都可以单独配置为 10/100/1000 Mbit/s 运行。

芯片介绍

1.1 概述

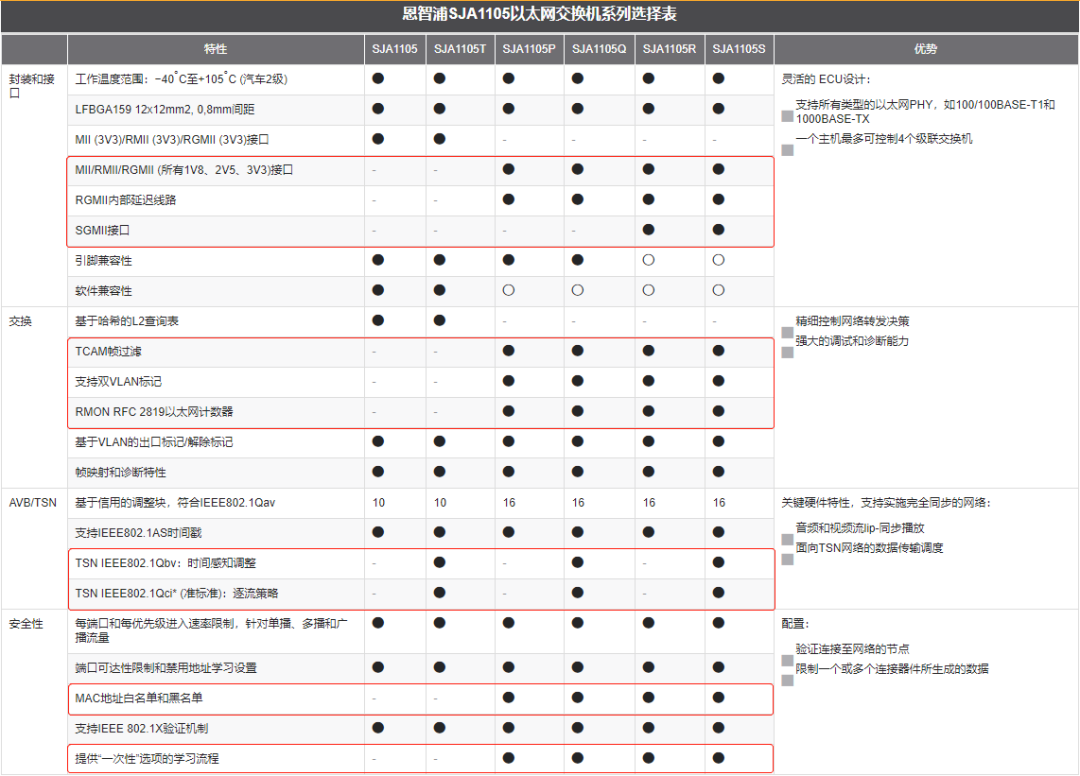

SJA1105PEL/QEL/REL/SEL 系列是一款汽车千兆以太网交换机,相较于 SJA1105EL/TEL,其扩展了交换机的功能,改进了安全特性,扩展了接口选项,具体区别如图:

SJA1105P/Q/R/S 系列中 P/Q 版本不带 SGMII 接口(本文设计指导基于 P/Q 版本),具体区别如下图:

1.2 基本特征

① 基于帧头的安全特性

a. 根据具体帧头值划分的帧黑名单和白名单

b. 防止转发错误或恶意数据

c. 支持实施防火墙应用

② 5 个可单独配置的端口,带有扩展 IO 选项

a. 广泛的数据传输速率,可优化 PCB 设计

b. SGMII 选项用于 EMC 友好型千兆位接口

c. 可灵活地连接至 10/100/1000 BASE-T1/TX 光 PHY

③ 全面支持音频/视频桥接和时间同步

a. 实施完全同步的网络

b. 支持汽车领域大多数 AVB /TSN 特性

c. 由恩智浦或第三方软件厂商提供的 AVB 软件

1.3 封装及引脚信息

① 封装: SJA1105P/Q/R/S 系列封装均为 LFBGA159(SOT1427-1),且兼容 SJA1105、SJA1105T,具体封装参数如图:

② 引脚定义:

硬件设计指南

1.1 电源设计

① VDD_CORE、VDDA_OSC、VDDA_PLL 的电源输入拓扑如图所示:(建议在每一路电源上增加一个铁氧体磁珠及两个电容组成一个 PI 型滤波)

② VDDIO_MIIx 的电源输入拓扑如图所示:(建议在每一路电源上增加一个铁氧体磁珠及两个电容组成一个 PI 型滤波)

所有 xMII-port 端口需根据其模式配置提供相应的电源(1.8V/2.5V/3.3V)。

没有使用的端口,其 VDDIO_MIIx 电源可以直接连接到地面,以节省电力。也可以选择在核心电源处于活动状态时动态关闭各个端口的电源。但是 VDDIO_MIIx 不能悬空。

③ VDDIO_HOST、VDDIO_CLO 的电源输入拓扑如图所示:(建议在每一路电源上增加一个铁氧体磁珠及两个电容组成一个 PI 型滤波)

VDDIO_HOST 和 VDDIO_CLO 都可以接受 1.8 V、2.5 V 或 3.3 V 的电源。SPI、JTAG 和PTP_CLK 接口通过 VDDIO_HOST 提供。25 MHz 时钟输出、CLK_OUT 由 VDDIO_CLO 提供。独立的供电引脚和各种电压搭配为不同的接口电压兼容提供了灵活性。

重要的是,提供 VDDIO_HOST 的域也提供给了附加的微处理器的 SPI 接口。这保证了SDO 和 SDI 引脚上的电压是从 VDD_HOST 派生的。在任何情况下,需确保 VDDIO_HOST 上电之前 SPI 的输入引脚(SDI, CS)没有电平。

2.2 接口设计

① MII/RMII/RGMII 接口

未使用的 xMII 接口应该有固定状态,输入端不能悬空,特别是所有 RX 输入都应连接到 GND。或者也可以通过内部上/下拉(见 ACU 寄存器)来定义引脚状态。

输出端(TX pins)可以悬空。

MII/RMII/RGMII 接口设计要求:

a. 单端 50 Ω 阻抗控制。

b. 组间等长控制

c. 建议将时钟和数据信号走内层,以减少辐射发射。

② SPI 接口

SJA1105PQRS 通过 SPI 连接到主机控制器上进行初始配置和时钟调整,并进行一般管理,其工作在从机模式。SPI 接口可以在 3.3 V、2.5 V 或 1.8 V 的电源电压下工作,这取决于 VDDIO_HOST 电源。SPI 的时钟最大支持到 25 MHz。

SPI 设计要求:

a. 单端 50 Ω 阻抗控制。

b. 推荐组间等长(SCK,SDI,SDO,SS_N)

2.3 时钟设计

SJA1105PQRS 支持晶体输入(振荡模式)和外部时钟输入(时钟模式)作为参考时钟。

① 晶体模式

选择晶体和负载电容的基本原则是确保其振荡频率稳定在 25mhz±50ppm 的容差范围内(针对 RMII 和 RGMII),如果所有端口都工作在 MII 模式,则为 25mhz±100ppm。

建议在默认配置下使用两个 10pf 陶瓷电容器。电容值可能随晶振规格和板级测试结果而变化。当晶振被用作时钟源时,需要尽可能的将晶振靠近 SJA1105PQRS 放置以减小 EMI 影响。

② 时钟模式

SJA1105PQRS 支持 AC-coupled(没有外部电压偏置)的外部 25MHz 时钟输入至 OSC_IN 引脚,此时 OSC_OUT 引脚保持悬空,这种应用下需要串接 100 pF 的电容。

注意 OSC_IN 的输入电压不能超过 1.2V 的峰峰值(VDDA_OSC)。如果使用超过 1.2V 峰峰值的数字时钟源,建议使用电阻进行分压后再输入,如图所示:

2.4 典型参考设计

如下图所示为两颗 TJA1102 与一颗 SJA1105P/Q 通过 MII/RMII 连接的系统示意图,其中主控与 SJA1105P/Q 通过 RGMII 接口连接。

为了与 TJA1102 兼容,必须选择 3.3 V 的 VDDIO_MIIx 电源。其他接口的电源则根据主控系统电平决定对应的电压大小。

2.5 PCB Layout 指导

在去耦电容的布置设计中,应注意寄生电感和寄生电阻对去耦电容谐振频率的影响,从而影响去耦性能。

尽量减小寄生电感和电阻:

a. 减少去耦电容至电源和地引脚之间的走线长度。

b. 增加走线宽度。

c. 小电容尽量靠近芯片引脚,因为谐振频率高的小电容更容易受到寄生电感和电阻的影响。

以上就是关于 SJA1005x 的硬件设计的全部内容,接下来我们也会不断推出关于ADAS 域控制器硬件设计的开发博文。

-

以太网交换机的测试2014-03-03 0

-

如何配置以太网交换机2008-12-07 17985

-

什么是以太网交换机/ATM交换机2010-04-07 2474

-

GOE300车载三层工业以太网交换机2016-12-27 1172

-

GOE200车载千兆工业以太网交换机2016-12-27 1218

-

MMoIP以太网交换机硬件安装手册2017-01-01 969

-

工业以太网交换机简介及其与普通交换机的区别介绍2017-10-17 2705

-

工业以太网交换机和普通交换机的区别2017-10-25 11711

-

以太网交换机的基本概念,具有什么特点2020-12-19 8964

-

工业以太网交换机怎么使用2021-08-13 11197

-

以太网交换机是什么 以太网交换机的使用方法2022-10-09 1030

-

以太网交换机是什么?2023-05-05 3262

-

以太网交换机怎么用2023-05-05 7033

-

详解工业以太网交换机的原理、特点、优势、应用2023-04-25 4712

-

以太网交换机怎么用 以太网交换机有什么用2024-02-02 3144

全部0条评论

快来发表一下你的评论吧 !