如何在SaberRD中使用IBIS工具转换3-state_ECL模型呢?

电子说

描述

名词解释

IBIS(Input/Output Buffer Information Specification)输入/输出缓冲器信息规范

3-state(三态):通常作为驱动器,也可通过使能端关闭

ECL:(Emitter Coupled Logic,发射极耦合逻辑威廉希尔官方网站 ),包括input_ECL、output_ECL、I/O_ECL、3-state_ECL

说明

IBIS是一种基于V/I曲线的,对I/O缓冲器快速准确建模的方法,其目的是提供一种集成威廉希尔官方网站 制造商与仿真软件供应商以及设计工程师之间相互交换电子元件仿真数据的标准方法。

IBIS模型是一种行为模型,它不是从需要仿真的元件的结构出发定义,而是从元件的行为出发定义的。

IBIS本身是一种标准的文本格式,它记录驱动器和接收器的不同参数,如驱动源输出阻抗、上升/下降时间以及输入负载等参数,但它不说明这些记录参数是如何使用的。

SaberRD的IBIS模型工具可以帮助工程师更容易地将IBIS数据文件中的模型信息导入到SaberRD IBIS缓冲区模型中,进行引脚选择,并使用已保存的组件原理图生成层次符号,进而生成相应的SaberRD模型,以便在SaberRD仿真环境中使用。

IBIS模型文件通常由IC供应商提供,供Saber使用的IBIS模型很多。

目前的SaberRD支持IBIS 4.2版本,向下兼容所有以前的版本。

用IBIS转换工具可以将3-state模型转换,但使用IBIS转换工具并不能直接将3-state_ECl模型转换为Saber模型。

解决方案

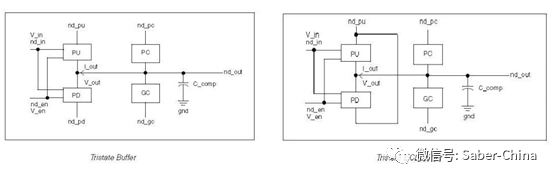

根据HSPICE用户指南,3-state_ECL缓冲区几乎类似于3-state缓冲区。最主要的区别是3-state_ECL缓冲区没有下拉节点。下面给出了两个缓冲区的框图。

解决方案包括两个步骤。

步骤1:更改模型类型并转换

a. 用记事本应用程序打开要转换的*.ibs文件;

b. 搜索Model_type。

c. 将模型类型值从“3-sate_ECL”更改为“3-state”。

d. 保存文件。

e. 现在使用IBIS工具将ibs模型转换为Saber模型。

步骤2:移除下拉节点。

a. 转换完成后,对应的*.ai_sch和*.ai_sym文件被创建。

(1)在工作目录中创建一个新的设计文件(例如:test_design.ai_dsn)

(2)放置*.ai_sym在原理图上。

(3)右键单击符号并选择“Open hierarchy”。

b. 删除名称为“pd”的同页连接器和节点

c. 连接npu和npd,如下图所示。

d. 对其它(ib_*)有pu和pd节点的块重复上述步骤。

e. 保存设计。

练习实例

文后给出了一个小例子,你可以检查样例ps020h33_mod。并检查ps020h33.ibs文件。zip文件中的.ai_dsn文件,用于指定pu和pd之间的连接。

-

IBIS 模型2008-07-30 0

-

IBIS模型2013-11-06 0

-

请问如何将HSPICE和 IBIS两种模型怎么转换成TINA软件中用?2024-09-02 0

-

请问有人知道IBIS模型怎么使用吗?2017-02-13 0

-

高速互连IBIS仿真模型概述2018-09-03 0

-

怎么使用IBIS模型用于Spartan-3A2019-05-15 0

-

生成IBIS模型错误2019-05-27 0

-

如何在最新版本的Genesys中使用ADS模型?2019-10-17 0

-

在Hyperlynx中使用Xilinx Artix IBIS模型时,IO模型不可选是怎么回事2020-05-26 0

-

工程师们为什么会使用 IBIS 模型呢?2021-04-12 0

-

请问哪里可以找到ADA4817的IBIS模型呢?2023-11-17 0

-

如何使用Model Integrity转换IBIS模型2021-03-04 4545

-

LTC4313-3 IBIS模型2021-06-10 430

-

如何在SaberRD中评估闭环DC-DC升压变换器的环路稳定性?2023-12-05 958

-

SaberRD外部模型导入功能—IBIS TOOL2023-12-06 1371

全部0条评论

快来发表一下你的评论吧 !