解读AXI总线系统中的多交易操作应用

接口/总线/驱动

描述

本文以解读AXI协议中的多交易操作部分为目的而展开介绍,首先介绍了AXI协议基本概念中与多交易操作相关的概念,之后对多交易操作所涉及的“outstanding”、“out of order”和“interleaving”等重要概念做了基本解读。

1、AXI基本概念

基本互联结构

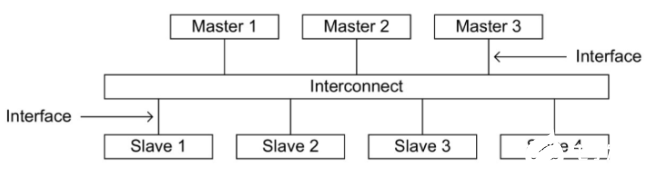

AXI总线系统由Master、Slave和Interconnect等基本器件搭建而成,器件间的互联方式如下图所示:

通道分离

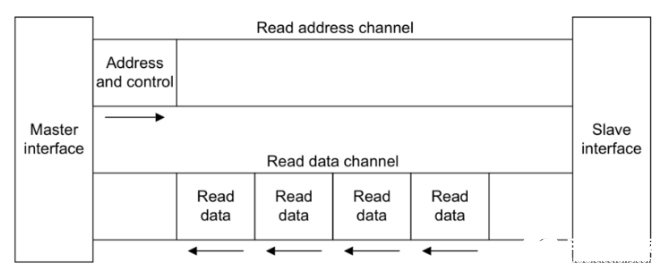

AXI协议定义了5个独立的通道,每个通道通过VALID和READY信号完成握手机制。 五个通道分别为:读地址通道、读数据通道、写地址通道、写数据通道和写响应通道。 读交易通道结构如下图所示:

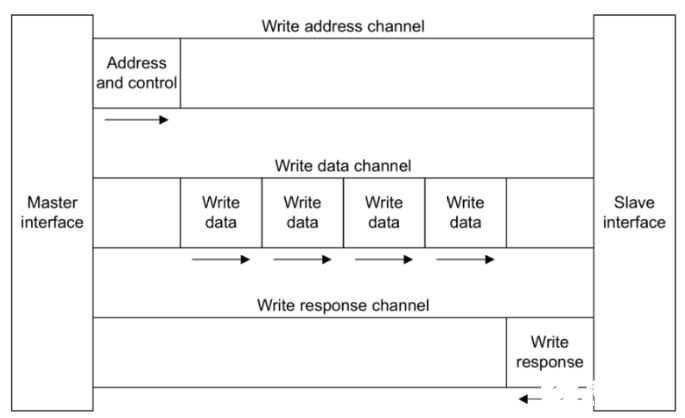

写交易通道结构如下图所示:

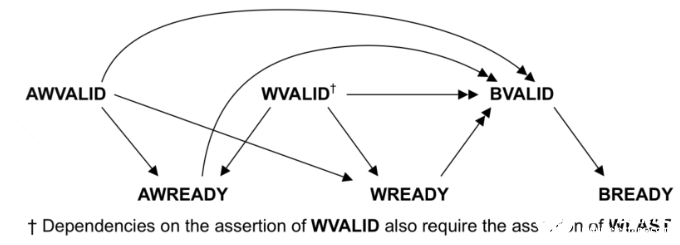

读写交易中握手信号的依赖关系

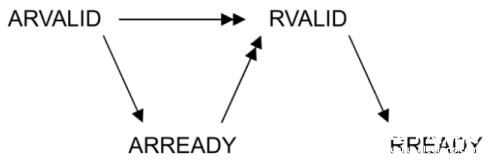

读交易中握手信号的依赖关系如下图所示:

写交易中握手信号的依赖关系如下图所示:

注:单箭头指向的信号可以在指向它的信号未使能或使能后,它再使能;双箭头指向的信号必须在指向它的信号全都使能后,它再使能。

独立的交易ID

通过接口的每次交易都有一个ID标签且五个通道均具备传递ID标签的能力。

2、多交易中的“out of order”概念

“out of order”即乱序传输。

协议基本规定

在猝发读模式中,相同交易ID的Slave应依据地址发送顺序返回对应读数据; 在猝发写模式中,相同交易ID的Master应依据地址发送顺序发送对应写数据; 不同ID的交易间,不同交易的读写命令与命令对应的读写数据间无顺序限制。

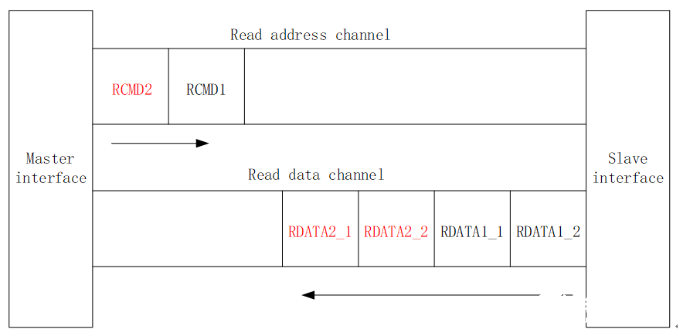

乱序传输的示意案例

二猝发的读交易乱序传输示意图如下图所示: (其中Master先发出读命令RCMD1,后发出读命令RCMD2,但Slave先返回了RCMD2对应的读数据RDATA2_1和RDATA2_2)

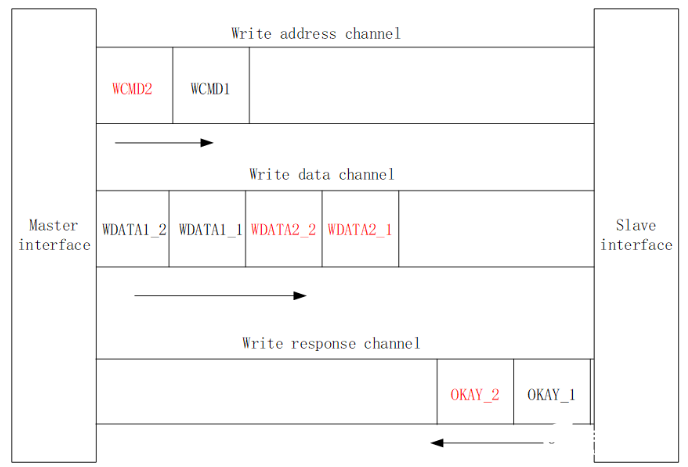

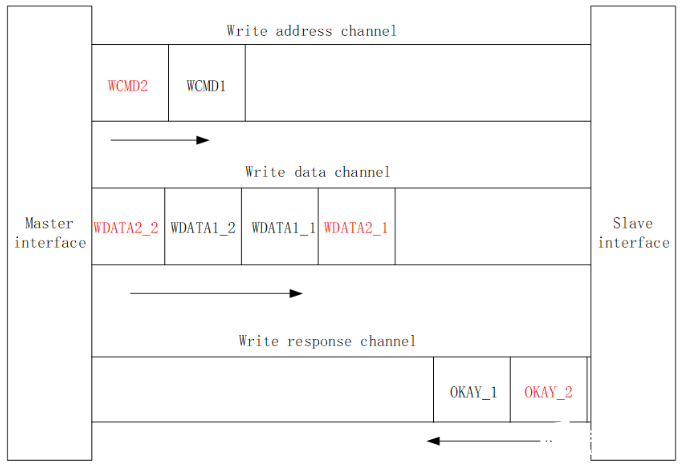

二猝发的写交易乱序传输示意图如下图所示: (其中Master先发出写命令WCMD1,后发出写命令WCMD2,但Master先发出了写命令WCMD2对应的写数据WDATA2_1和WDATA2_2)

乱序传输的优势

“out of order”技术保证响应较快的存储区域不必等待响应较慢的存储区域,降低了交易延时,从而提高了系统性能表现。

3、多交易中的“interleaving”概念

“interleaving”即交错传输。

协议基本规定

在猝发读模式中,不同交易ID的Slave返回数据间允许交错传递; 在猝发写模式中,不同交易ID的Master写入数据间允许交错传递。(此项只在AXI3协议中生效)

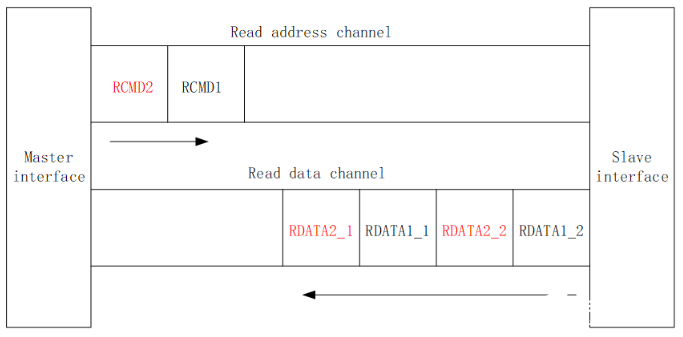

交错传输的示意案例

二猝发的读交易交错传输示意图如下图所示: (其中Master先后发出读命令RCMD1和RCMD2,Slave依据时间先后,交错返回了RDATA2_1、RDATA1_1、RDATA2_2、RDATA1_2等读数据)

二猝发的写交易交错传输示意图如下图所示: (其中Master先后发出写命令WCMD1和WCMD2,Master依据时间先后,交错写入了WDATA2_1、WDATA1_1、WDATA1_2、WDATA2_2等写数据)

交错传输的优势

在读交易下,“interleaving”技术保证了不同响应状况的Slave在传递读数据时能最大化利用互联带宽; 在写交易下,当Master单此猝发传输的写数据来自速度不同的存储单元时,“interleaving”技术能够提升互联带宽的利用率。

4、多交易中的“outstanding”概念

“outstanding”即待处理的传输。

协议基本规定

AIX总线系统支持同时发布多个未完成的交易地址。

待处理传输的优势

“outstanding”技术意味着Masters可以不需等待上一交易完成便可发布交易地址,因而使能了总线系统平行处理多个交易的能力,进而提高了系统性能。

=============================================================================

AXI事务ID与outstanding/out of oreder/interleaving实现关系

前言

众所周知,AXI3/AXI4支持outstanding/out of order/ interleaving的特性,但是这一特性是根据AXI哪一路实现的,以及需要注意和说明的地方是什么。

here is the analysis.

超前传输 outstanding的实现

outstanding是什么

outstanding表示AXI超前传输的特性,表示这笔transaction还没完成,可以先提起别的事务,这么说如果抽象的话,那么就是AR/AWchannel可以提起多个事物,即便在W/R channel数据还没发完或者还没发的情况下。

超前传输是如何实现的?

在不考虑其他两个特性(乱序和交织)的情况下,AXI事务都是顺序完成的,这时多事务在途不需要其他信号来实现,直接根据write channel或者read channel的LAST信号或者response channel的信号来判断分割事务就可以了。可以认为是一种队列或FIFO结构,AR/AWchannel发起事务就是顺序压入队列,当这些事务对应完成的时候,就最提起事务先弹出队列,表示结束,然后接收完成后面的事务。

超前传输的可支持性

超前传输需要master和slave都支持超前传输,其中outstanding depth表示了主机超前传输的性能,表示同一时刻最多支持多少个AXI 事务在途。

如果slave不支持outstanding如何响应?

AXI 从机可选地支持超前传输,假设从机不支持超前传输,只需要在接收到 Trans0 后,置低 AxREADY 信号,阻止主机超前传输。在返回读数据后,再置高 AxREADY 信号,接收下一事务。如下图所示,主机将 Trans1 保持在总线上直至从机接收。

乱序 out of order的实现

out of order乱序是什么?

当有多个事务在途的时候,有的事务可能先准备好,因此可以先发送在总线上。那就需要面对一个问题,如何判断返回的是哪个事务的数据?这就与AXI的事务ID有关

AXI的事务ID

AXI的事务ID包含了:

AWID

WID (只有AXI3有,AXI4没有,因此不支持写交织)

BID

ARID

RID

AXI out of order乱序的实现模型与思路

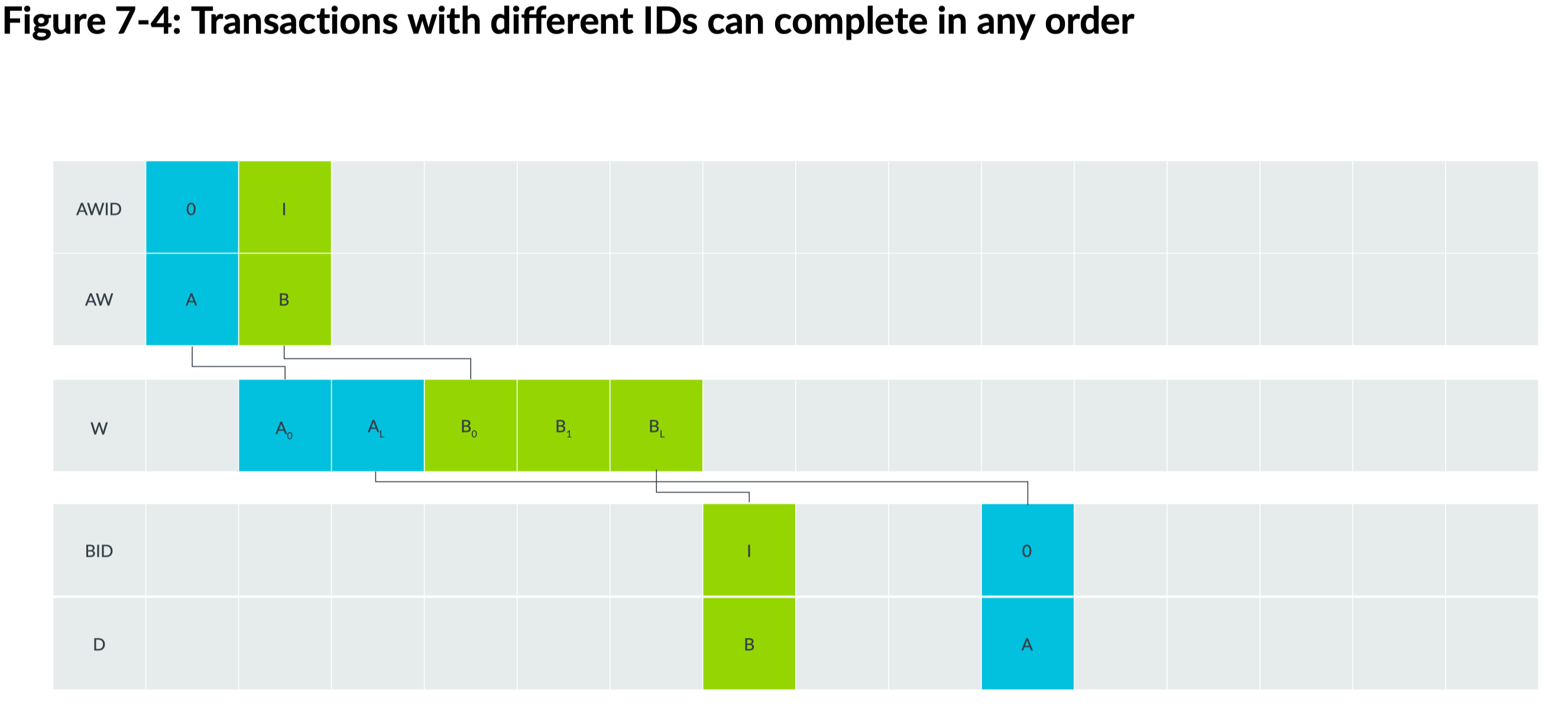

AXI乱序的特性是由地址channel和响应channel上的ID信号AWID/ARID和WID/RID来实现的,根据ID不同来标识事务不同,但是并不代表不同事务传输AWID/ARID就已经要不同

不同事务的AxID如果一致,那么这些事务就不能实现out of order,只能进行顺序完成。(因此需要重排序模型,重排序模型包括了事务缓冲区和数据缓冲区,事务缓冲区存放在途需要完成的事务,对于slave来说,其可能对于不同事务完成的时间不同,因此事务准备好了与事务缓冲区的首个事务比较,如果匹配就输出,如果不匹配就进入数据缓冲区)

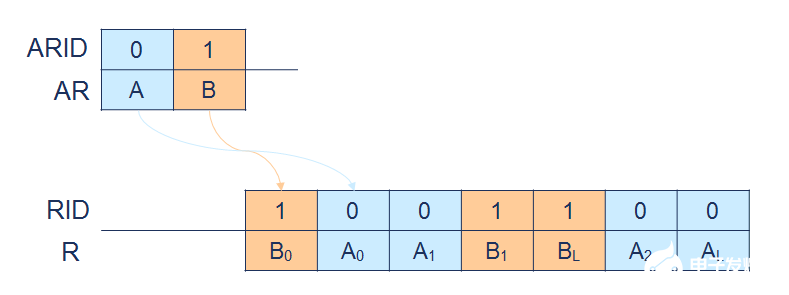

如果不同事务AxID不同,那么这些事务之间可以乱序。那么不同AxID事务的数据,对于AXI读来说,如何判断返回的数据属于哪个事务呢,是通过RID来进行匹配的,也就是说,在完成乱序传输的时候,需要RID和ARID保持一致,以标识不同事务的数据

那么对于实际情况来说,在实际传输中,可能有的事务AxID是不同的,有的是相同的,这是如何解决的?答:对于ID相同的就顺序完成,对于ID不同的可以乱序。

在实际应用中,在slave的实现中,为每个ARID准备了一个事务缓冲区和数据缓冲区,以支持相同ID和不同ID的数据顺序传输和乱序传输。

有关于写乱序

有一个重要的观点,写乱序不是针对于master来说的,说的不是不同事务发送的顺序可以不一样(即事务A先发起,事务B后发起,先发B事务的数据然后再发A事务的数据,如此叫做乱序,这种观点是错误的!)

写乱序指的是:乱序是针对slave来说的,slave接收到了多个事务(可能是多个master传输来的事务)那么slave返回BID的顺序与发送过来的AWID顺序是不同的,这叫做写乱序,如图所示,slave对于写事务的完成(响应)可以是乱序的,称之为写乱序,写乱序实际上指的是写响应乱序。

对应写事务乱序跟读事务也是相同的

通过BID和AWID来表示数据所属事务

AXI interleaving 交织的实现

什么是交织?

interleaving表示不同事务的数据可以被打散混合排列(但是注意,这里说的混合排列是不同事务间的,同一个是数据是不循序被打乱的)。例如事务1数据是0a 0b,事务2数据是1a 1b,如果不支持交织,那么总线上数据的传输需要是0a0b1a1b或者1a1b0a0b,如果支持交织的话那么就可以是0a1a0b1b(或者别的插入顺序)

交织的实现

对于读交织来说,读事务的response方向和读方向的相同的,不同事务交织是通过RID来进行识别的,也就是说RID在AXI传输中即起到了out of order乱序的不同事务识别也起到了interleaving交织中不同事务数据的识别

对于写交织来说,由于写方向和response方向不一样,那么WID就是提供了写交织的不同事务的识别,BID提供了乱序不同事务的识别。使用与 AWID 匹配的 BID 标识写回复所属的事务 ID。实际上从机给出写回复可以类比读事务中给出读数据的过程。

总结

到此为止,介绍了AxID和RID/BID在AXI乱序交织中的作用。

审核编辑:黄飞

-

一文详解ZYNQ中的DMA与AXI4总线2020-09-24 5297

-

Xilinx zynq AXI总线全面解读2020-12-04 7133

-

FPGA中的除法运算及初识AXI总线2018-08-13 0

-

如何手动设置读/写使用AXI总线注册测试接口代码?2019-09-09 0

-

看看在SpinalHDL中AXI4总线互联IP的设计2022-08-02 0

-

基于AXI总线的MicroBlaze双核SoPC系统设计2012-03-09 1566

-

AMBA AXI总线学习笔记2015-11-11 1098

-

AXI总线的MicroBlaze双核SoPC系统设计2017-10-31 1113

-

ARM+FPGA开发:基于AXI总线的GPIO IP创建2020-12-25 5678

-

ZYNQ中DMA与AXI4总线2020-11-02 4334

-

AXI总线协议简介2022-10-10 10090

-

SOC中AXI总线怎么连接2022-11-30 1684

-

AXI总线工作流程2023-05-25 1001

-

Xilinx FPGA AXI4总线(一)介绍【AXI4】【AXI4-Lite】【AXI-Stream】2023-06-21 2279

-

SoC设计中总线协议AXI4与AXI3的主要区别详解2024-05-10 6682

全部0条评论

快来发表一下你的评论吧 !