LDMOS在ESD设计中的应用设计思路

EMC/EMI设计

描述

LDMOS在ESD设计中的应用。LDMOS属于功率半导体器件,主要应用于高压场合。而针对高压芯片的ESD防护领域,可采取GGNLDMOS的设计思路。

在讲解LDMOS的ESD防护机理之前,先要简单解释下LDMOS的工作原理。

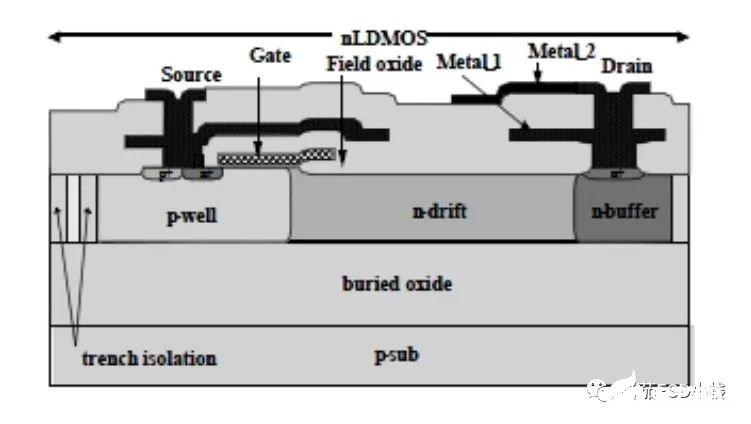

图一.nLDMOS结构示意图。

N-LDMOS为了提高器件的耐压性能,在器件内部制作了n-drift区,同时为了提高器件栅极的耐压能力,N-drift上方的栅极是需要盖在场氧之上,将场氧作为氧化层。也是因为这样的设计,整个NLDMOS器件的VGD和VSD的负向耐压很高。(V:D→G,D→S)

而嵌入器件中的N-drif阱的掺杂浓度会低于p-well和n-buffer,其与p-well接触区会形成空间电荷区,根据之前文章的讲解,存在浓度差的线性缓变结其接触面的空间电荷区会主要分布在N-dfift内,如图。

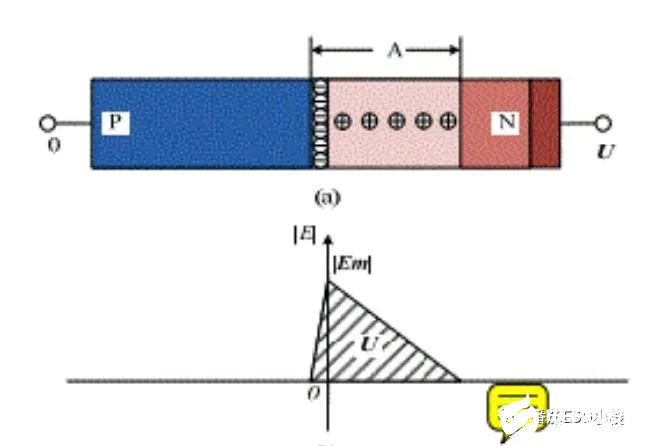

图二. N-drift空间电荷区分布示意图。

当整个器件关断时,这部分空间电荷区等效于在NLDMOS中嵌入一个高耐压“电阻”,也正是因为这个“电阻”的存在,使得器件的Drain端能承受高电压。当栅压开启整个MOS管后,P-well上方的栅还和正常MOS一样在P-well内形成沟道,而N-drift上方的栅会在靠近场氧的区域内形成积累层,从而形成沟道,就如同栅压将空间电荷区往器件内部推进,在场氧下方推出一条“沟道”。

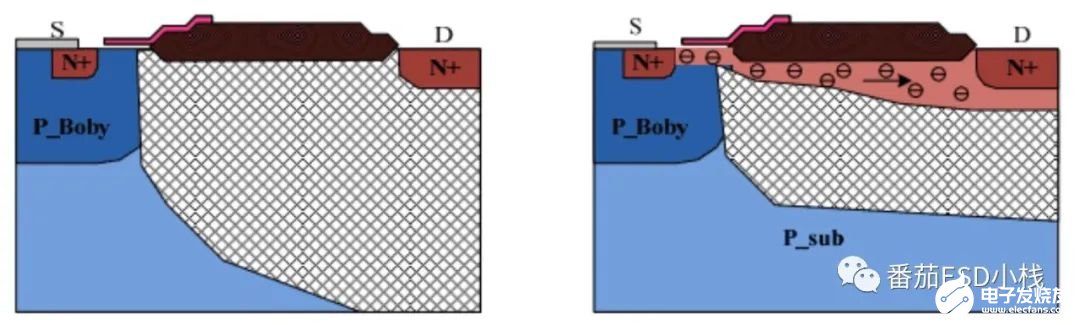

图三. LDMOS的工作原理示意图。

而随着对高耐压性能的追求,越来越多的tips也开始应用到LDMOS的设计中。目前常见的有RESURF、场板、super junction等。

因为NLDMOS的耐压性能也决定了其作为ESD器件的耐压上限,所以这里大概介绍下这三种设计。

RESURF:

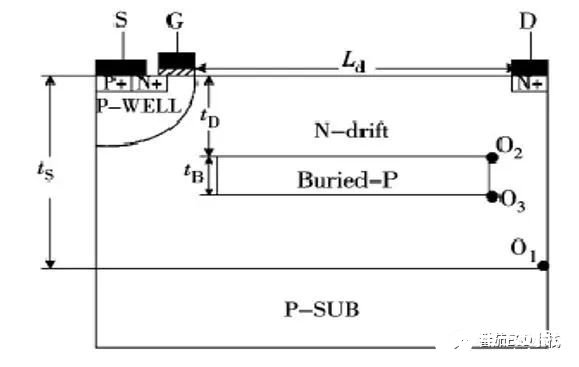

图四.体硅RESUFR结构示意图。

RESURF就是在N-drift中继续埋入一层P-Buried,使得N-drift中的空间电荷区分布更大,同时调制电场分布,改变反向击穿的节点。

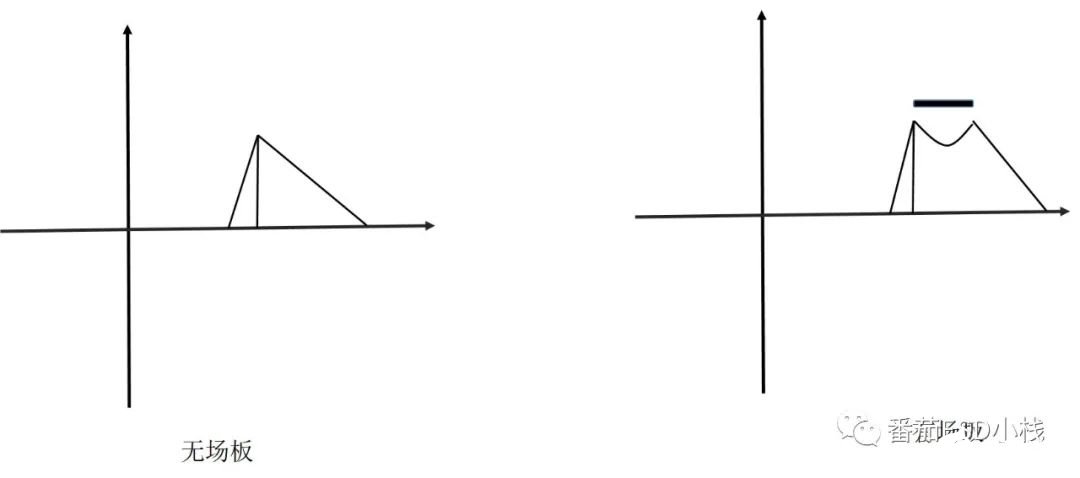

2.场板:

场板就是图一中Drain上方的M1,M2金属层,金属延伸在Gate上方形成场板。场板通过改变表面电势分布来抑制表面电场的集中,获得更均匀的表面电场分布,从而提高器件的整体耐压性能。

图五.场板电场分布。

场板能一定程度缓解了电力线在冶金结处的集中,降低了冶金结的峰值电场,同时在场板末端引入新的电场峰值,提高耐压能力。

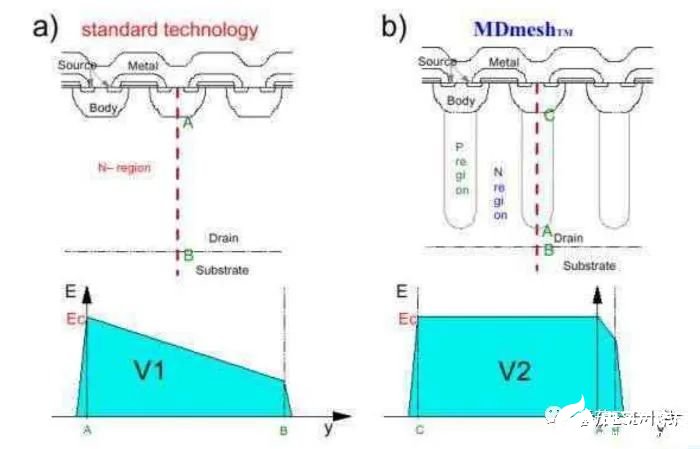

3.Super Junction

超结工艺广泛应用于超高耐压器件,超结是RESURF技术的延伸,通过制造出很深的阱来提高器件耐压能力。

图六.超结示意图。

目前超结工艺能提供600V到1000V的超高压耐压能力,但是超结自身也存在着诸多问题。

因为LDMOS主要应用于工业级,工作环境更加复杂多变,其对ESD、浪涌的需求也相对较高。所以针对高压ESD设计难度也较大。

上期讲解了LDMOS的工作原理,在高压BI-CMOS工艺中ESD防护目前有两种设计思路:一种是将低压器件进行stack,另一种是直接使用高压ESD防护器件。第一种思路的劣势是对面积需求过大,优点是工艺偏差小。而高压防护器件对面积的需求小,但是工艺偏差大,同时具有latch-up风险。

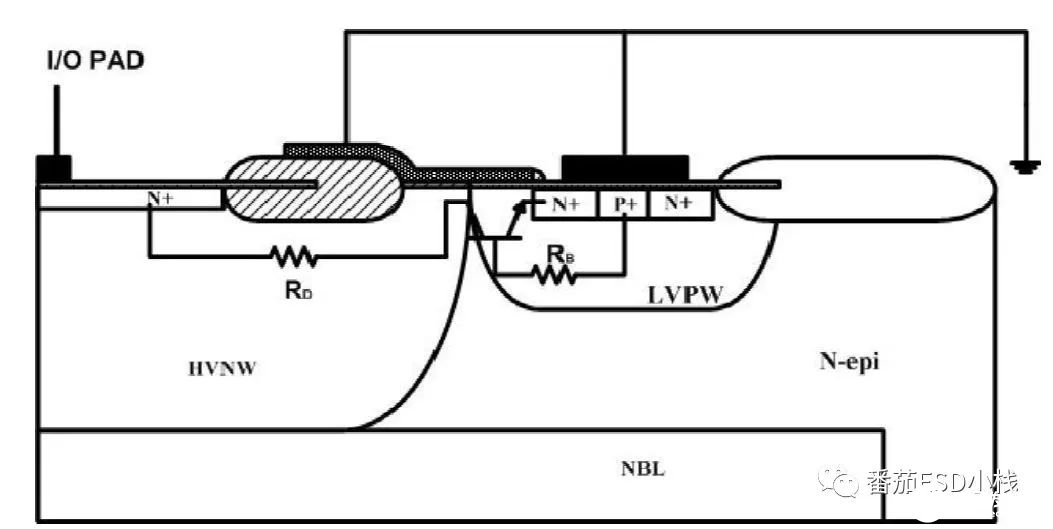

无论哪种设计思路都需要定制ESD器件,fab厂也会给出相应的ESD design rule。LDMOS在ESD防护中的连接方式如图所示:

图一.GGLDMOS结构示意图。

与GGNMOS类似,GGNLDMOS也同样源,栅,体三端接地,漏端接IO PAD。而因为LDMOS本身具有漂移区,漏端空间较大,所以其漏端的耐压能力较高,内部击穿电压较高,Trigger voltage和Holding Voltage也相对较高。因其本身所具有的优异耐压性能,并不需要针对器件版图进行大改,只需要关注器件隔离就行。

但是部分fab厂并不建议GGNLDMOS的原因主要出于热电效能的考虑。LDMOS的热失效风险较高。具体表现为冶金结处电场强度过大,会造成热量过于集中,容易造成软失效。所以GGNLDMOS的设计难点在于预防电场过于集中,需要对电场进行再分布处理。

改善电场分布的手段主要有两种:一种是改变版图尺寸,一种是改变器件结构。

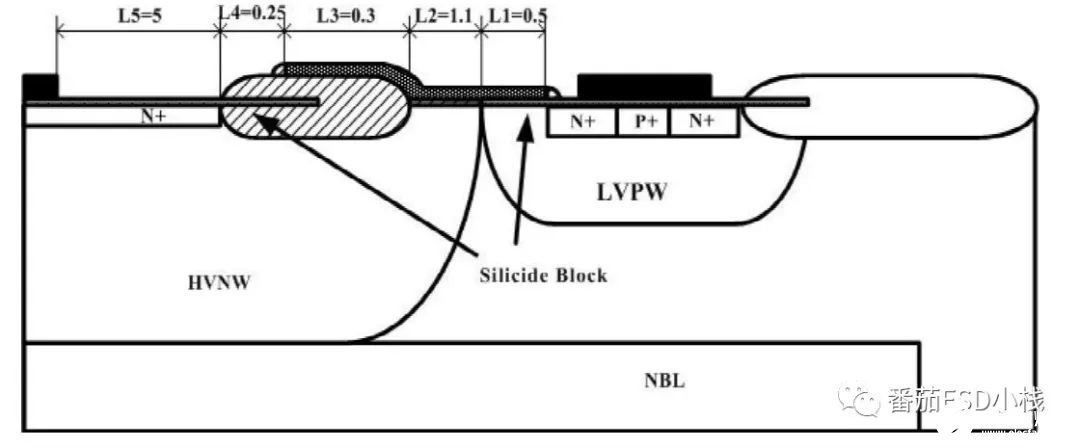

版图尺寸:

图二.LDMOS版图示意图。

L1是 Gate在P-weLL上方的距离;L2是厚栅氧层跨在N-well上方的距离;L3是栅极长度;L4是无栅级的漂移区距离;L5是N—implant与contact的距离。调整L4与L3的距离能改变器件耐压能力,同时要缩短L5和L1的的距离,在提高耐压能力的同时,提高器件的电流导通能力,防止冶金结过热,造成的器件损坏。

器件结构:

为了提高GGNLDMOS的抗静电性能需要在阱与阱之间添加缓变结,就是改变阱结构,在DRC允许的情况下在HNWELL中嵌套NWELL以实现浓度梯度,改变单一结载流子过于集中的现象,用以缓解热电效应。

审核编辑:黄飞

-

ESD静电整改有什么基本思路?2023-11-02 783

-

电容在ESD中的应用—耦合效应2014-02-20 0

-

压敏电阻在ESD中的作用?2015-12-28 0

-

LDMOS结构及优点的全面概述2019-06-26 0

-

高压LDMOS在军事和航空航天领域的应用2019-07-05 0

-

如何利用RFIC设计抗击穿LDMOS?2019-07-31 0

-

硅基氮化镓与LDMOS相比有什么优势?2019-09-02 0

-

LDMOS的优势是什么?2020-04-07 0

-

LDMOS介绍2020-05-24 0

-

什么是LDMOS?LDMOS有哪些有优良性能?2021-06-18 0

-

在AWR中模拟LDMOS MRFE6VS25N时模型只有32位是怎么回事?2023-04-23 0

-

LDMOS器件在ESD保护中的应用2009-12-14 716

-

LDMOS器件静电放电失效原理2011-12-01 10627

-

浅谈ESD整改的基本思路2019-01-26 1103

-

电容在ESD测试整改中的妙用2023-12-07 652

全部0条评论

快来发表一下你的评论吧 !