FPGA产业发展现状分析

描述

现场可编程门阵列 (FPGA) 是提供适应性强且可更改的硬件功能的半导体。它们包含各种可变逻辑单元和可编程连接,允许个人制作和执行个性化数字威廉希尔官方网站 ,而无需创建自己独特的芯片。

FPGA 广泛应用于电信、航空航天和工业自动化等多个领域,这些领域需要快速创建、最小延迟和强大的计算能力。它们的适应性使它们成为硬件开发、研究和独特计算职责的宝贵资产。

全球现场可编程门阵列 (FPGA) 市场预计未来几年将以7.8% 的复合年增长率稳定增长。

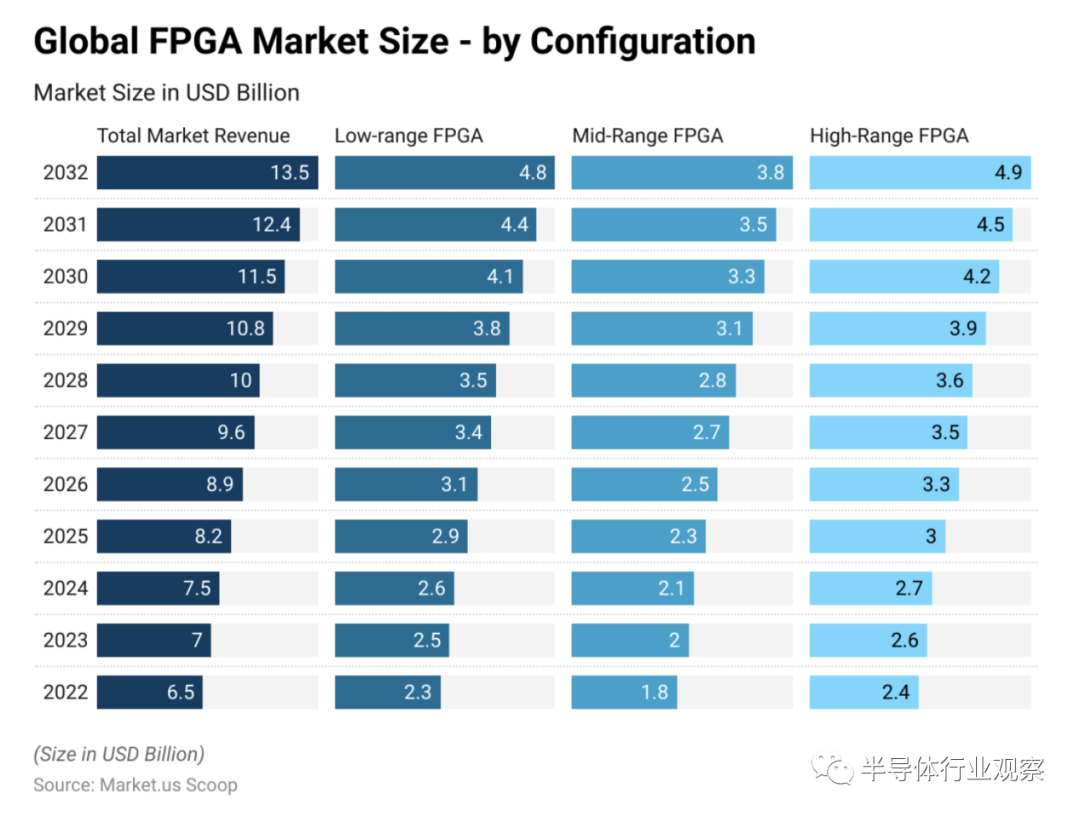

2022年,FPGA市场收入为65亿美元,预计2023年将增至70亿美元。收入将持续增长,到2024 年将达到75亿美元,2025 年将达到82亿美元,2026年将达到89亿美元。随着我们的进一步推进,预计该市场将在2027 年达到96亿美元,2028 年达到100亿美元,2029 年达到108亿美元。这一增长趋势将持续下去,预计2030年收入将达到115亿美元,2031年将达到124亿美元,2032年将达到135亿美元。

展望2032年,低端 FPGA 预计将达到48亿美元,中端 FPGA 为38亿美元,高端 FPGA 占市场总收入的49亿美元。这种上升轨迹反映了 FPGA 在为从电信到汽车等广泛应用提供可定制和适应性强的硬件解决方案方面发挥着至关重要的作用。

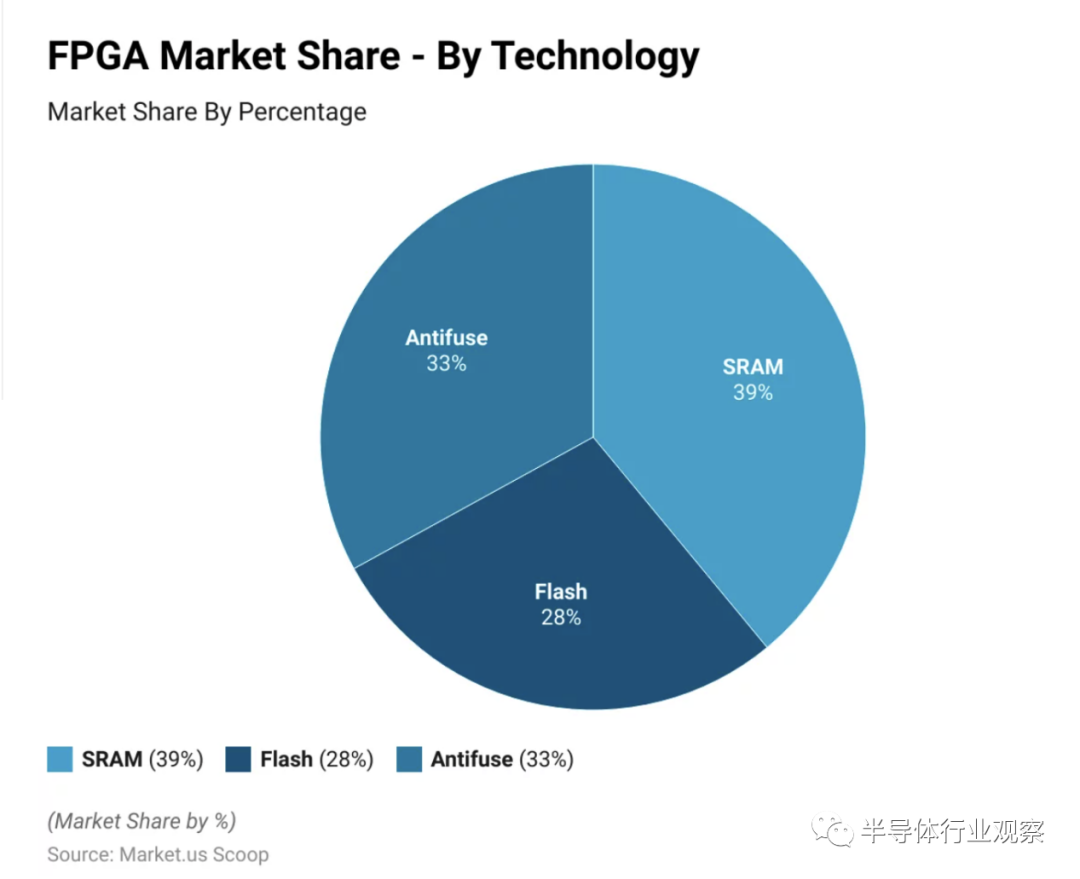

技术的市场份额分布揭示了全球现场编程门阵列 (FPGA) 市场的有趣格局。

截至最新数据,基于SRAM的FPGA以39%的份额占据市场主导地位。这些 FPGA 以其可重新配置性和速度而闻名,在灵活性和快速周转时间至关重要的应用中受到青睐;紧随其后的是基于闪存的 FPGA,占据了28% 的市场份额。闪存 FPGA 因其非易失性配置存储而受到重视,使其成为需要数据持久性和安全性的应用的理想选择;最后,基于反熔丝的 FPGA占据了33% 的市场份额。当可靠性和安全性至关重要时,首选反熔丝技术,因为它提供一次性可编程配置,一旦设置就无法更改。

FPGA 市场的技术多样性凸显了根据特定应用需求定制硬件解决方案的重要性,以确保许多行业从这些多功能设备中受益。

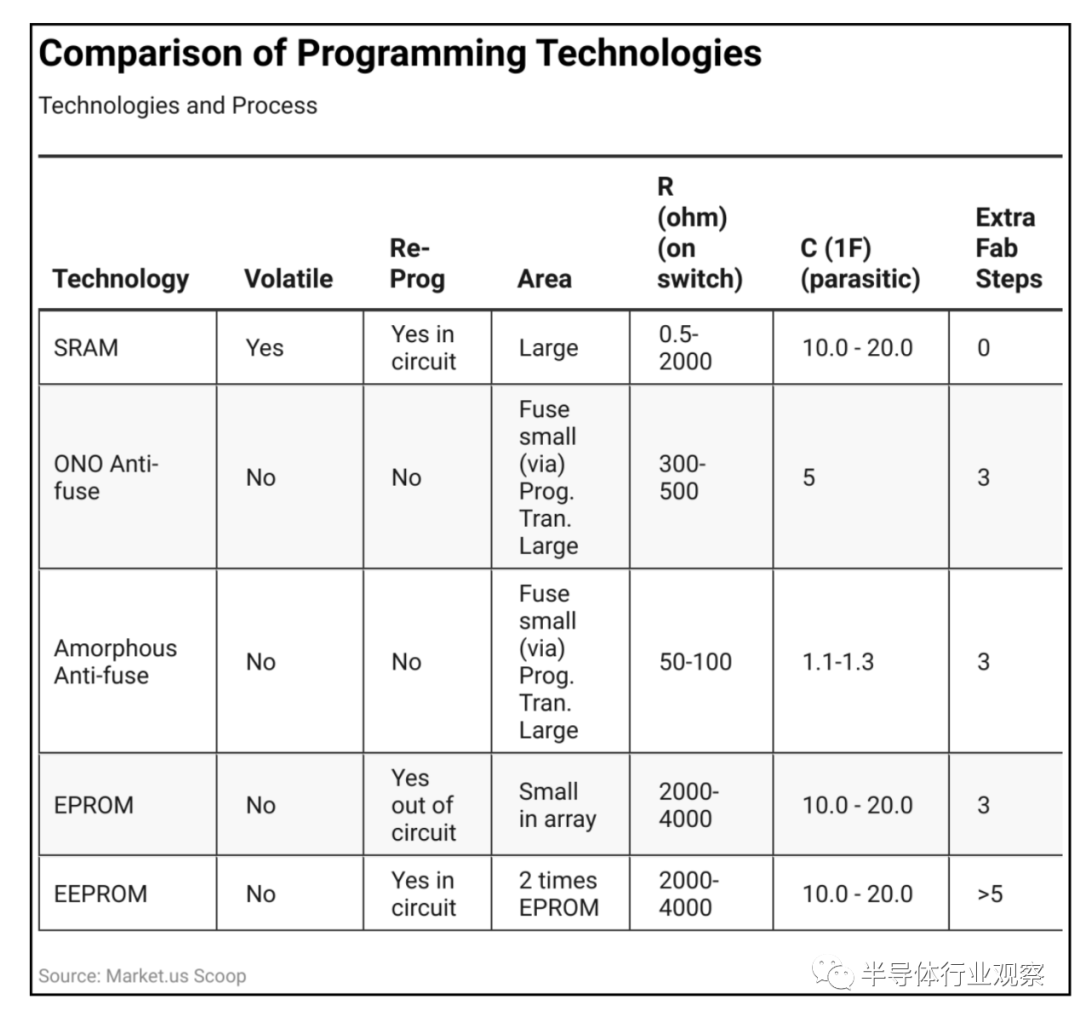

我们来看一下不同技术的FPGA的对比,在比较不同的 FPGA 编程技术时,有几个关键因素会发挥作用。

首先,我们考虑易失性,基于 SRAM 的 FPGA允许在威廉希尔官方网站 中进行易失性重新编程。相比之下,基于反熔丝的 FPGA(无论是ONO 类型还是非晶类型)都提供非易失性编程,使其适合数据持久性至关重要的应用。

其次,就面积和电气特性而言,基于 SRAM 的 FPGA 往往比反熔丝变体具有更大的面积,反熔丝变体具有小型熔丝元件和编程晶体管。

开关上的电阻 (R) 和寄生电容 (C) 在信号传播中起着至关重要的作用,ONO 反熔丝 FPGA 具有适中的电阻(300-500 欧姆)和低电容(5F),而非晶反熔丝 FPGA 的表现较低电阻(50-100 欧姆)和稍高的电容(1.1-1.3F)。

此外,每种技术所需的额外制造步骤各不相同。SRAM FPGA 通常不涉及额外的制造步骤,因此相对简单。

相比之下,ONO 和非晶反熔丝 FPGA 都需要额外的步骤来创建熔丝和对晶体管进行编程。

此外,在提供非易失性重新编程的同时,基于 EPROM 和 EEPROM 的 FPGA涉及额外的制造步骤,并且比反熔丝选项稍大的占地面积。

在为特定应用选择最合适的 FPGA 编程技术时,这些考虑因素强调了波动性、可编程性、面积和电气特性之间的权衡。

来到架构方面,从根本上来说,FPGA 的架构由许多称为可配置逻辑块 (CLB) 的重要元素组成。这些 CLB 被适应性连接系统(通常称为结构)包围,该系统有助于在这些 CLB 之间路由信号。

此外,输入/输出 (I/O)模块将 FPGA 连接到外部设备。根据特定制造商的不同,这些 CLB 可能由逻辑块 (LB)、逻辑元件 (LE) 或逻辑单元 (LC) 等替代术语表示。

在单个 CLB 中,您会发现多个逻辑块。FPGA 的一个重要组件是查找表 (LUT),它是一个定义性功能。LUT 为每个可能的输入组合存储一组预定的逻辑结果。

通常,广泛采用具有四到六个输入位的 LUT 。在这种情况下,经常会遇到多路复用器 (mux)、全加器 (FA) 和触发器等标准逻辑功能。

CLB 内组件的配置和布局可能因设备而异。通常,它包括两个三输入 LUT、一个全加器、一个 D 型触发器和一个标准多路复用器。此外,还有两个额外的多路复用器,它们是在 FPGA 编程期间设置的。

这种简化的 CLB 有双重目的。在标准模式下,LUT 与 Mux 2 结合创建一个四输入 LUT。相反,在算术模式下,LUT 输出以及来自另一个 CLB 的进位输入成为全加器的输入。

Mux 4选择全加器的输出或 LUT 输出。Mux 6通过 D 触发器确定操作是异步还是与 FPGA 时钟同步。

在最新一代 FPGA 中,CLB 变得更加复杂,能够在单个块中处理多个任务。它们可以组合起来执行乘法、数据存储、计数甚至数字信号处理 (DSP) 任务等高级功能。

再看SoC FPGA,SoC FPGA 是片上系统现场可编程门阵列的缩写,提供针对不同应用定制的各种处理功能。以英特尔的 Cyclone V为例,它是一款经济高效且节能的 SoC FPGA。

它专为在大容量场景中表现出色而设计,例如控制工业电机、桥接协议、处理视频处理任务以及为便携式设备供电。

Cyclone V 由两个主要元素组成:FPGA部分和以单核或双核32 位 Arm Cortex-A9 MPCORE为中心、主频为 925 MHz 的硬处理器系统(HPS)。这两个部分都配备了一系列外围组件,其中可能包括来自第三方供应商的专用硬件。与此形成鲜明对比的是,Stratix 10 SX面向高性能应用,例如通信系统、加速数据中心、为高性能计算 (HPC) 设置提供动力、处理雷达数据以及充当 ASIC 原型设计平台。该 FPGA 凭借其四核64 位 Arm Cortex-A53处理器而大放异彩,运行速度高达1.5 GHz。

统计可见,现场可编程门阵列 (FPGA) 是一种多功能半导体器件,因其灵活性和可重新配置性而应用于电信、航空航天和工业自动化等行业。它们由可配置逻辑块 (CLB) 和可编程互连组成,无需定制芯片即可实现定制数字威廉希尔官方网站 设计。

SoC FPGA 将 FPGA 结构与嵌入式处理器相结合,适用于各种应用。虽然 FPGA 具有低延迟、快速处理和成本优势,但它们比 GPU 更昂贵,尤其是对于较大的模型。来自威廉希尔官方网站 板供应商、IP 供应商和工具的额外费用可能会极大地增加总体成本。

文章来源:半导体行业观察

审核编辑:汤梓红

-

我国分布式光伏发电发展现状2014-04-22 0

-

通信电源产业链发展现状与趋势分析(一)2018-09-26 0

-

物联网发展现状分析2021-01-12 0

-

FPGA的发展现状如何?2021-04-08 0

-

有关音频编码标准的发展现状及其趋势2021-04-14 0

-

嵌入式系统开源软件发展现状如何?2021-04-26 0

-

汽车用基础电子元器件发展现状与趋势是什么?2021-05-17 0

-

广播电视发展现状及趋势2021-07-21 0

-

云计算产业发展现状及趋势2021-07-27 0

-

深圳IC设计产业发展现状2009-12-17 486

-

通信电源产业链发展现状与趋势分析2013-05-20 3269

-

平板显示产业的发展现状和存在问题的描述2017-10-19 1590

-

我国半导体产业发展现状如何?一窥半导体产业的现状2018-06-07 17570

-

国内智慧产业的发展现状2020-06-22 11355

-

【电子发烧友】2021中国嵌入式产业发展现状及趋势分析2021-09-01 632

全部0条评论

快来发表一下你的评论吧 !