先进封装形式及其在三维闪存封装中的可能应用

描述

先进封装形式及其在三维闪存封装中的可能应用

SiP

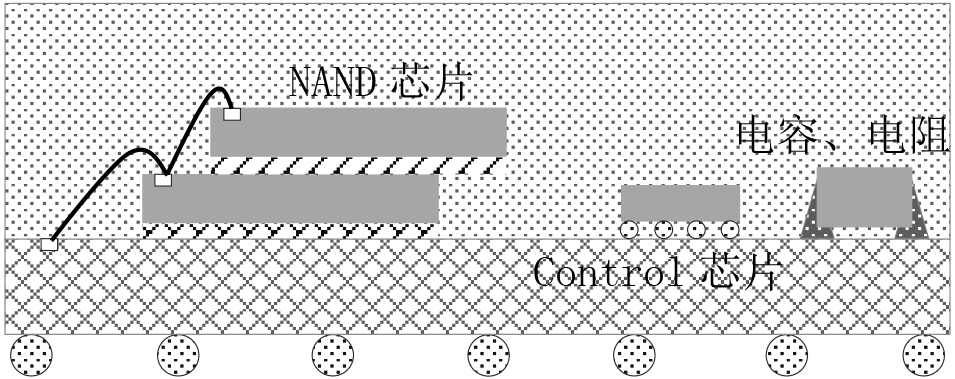

SiP 是将不同功能的芯片(例如存储器、处理器无源器件等)封装在同一个塑封体中,以此来实现一个完整功能的封装形式4.具有高集成、低功耗、良好的抗机械和化学腐蚀的能力以及高可靠性等优点如图 4 所示。

对照此概念,目前 3D NAND 应用中的Managed NAND(eMMC,UFS 等),eMCP 产品较类似且已广泛应用,即将堆叠的 NAND 芯片、倒装或金线连接的 Control芯片、以及电容电阻互连在一个封装体中,实现系统集成,同时根据产品需求的不同增加芯片的数量和种类,以此实现异构、异质集成咸少封装体积.降低系统成本。

图 4 SiP 封装结构图

Fan-in/Fan-out

Fan-in 封装是在晶圆上布 RDL,并植球,直接切制后形成单颗芯片。这种形式得到的单颗封装体的尺寸几乎与芯片的尺寸相同,且可以多晶圆同时加工,提高封装的作业效率。

但也因其 IO 局限在单颗芯片尺寸范围内,导致 I/0 数量被极大限制住,所以应用一般仅限在小型电子器件,并且不需要较多IO 需求的产品上。Fan-out 封装技术属于晶圆重构技术,将晶圆切制成单颗芯片后,重新布置在载体上,然后进行塑封、RDL、植球、切制日,从而得到面积大于芯片面积的封装体。

这样可以灵活把控 I/O 的间距及数量不受芯片尺寸的限制。Fan-out 工艺也可分为芯片先上(Die First)和芯片后上(Die Last)两种.相对于芯片先上.芯片后上具有塑封翘曲小和成品率高等优点,但是制造工艺相对复杂。

当前,市面上的三维闪存芯片封装的主流还是将芯片通过直接贴装在封装基板的表面上,然后采用金属线键合工艺实现芯片焊盘与基板电性能连接。

基板作为芯片封装的核心材料之一,其成本占据整个封装材料成本的 30%-50%;并且为了应对产品朝着轻薄小的方向发展,基板中的设计会越来越复杂,而且层数也会随之增加,导致基板的厚度增加.影响了总体的封装厚度,还致使基板的价格进一步提高。在线宽线径方面,15/15 u m(mSAP 工艺)已经是接近极限,想再进一步下探需要更换制作工艺,同时会带来成本或其他负面效果,并且也很难低于5um.单层的 P 厚度最薄也只能接近 15um。

RDI工艺是晶圆制造端较成熟的工艺,可 以达到1.5/1.5 u m 的线宽线距:在厚度方面,单层的 RDI厚度可以控制在 5~20 um 的范围之内,也是低于基板的厚度。

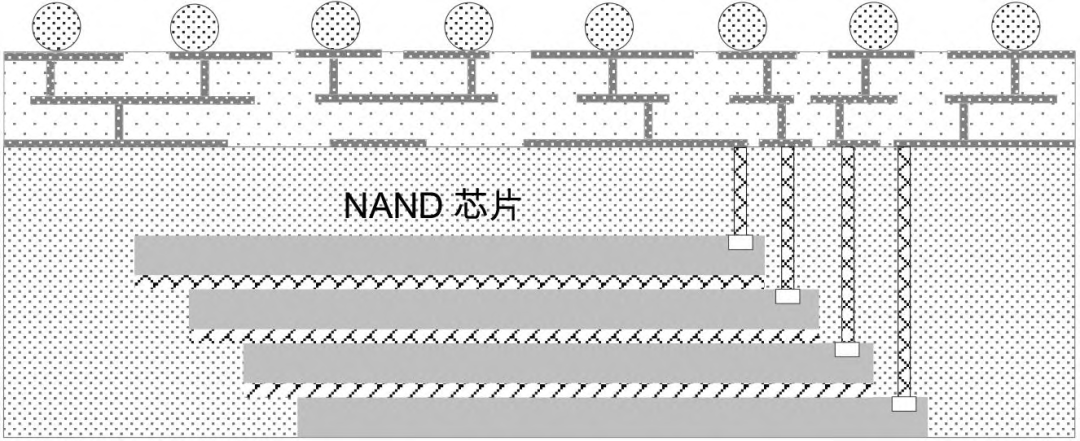

如将 Fan-out 应用在三维闪存芯片封装上,可起到提升信号速度,减少封装体厚度的作用。本文设想的结构如图 5 所示,将 NAND 芯片层错开堆叠(露出焊盘区).然后利用金属导电结构代替 WB 打线与外界信号连接,塑封后制作重新布线层和凸块以此实现内外的导通结构。

该结构的主要难点在于连接的问题,本文针对该难点采用激光打孔和做金属柱两种方法,激光打孔是需要在塑封体上进行钻孔,使孔底落在芯片焊盘上,然后再深孔内形成导电结构,从而连接 RDL 层实现电信号传输;金属柱则是先在芯片 Pad 上形成金属结构,然后进行塑封,然后打磨塑封体露出金属柱.实现与 RDL 层连接。

图 5 扇出型封装体的剖面结构示意图

2.5D/Chiplet

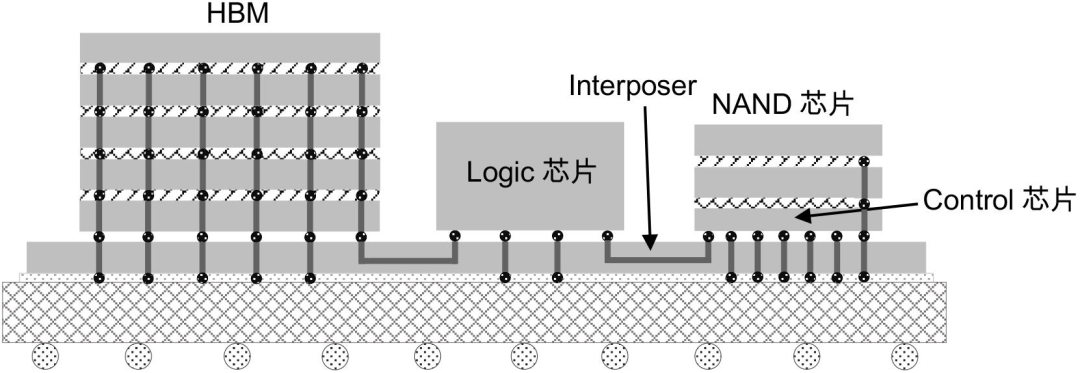

Chiplet 的封装被视为延续摩尔定律的新法宝,是将原 SoC 大尺寸的设计分散在较小的芯片上将多个芯片通过先进封装技术重新组合在一个 Si中介板上,形成一种“SiP”封装形式,以此来满足产品的需求。

应用 Chiplet 的优势首先在于利用 Si 中介板代替基板.将 NAND 芯片、DRAM芯片Lgic 芯片和 Control 芯片等异质芯片集成在 Si 中介板上是可以有效地解决热效应导致的异质芯片与基板之间热膨胀系数不匹配的问题,二是由于 Si 中介板采用的 TSV 技术,可以有效缩短电性传输路径,从而提高其传输的速度;其次,Si 中介板的威廉希尔官方网站 设计是可以根据异质芯片的不同需求而采取不同的工艺节点,这正好符合处理器、DRAM、NAND 的不同工艺现状,从而增加工艺的灵活性,缩短产品更新周期。

本文设想的结构如图 6 所示,结合 Chiplet 技术在 NAND 中的应用,可采用前文提到的 TSV 技术将DRAM 芯片和 Logic 芯片垂直堆叠连接成 HBM 结构,然后通过 Si interoser 与外界基板实现连接;单个的 Logic 芯片以倒装(FC)的形式与 Si interposer实现连接,并通过内部布线实现与 HBM 的电信连接:NAND 芯片和 Control 芯片垂直堆叠并通过 Siinterposer 实现与内部的 Logic 芯片和外部的基板工连;通过 Si interposer 实现系统内互连,达到高度集成的目的。

该结构的难点在于产品还存在散热等问题,目前,市面上还没有发现规模化的相关产品应用,因此,未来还是充满了挑战。

图 6 Chiplet 技术封装体的剖面结构示意图

本文内容源于【中国集成威廉希尔官方网站

】

审核编辑:汤梓红

-

#硬声创作季 【VFX三维渲染】何为半导体封装?用最简单的画面,让你全方位了解半导体封装技术Mr_haohao 2022-10-21

-

如何用labview在三维图里画多条线?2014-11-08 0

-

三维立体数字沙盘是是什么?2020-08-28 0

-

高速相机在三维运动康复中的应用案例2016-06-07 0

-

三维触控技术突破“二向箔”的束缚2016-12-19 0

-

晶圆级三维封装技术发展2020-12-28 0

-

安徽三维动画制作和二维动画有哪些区别呢?(一)2022-01-22 0

-

蔡坚:封装技术正在经历系统级封装与三维集成的发展阶段2021-01-10 2459

-

基于高温共烧陶瓷基板的三维互连技术2022-11-16 1569

-

三维封装技术介绍2023-03-25 3632

-

三维封装工艺流程与技术2023-05-08 3606

-

三维X射线显微镜半导体封装产品检测2023-06-27 626

-

什么是先进封装?先进封装技术包括哪些技术2023-10-31 2326

-

先进封装技术在三维闪存中的应用2023-12-08 818

-

先进封装技术在三维闪存产品中的应用探讨2023-12-14 953

全部0条评论

快来发表一下你的评论吧 !