半大马士革集成中引入空气间隙结构面临的挑战

制造/封装

描述

帮助imec确定使用半大马士革集成和空气间隙结构进行3nm后段集成的工艺假设

作者:泛林集团Semiverse™ Solution部门半导体工艺与整合工程师Assawer Soussou博士

随着芯片制造商向3nm及以下节点迈进,后段模块处理迎来挑战

半大马士革集成方案中引入空气间隙结构可能有助于缩短电阻电容的延迟时间

随着器件微缩至3nm及以下节点,后段模块处理迎来许多新的挑战,这使芯片制造商开始考虑新的后段集成方案。

在3nm节点,最先进的铜金属化将被低电阻、无需阻挡层的钌基后段金属化所取代。这种向钌金属化的转变带来减成图形化这一新的选择。这个方法也被称为“半大马士革集成”,结合了最小间距互连的减成图形化与通孔结构的传统大马士革。

互连线减成图形化的优点之一,是提供了转变至(更)高深宽比金属线的机会。但它也有缺点,那就是会增加电容。如果引入空气间隙结构,支持互连线隔离,则可以克服这种不良影响。因此,空气间隙常常被视作缩短电阻电容延迟时间的主要手段。

前文提出的半大马士革集成方案可结合完全空气间隙集成,用于最关键的最小间距金属层(M1和M2)。它也可以与传统的双大马士革或混合金属化方案相结合。

我们支持了imec的一项研究,对先进3nm节点后段集成方案进行分析。研究中,我们使用SEMulator3D®工艺模拟软件对半大马士革集成流程和引入空气间隙结构进行模拟。这帮助imec在试产线上进行硅晶圆处理之前,就能更好地了解集成潜在的挑战和相关的失败风险。该项目的目标是确定使用半大马士革集成和空气间隙结构进行3nm后段集成的工艺假设。

流程模拟

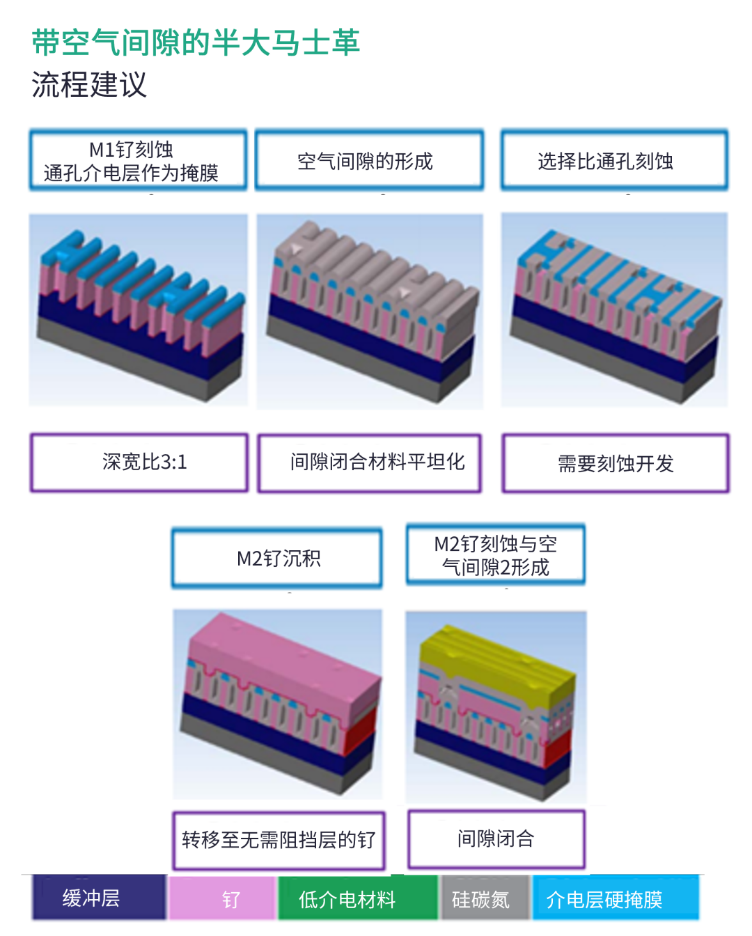

使用SEMulator3D对3nm后段方案的半大马士革空气间隙工艺流程进行模拟。图1展示了关键的工艺步骤,其中包括M1钌刻蚀步骤、随后的空气间隙闭合、完全自对准通孔图形化、完全自对准通孔/M2金属化、以及最后的M2图形化。

此次研究中,为了真实地再现空气间隙形状,我们根据imec 10nm半间距金属互连模块的透射电子显微镜 (TEM) 图像,对M1钌图形化和空气间隙闭合工艺步骤进行校准。

图1:3nm节点后段半大马士革空气间隙工艺流程

空气间隙方面的挑战

为了避免潜在的硅晶圆工艺失效,我们利用SEMulator3D研究了半大马士革空气间隙工艺流程中,空气间隙闭合相关的挑战和薄弱环节。

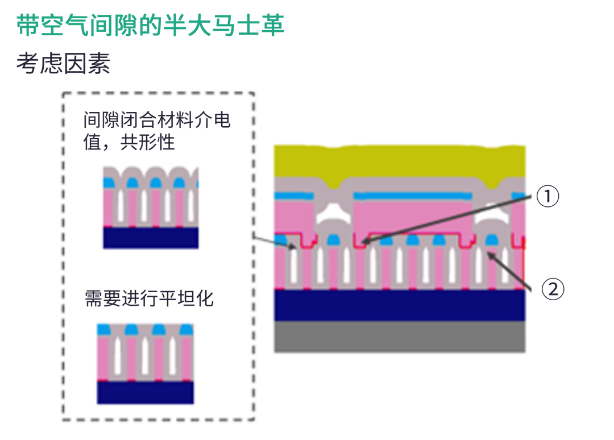

图2展示了3nm节点半大马士革空气间隙工艺面临的挑战。其中,该图突出展示了空气间隙闭合后进行平坦化、以保持介电常数k值和共形性的需求,以及空气间隙闭合控制这一关键的工艺挑战。

我们的模拟显示,为了避免引入空气间隙失败,M1和M2之间应该保留一段最小距离。换句话说,在完全自对准通孔刻蚀的第一步,必须使用对暴露的硅碳氮空气间隙闭合介电材料具有高选择比的工艺。

在随后的硅碳氮刻蚀工艺步骤中,为了与下层金属1钌相接,需要进行刻蚀工艺,使硅碳氮介电层产生较高的倾斜度。这可以减少对间隙闭合介电层的过度刻蚀,并在通孔刻蚀工艺中保持空气间隙闭合。图3左右的模拟结果分别展示了需要的二氧化硅与硅碳氮的刻蚀选择比,和理想的硅碳氮倾斜度。

图2:半大马士革空气间隙工艺流程挑战

图3:空气间隙闭合的薄弱环节

敏感性分析

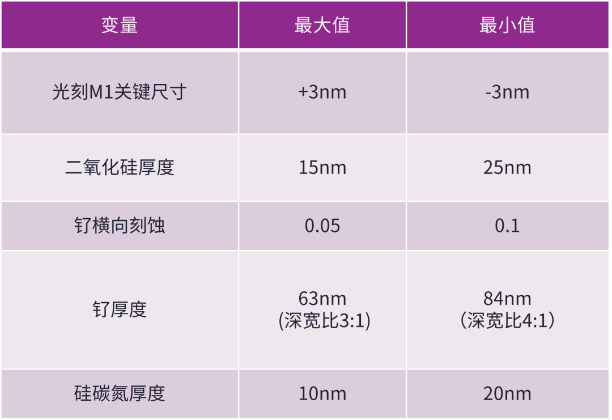

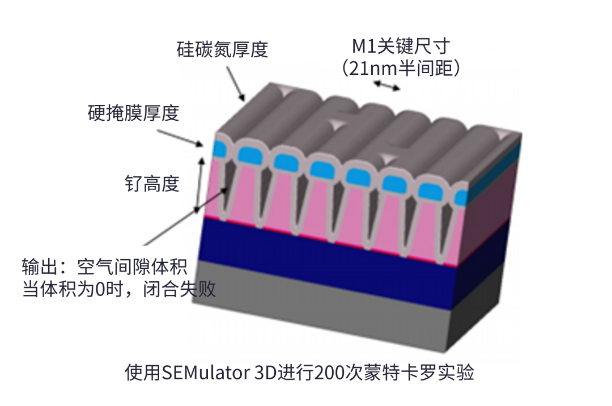

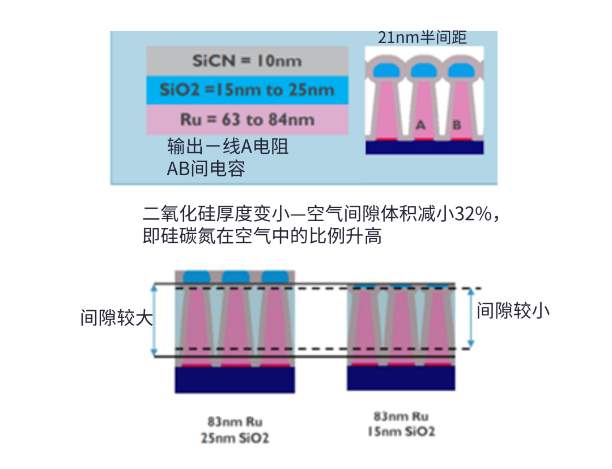

在模拟中,我们对可以控制和维持空气间隙闭合和体积的工艺参数进行敏感性分析。其间,通过改变M1光刻关键尺寸、硅碳氮间隙闭合介电层厚度、二氧化硅硬掩膜厚度、M1钌横向刻蚀和钌高度,我们在SEMulator3D上共进行了200次蒙特卡罗实验。相关工艺参数和评估参数范围的详细信息见图4。

图4:空气间隙闭合工艺敏感性分析

模拟表明,关键尺寸越小,硅碳氮沉积失败的风险越大,因此,造成空气间隙闭合失败的最大因素是金属1关键尺寸和较小的二氧化硅硬掩膜厚度。此外,金属1钌厚度和二氧化硅硬掩膜厚度也是影响空气间隙体积的最大因素(见图5)。

图5:工艺敏感性研究结果:

对空气间隙闭合失败影响的研究(上2图)

对空气间隙体积影响的研究(下2图)

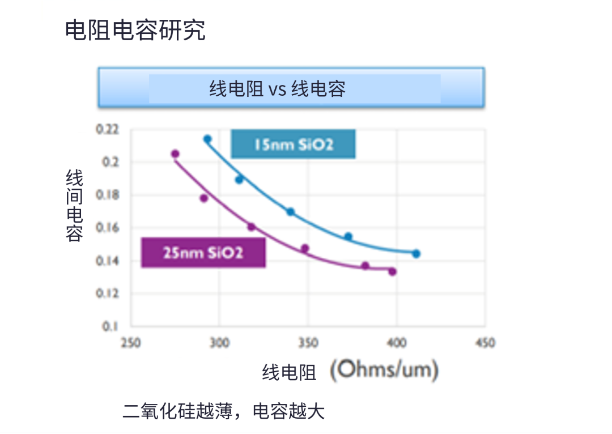

空气间隙体积敏感性研究的结果被用于量化对电阻电容降低的影响,相应的分析结果见图6。

图6:空气间隙体积工艺敏感性研究及其对电阻电容降低的影响

主要收获

在这项研究中,我们使用SEMulator3D模拟为3nm节点后段进行半大马士革空气间隙工艺的流程。为了确定为3nm节点后段进行半大马士革集成的最佳工艺,模拟研究了潜在的薄弱环节和工艺挑战。

工艺流程模拟显示,空气间隙材料的选择和刻蚀工艺是半大马士革和空气间隙工艺方案能否成功的关键。这些工艺模型非常有价值,因为imec不用经历耗时、耗财的硅晶圆制造过程,就能研究3nm后段工艺方案的关键工艺。

鸣谢

由衷感谢Gayle Murdoch和imec同意我们分享这项研究。此研究获得了Pin3s ECSEL Joint Undertaking的支持。

- 相关推荐

-

铁匠铺锻打大马士革花纹钢酸洗之后花纹确实够漂亮锻打 铁匠 大马士革 #硬声创作季Hello,World! 2022-09-27

-

触摸屏在车载应用中面临巨大的挑战2014-06-19 0

-

调试速度高达几个Gb每秒的连接时所面临的挑战2021-03-01 0

-

USB 2.0结构是怎样构成的?USB 2.0面临哪些测试挑战?2021-05-10 0

-

如何采用铜互连单大马士革工艺制作超厚金属铜集成电感的概述2018-05-19 20316

-

12吋晶圆集成威廉希尔官方网站 芯片制程工艺与工序后端BEOL的详细资料说明2019-04-10 3001

-

使用半大马士革工艺流程研究后段器件集成的工艺2023-10-24 869

-

什么是铜互连?为什么铜互连非要用双大马士革工艺?2023-11-14 8517

-

半大马士革工艺:利用空气隙减少寄生电容2024-11-19 532

-

大马士革铜互连工艺详解2024-12-04 846

-

铜互连双大马士革工艺的步骤2024-12-10 447

全部0条评论

快来发表一下你的评论吧 !