影响射频系统性能的因素有哪些呢?

描述

(1)

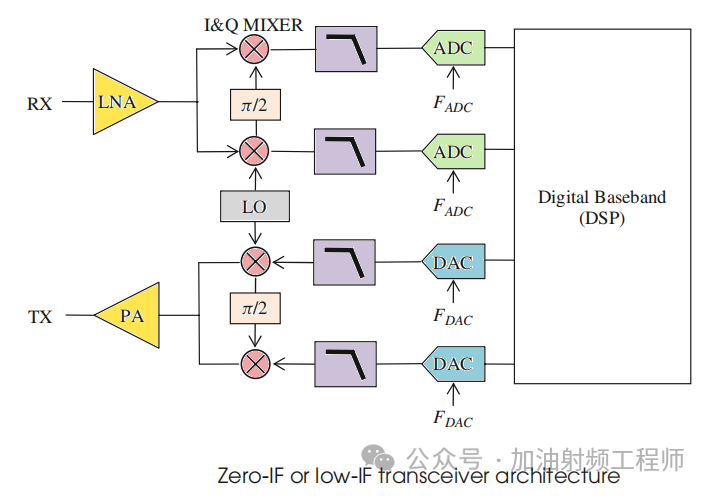

现在芯片越来越集成,一个小小的芯片集成一个或者很多个射频系统,已经不是什么稀罕事。

在芯片的架构中,通常会用零中频或者低中频架构,因为这些架构简单,而且不需要像超外差接收机一样,使用片外滤波器。

如下图所示。

不过射频上是简单了,但是其实需要数字部分做很多的校准工作。

那么都是哪些实际器件中的不理想性,会对系统的性能产生影响呢?

(2)

首先,是热噪声和闪烁噪声。

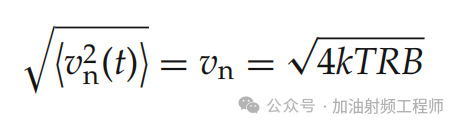

所有的实际器件,都会有电子的随机运动,而这些运动会产生随机噪声,即热噪声。

比如说,一个无源的电阻R,在温度T K下,就会产生噪声电压:

如果这个电阻的负载的大小,与该电阻大小相等,那么输入到负载的噪声功率,则是我们经常看到的KTB,如下图所示。如果不考虑系统带宽,温度为T为290K,那Pn就是我们熟知的-174dBm/Hz。

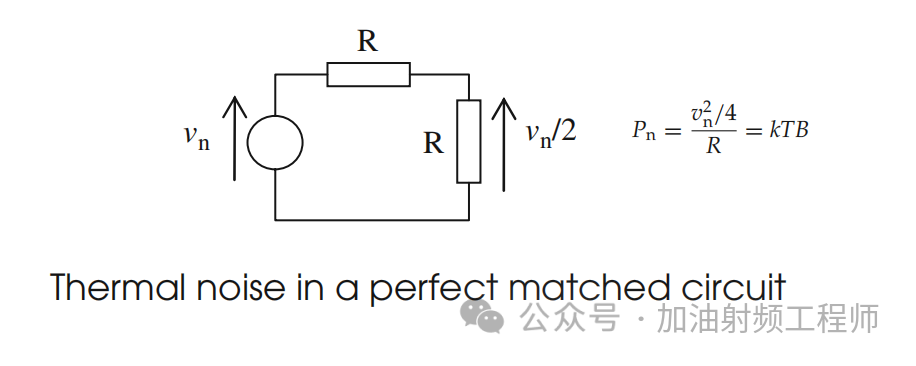

还有,有源器件中的闪烁噪声(flicker noise),又称为1/f noise。

因为闪烁噪声位于直流(DC)附近,所以对零中频架构的影响很大,对低中频架构的影响次之。

(3)

接着,是LO相位噪声。

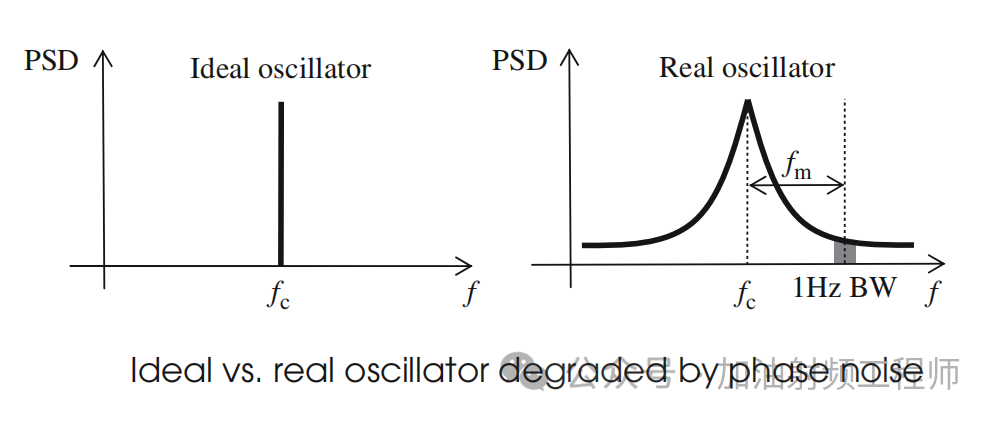

理想振荡器的输出,在频域可以用δ函数来表示,但是实际的相位噪声,往往会有裙摆,如下图所示。

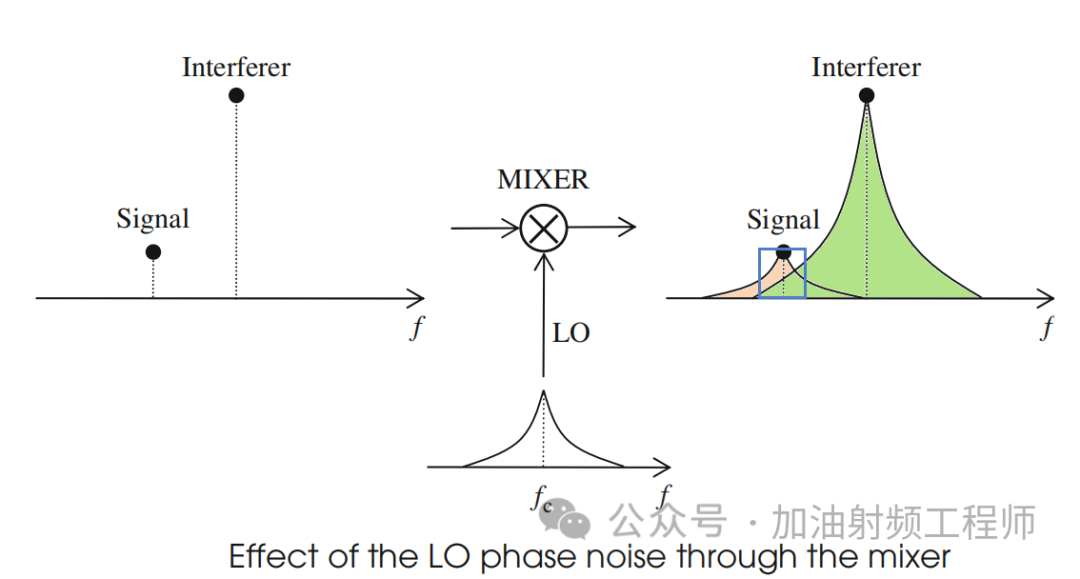

收发机中LO的相噪的影响,如下图所示,蓝框表示有用信号的带宽。

一方面来源于本振相噪带与信号相乘,会带来带内噪声的增加;另一方面,来源于干扰信号与本振的相噪混频,会造成带内噪声的增加(即倒易混频)。

(4)

再者,是采样抖动。

ADC和DAC是收发机种模拟和数字的边界。

在模拟和数字进行转换的时候,需要用到采样时钟。

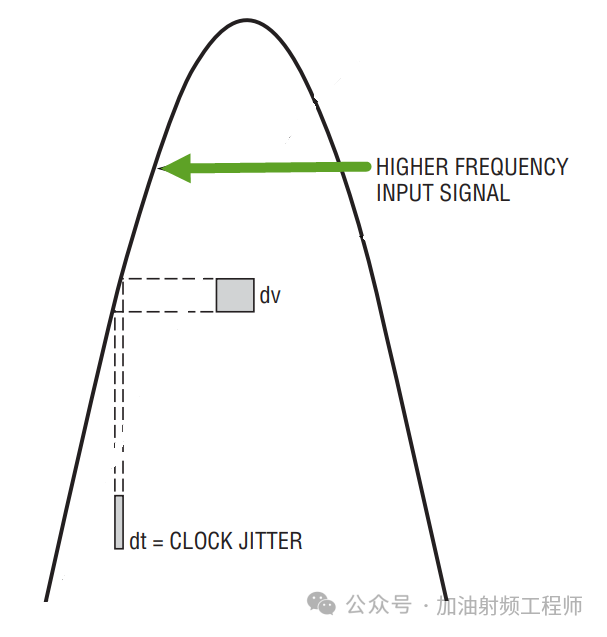

采样时钟,本质上也是一个振荡信号。如前面所示,实际的振荡信号会有相噪,等效于时域的抖动。

因为这个时域的抖动,会造成采样的误差,从而产生噪声。

(5)

其次,是载波频率偏移(CFO,carrier Frequency offset)和采样频率偏移(SFO)。

在通信系统中,载波频率一般是由锁相环产生的。

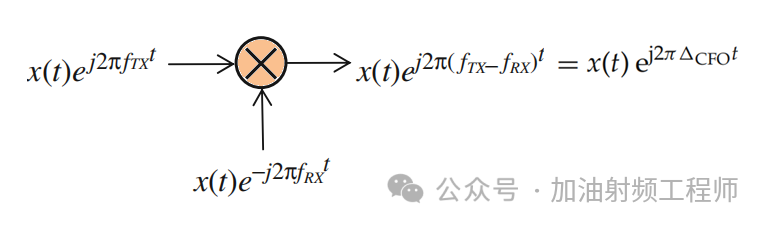

但是因为TX和RX的载波频率会有一点点的不同,所以,接收机变频后的频率会有残余频率误差,称为CFO,即载波频率偏移。如下图所示。

同样的,ADC和DAC的采样频率也会有差别,称之为采样频率偏移,即SFO,同样也会影响系统性能。

(6)

接着,是DAC和ADC的量化噪声和截断。

ADC和DAC在进行模数转换的时候,会产生量化噪声,从而产生有限的SNR。

所以在设计接收机的时候,通常ADC的前级需要有足够的增益,保证ADC本身的噪声电平与其输入的热噪声电平(由前面级威廉希尔官方网站 产生)相比,要足够小,可以忽略不计。

而ADC的截断效应,会限制信号的PAPR(Peak to Average Power Ratio,峰均比),从而恶化信号的SNR。

(7)

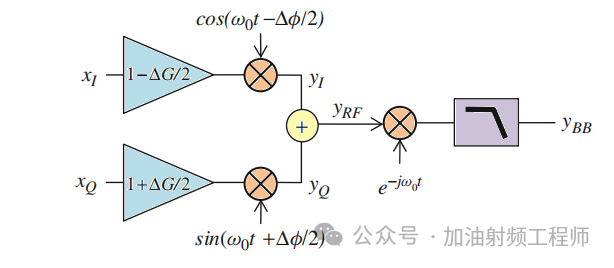

还有,正交不平衡。

在进行上变频或者下变频的时候,使用的是正交混频器。实际的正交混频器,I路和Q路,会有增益失配和相位失配,从而影响信号的SNR或者产生带外噪声。

(8)

还有,器件的非线性。

接收机的非线性,主要是对大信号干扰负责。即我们经常说到的互调抗扰性。

审核编辑:刘清

-

造成微波暗室性能精度差的因素有哪些?2019-07-30 0

-

镜像对系统性能的影响有哪些?2021-03-29 0

-

影响存储器访问性能的因素有哪些?2021-04-19 0

-

如何提高FPGA的系统性能2021-04-26 0

-

影响相干光学采集系统的因素有哪些?2021-05-08 0

-

LED大屏质量得以保证的几大因素有哪些呢?2021-05-31 0

-

电信级视频监控系统的关键因素有哪些?2021-06-01 0

-

lcd的显示速度跟哪些因素有关呢?2022-01-12 0

-

TD-SCDMA射频系统性能评估方案及系统介绍2010-03-05 402

-

影响锌锰电池电性能参数检测的因素有哪些?2009-10-28 1961

-

使系统性能达到最佳的设计考虑因素和规格2019-02-21 2551

-

射频电缆的衰减一般与哪些因素有联系2021-03-26 4104

-

限制机器人力控性能的因素有哪些2023-11-08 848

-

贴片绕线电感性能的影响因素有哪些2024-01-22 173

-

影响pcb蚀刻性能的五大因素有哪些?2024-03-28 957

全部0条评论

快来发表一下你的评论吧 !