传统封装和先进封装的区别

描述

来源:半导体封装工程师之家

半导体器件有许多封装形式,按封装的外形、尺寸、结构分类可分为引脚插入型、表面贴装型和高级封装三类。从DIP、SOP、QFP、PGA、BGA到CSP再到SIP,技术指标一代比一代先进。总体说来,半导体封装经历了三次重大革新:第一次是在20世纪80年代从引脚插入式封装到表面贴片封装,它极大地提高了印刷威廉希尔官方网站 板上的组装密度;第二次是在20世纪90年代球型矩阵封装的出现,满足了市场对高引脚的需求,改善了半导体器件的性能;芯片级封装、系统封装等是现在第三次革新的产物,其目的就是将封装面积减到最小。半导体产品在由二维向三维发展,从技术发展方向半导体产品出现了系统级封装(SiP)等新的封装方式,从技术实现方法出现了倒装(FlipChip),凸块(Bumping),晶圆级封装(Waferlevelpackage),2.5D封装(interposer,RDL等),3D封装(TSV)等先进封装技术。

传统封装vs先进封装

传统封装概念从最初的三极管直插时期后开始产生。传统封装过程如下:将晶圆切割为晶粒(Die)后,使晶粒贴合到相应的基板架的小岛(LeadframePad)上,再利用导线将晶片的接合焊盘与基板的引脚相连(WireBond),实现电气连接,最后用外壳加以保护(Mold,或Encapsulation)。典型封装方式有DIP、SOP、TSOP、QFP等。

先进封装主要是指倒装(FlipChip),凸块(Bumping),晶圆级封装(Waferlevelpackage),2.5D封装(interposer,RDL等),3D封装(TSV)等封装技术。先进封装在诞生之初只有WLP,2.5D封装和3D封装几种选择,近年来,先进封装的发展呈爆炸式向各个方向发展,而每个开发相关技术的公司都将自己的技术独立命名注册商标,如台积电的InFO、CoWoS,日月光的FoCoS,Amkor的SLIM、SWIFT等。尽管很多先进封装技术只有微小的区别,大量的新名词和商标被注册,导致行业中出现大量的不同种类的先进封装,而其诞生通常是由客制化产品的驱动。

先进封装优势

先进封装提高加工效率,提高设计效率,减少设计成本。

先进封装主要包括倒装类(FlipChip,Bumping),晶圆级封装(WLCSP,FOWLP,PLP),2.5D封装(Interposer)和3D封装(TSV)等。以晶圆级封装为例,产品生产以圆片形式批量生产,可以利用现有的晶圆制备设备,封装设计可以与芯片设计一次进行。这将缩短设计和生产周期,降低成本。

先进封装提高封装效率,降低产品成本。

随着后摩尔定律时代的到来,传统封装已经不再能满足需求。传统封装的封装效率(裸芯面积/基板面积)较低,存在很大改良的空间。芯片制程受限的情况下,改进封装便是另一条出路。举例来说,QFP封装效率最高为30%,那么70%的面积将被浪费。DIP、BGA浪费的面积会更多。

先进封装以更高效率、更低成本、更好性能为驱动。

先进封装技术于上世纪90年代出现,通过以点带线的方式实现电气互联,实现更高密度的集成,大大减小了对面积的浪费。SiP技术及PoP技术奠定了先进封装时代的开局,2D集成技术,如WaferLevelPackaging(WLP,晶圆级封装),Flip-Chip(倒晶),以及3D封装技术,ThroughSiliconVia(硅通孔,TSV)等技术的出现进一步缩小芯片间的连接距离,提高元器件的反应速度,未来将继续推进着先进封装发展的脚步。

先进封装技术

Flip-Chip & Bumping

FlipChip指的是芯片倒装,以往的封装技术都是将芯片的有源区面朝上,背对基板和贴后键合。而FlipChip则将芯片有源区面对着基板,通过芯片上呈阵列排列的焊料凸点(Bumping)实现芯片与衬底的互联。硅片直接以倒扣方式安装到PCB从硅片向四周引出I/O,互联长度大大缩短,减小了RC(Resistance-Capacitance)延迟,有效的提高了电性能。

FlipChip的优势主要在于以下几点:小尺寸,功能增强(增加I/O数量),性能增强(互联短),提高了可靠性(倒装芯片可减少2/3的互联引脚数),提高了散热能力(芯片背面可以有效进行冷却)。

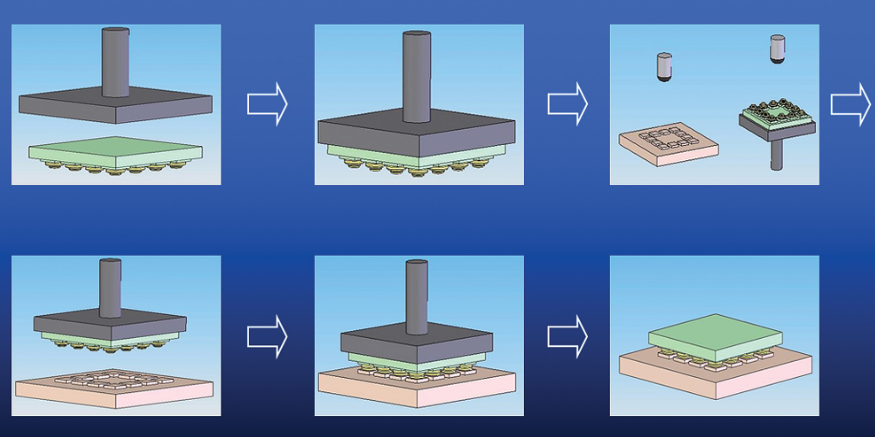

倒装芯片晶体贴装技术

Bumping是一种新型的芯片与基板间电气互联的方式。

可以通过小的球形导电材料实现,这种导电球体被称为Bump,制作导电球这一工序被称为Bumping。当粘有Bump的晶粒被倒臵(Flip-Chip)并与基板对齐时,晶粒便很容易的实现了与基板Pad(触垫)的连接。相比传统的引线连接,Flip-Chip有着诸多的优势,比如更小的封装尺寸与更快的器件速度。

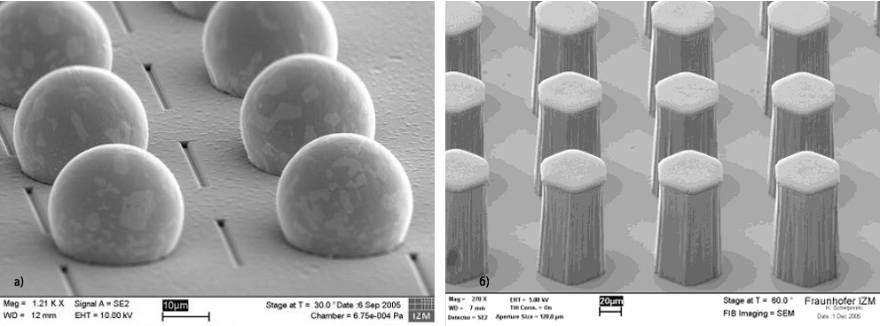

焊球端子和柱式端子

FlipChip的关键一步是Bumping,可以通过在晶圆上制作外延材料来实现。

当芯片制作工序完成后,制造UBM(Underbumpmetallization)触垫将被用于实现芯片和威廉希尔官方网站 的连接,Bump也会被淀积与触点之上。焊锡球(Solderball)是最常见的Bumping材料,但是根据不同的需求,金、银、铜、钴也是不错的选择。对于高密度的互联及细间距的应用,铜柱是一种新型的材料。焊锡球在连接的时候会扩散变形,而铜柱会很好的保持其原始形态,这也是铜柱能用于更密集封装的原因。

FlipChip产品对应不同bumping类型增长速度不一。

根据Yole预测,采用倒装芯片技术的集成威廉希尔官方网站 出货量将保持稳定增长,预计产能将以9.8%的复合年增长率扩张,从2014年的约合1600万片12寸晶圆增长到2020年的2800万片。终端应用主要为计算类芯片,如台式机和笔记本电脑的CPU、GPU和芯片组应用等。

其中镀金晶圆凸点(Au-platedwaferbumping)将稳定增长,由于IC显示驱动器(4K2K超高清电视和高清晰度、大屏幕平板电脑和智能手机)的市场驱动。预计产能将以4%的复合年增长率扩大,从2014年的430万片增长到2020年的540万片。

金钉头凸点(Austudbumping)产能将略有下滑,从2014年的30.4万片降到2020年的29.3万片,主要原因是射频器件从倒装芯片转移至晶圆级芯片尺寸封装(WLCSP)。但是,新兴应用的需求将增加,如CMOS图像传感器模组、高亮度LED等。

中道封装技术需求增长,将带来行业上下游的跨界竞争。针对3DIC和2.5D中介层平台的“中端工艺(middleend-process)”基础设施的出现将使Fab和IDM受益,并在较小程度上分给OSAT。2.5D中介层平台的发展将会产生价值的转移,从衬底供应商转向前端代工厂。

2.5D封装:RDL&中介层

RDL(Redistributionlayer,再分布层):在晶圆水平上,触点再分布可以很高效的进行。再分布层用于使连线路径重新规划,落到我们希望的区域,也可以获得更高的触点密度。再分布的过程,实际上是在原本的晶圆上又加了一层或几层。首先淀积的是一层电介质用于隔离,接着我们会使原本的触点裸露,再淀积新的金属层来实现重新布局布线。UBM在这里会被用到,作用是支撑焊锡球或者其他材料的接触球。

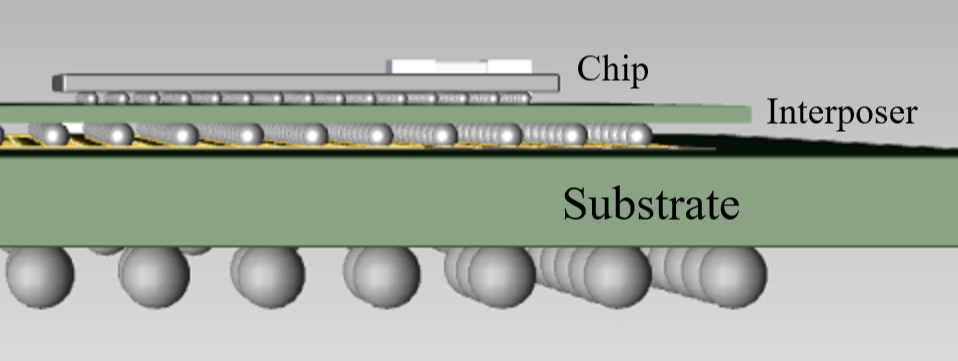

中介层(Interposer):指的是焊锡球和晶粒之间导电层。它的作用是扩大连接面,使一个连接改线到我们想要的地方。与再分布层作用类似。

中间层(Interposer)示意

3D封装:TSV,PoP和MEMS

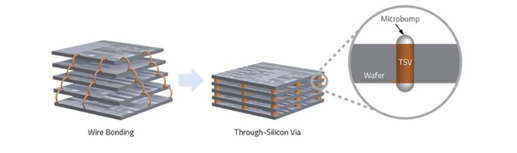

TSV(Through-siliconvia,硅通孔):Bump和RDL会占用芯片接合到基板上的平面面积,TSV可以将芯片堆叠起来使三维空间被利用起来。更重要的是,堆叠技术改善了多芯片连接时的电学性质。引线键合可以被用于堆叠技术,但TSV吸引力更大。TSV实现了贯穿整个芯片厚度的电气连接,更开辟了芯片上下表面之间的最短通路。芯片之间连接的长度变短也意味着更低的功耗和更大的带宽。TSV技术最早在CMOS图像传感器中被应用,未来在FPGA、存储器、传感器等领域都将被应用。根据Yole预测,2016~2021年,应用TSV技术的晶圆数量将以10%的年复合增长率增长。3D存储芯片封装也会在将来大量的用到TSV。

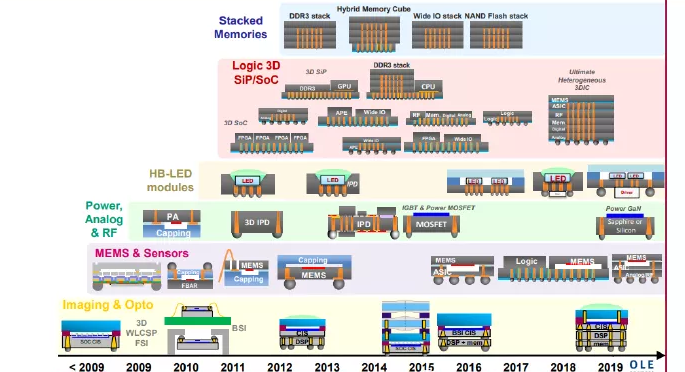

3DIC和TSV技术演进路径

TSV技术示意图

PoP(PackageonPackage,堆叠封装):PoP是一种将分离的逻辑和存储BGA(Ballgridarray,球状引脚栅格阵列)包在垂直方向上结合起来的封装技术。在这种结构中,两层以上的封装单元自下而上堆叠在一起,中间留有介质层来传输信号。PoP技术增大了器件的集成密度,底层的封装单元直接与PCB板接触。传统的PoP是基于基板的堆叠,随着存储器对高带宽的需求,球间间隔要求更小,未来将会与FOWLP技术相结合,做基于芯片的堆叠。

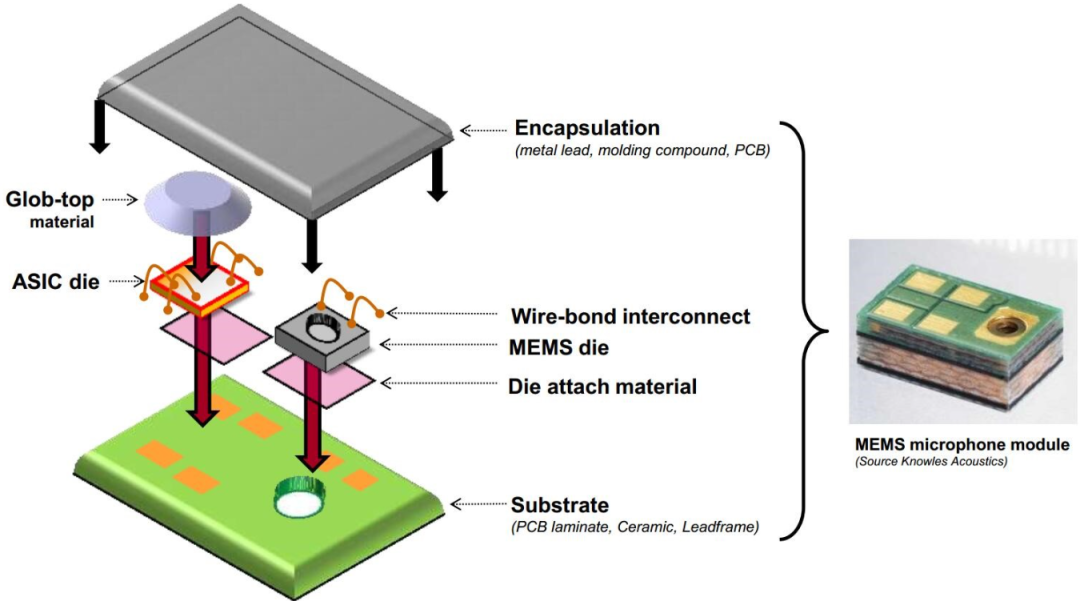

MEMS封装:微机电系统在近些年应用越来越广泛,随着传感器、物联网应用的大规模落地,MEMS封装也备受关注。MEMS的封装不同与集成威廉希尔官方网站 封装,分为芯片级、模组级、卡级、板级、门级等多元垂直分级封装,设计时也需考虑不同模组间的相互影响。目前MEMS封装市场规模在27亿美元左右,20162020年间将会维持16.7%的年复合增长率高速增长。其中RFMEMS封装市场是主要驱动,20162020年间,年复合增长率高达35.1%。

MEMS封装技术示意图

在整个MEMS生态系统中,MEMS封装发展迅速,晶圆级和3D集成越来越重要。主要的趋势是为低温晶圆键合等单芯片集成开发出与CMOS兼容的MEMS制造工艺。另一个新趋势是裸片叠层应用于低成本无铅半导体封装,这种技术可为量产带来更低的成本和更小的引脚封装。但是,MEMS器件的CMOS和3D集成给建模、测试和可靠性带来挑战。

FIWLP&FOWLP,PLP

首先要提及Wafer-levelpackaging(WLP,晶圆级封装)的概念。在传统封装概念中,晶圆是先被切割成小的晶粒,之后再进行连接和塑封。而晶圆级封装工序恰好相反,晶圆级封装将晶粒在被切割前封装完成,保护层将会被附着在晶圆的正面或是背面,威廉希尔官方网站 连接在切割前已经完成。

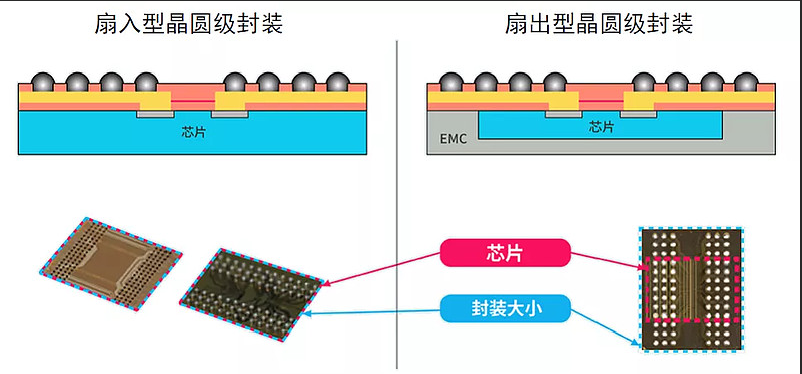

FIWLP:Fan-inWafer-levelpackaging,又称WLCSP(Wafer-levelChipScalePackage),扇入式晶圆级封装,也就是传统的晶圆级封装,切割晶粒在最后进行,适用于低引脚数的集成威廉希尔官方网站 。随着集成威廉希尔官方网站 信号输出的引脚数目的增加,焊锡球的尺寸也就变得越来越严格,PCB对集成威廉希尔官方网站 封装后尺寸以及信号输出接脚位臵的调整需求得不到满足,因此衍生出了扇出型晶圆级封装。扇入晶圆级封装的特征是封装尺寸与晶粒同大小。

FOWLP:Fan-outWafer-levelpackaging,扇出式晶圆级封装,开始就将晶粒切割,再重布在一块新的人工模塑晶圆上。它的优势在于减小了封装的厚度,增大了扇出(更多的I/O接口),获得了更优异的电学性质及更好的耐热表现。

FIWLP与FOWLP用途不同,均为今后的主流封装手段。FIWLP在模拟和混合信号芯片中用途最广,其次是无线互联,CMOS图像传感器也采用FIWLP技术封装。FOWLP将主要用于移动设备的处理器芯片中。根据Yole的预测,2018年以前FOWLP的主要驱动为苹果智能手机的处理器芯片,2018年以后的FOWLP的主要驱动除了其他安卓手机处理器的增长,主要是高密度FOWLP在其他处理芯片的应用,如AI、机器学习、物联网等领域。

FIWLP与FOWLP技术示意图

PLP:全称Panel-levelpackaging,平板级封装,封装方法与FOWLP类似,只不过将晶粒重组于更大的矩形面板上,而不是圆形的晶圆。更大的面积意味着节约更多的成本,更高的封装效率。而且切割的晶粒为方形,晶圆封装会导致边角面积的浪费,矩形面板恰恰解决了浪费问题。但也对光刻及对准提出了更高的要求。

审核编辑:汤梓红

- 相关推荐

- 半导体

- 威廉希尔官方网站 板

- BGA

- 先进封装

-

关于LED封装的不同,COB封装与传统LED封装的区别2018-02-02 8597

-

SMT里面区别于传统的芯片封装有哪些形式?2022-06-27 2306

-

#硬声创作季 先进封装技术详解——什么是良率?什么是晶圆级封装?什么是2.5D封装?Mr_haohao 2022-10-21

-

#硬声创作季 【科普向】传统封装与先进封装有何差异?——为什么需要先进封装Mr_haohao 2022-10-21

-

先进封装四要素及发展趋势电子学习 2022-12-10

-

先进封装对比传统封装的优势及封装方式2020-10-21 30438

-

SiP与先进封装有什么区别2023-05-19 1837

-

什么是先进封装?先进封装和传统封装区别 先进封装工艺流程2023-08-11 3345

-

什么是先进封装?和传统封装有什么区别?2023-08-14 1763

-

传统封装和先进封装的区别在哪2023-08-28 1652

-

HRP晶圆级先进封装替代传统封装技术研究2023-11-18 492

-

HRP晶圆级先进封装替代传统封装技术研究(HRP晶圆级先进封装芯片)2023-11-30 2175

-

COB封装与传统封装的区别及常见问题2024-01-30 5345

-

先进封装与传统封装的区别2024-07-18 3552

-

先进封装的重要设备有哪些2024-10-28 336

全部0条评论

快来发表一下你的评论吧 !