摩尔定律的终结:芯片产业的下一个胜者法则是什么?

描述

摩尔定律走下神坛,谁会是芯片下一个制胜法则?

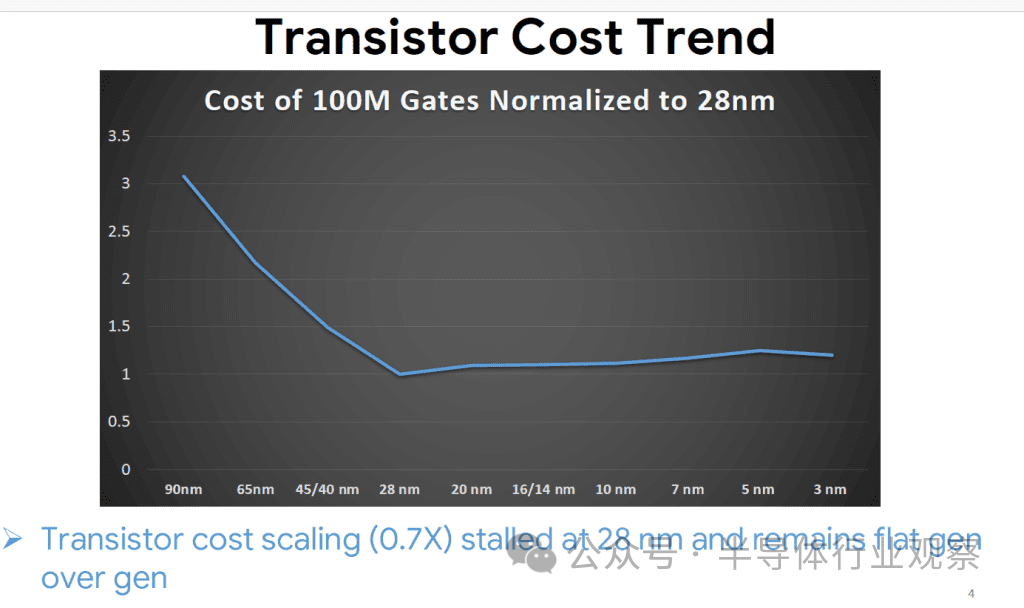

在动态的半导体技术领域,围绕摩尔定律的持续讨论经历了显着的演变,其中最突出的是 MonolithIC 3D 首席执行官Zvi Or-Bach于2014 年的主张。他关于晶体管成本缩减在 28 nm 达到关键节点的说法引起了广泛关注。

最近,谷歌的 Milind Shah 在 IEDM 2023 的短期课程中验证了这一说法。这一明确的说法“晶体管成本缩放 (0.7 倍) 在 28 纳米处停滞不前,并且一代一代之间保持持平”,这证实了之前的说法。最初在 2014 年的公众观点和博客中预见到了摩尔定律的结论。

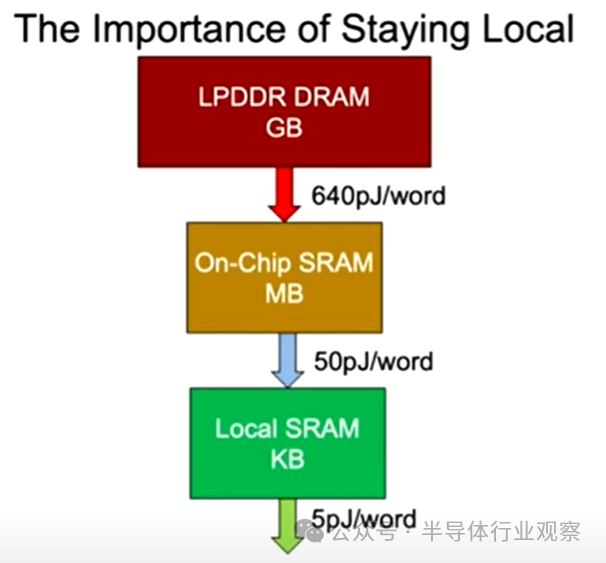

尽管成本扩展停滞不前,为什么业界仍在推动更小的晶体管,目标是令人难以置信的 1 nm 节点?答案在于系统级的好处。正如 NVIDIA 首席科学家 Bill Dally 的图表所示。

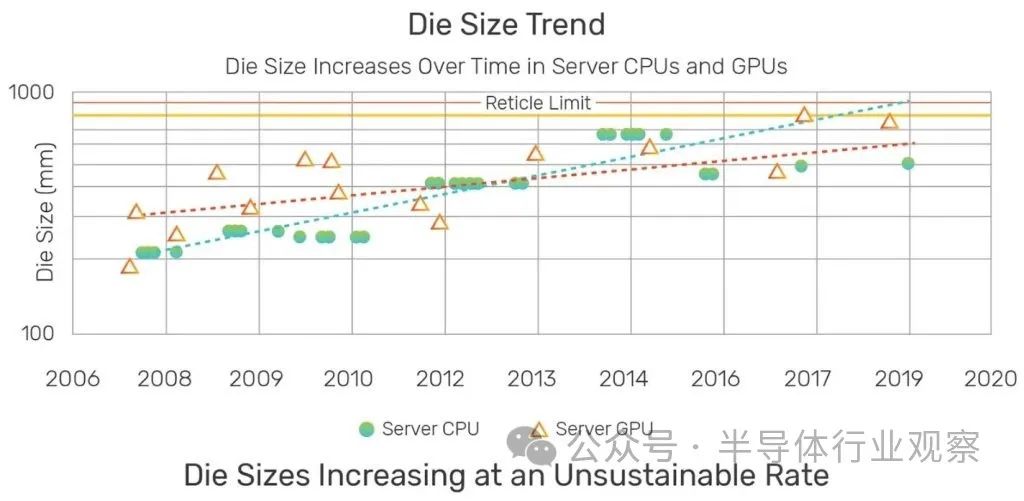

这反过来又推动了 CPU 和 GPU 等领先计算设备达到甚至更大尺寸的趋势。对更小节点的追求使得芯片上的组件集成更加紧密,从而进一步提高性能和效率。

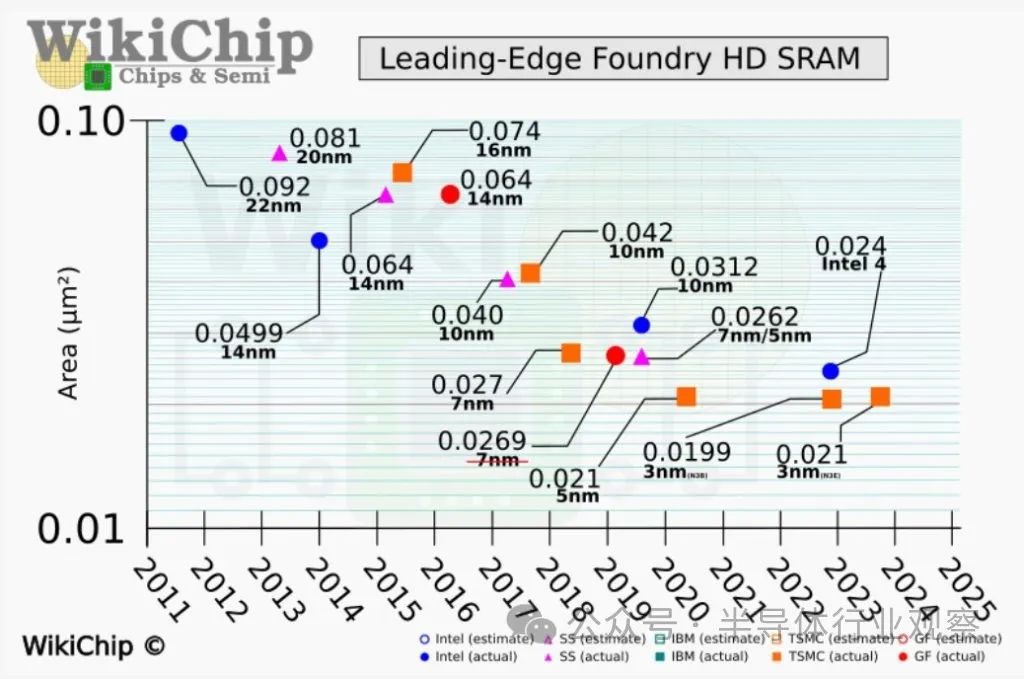

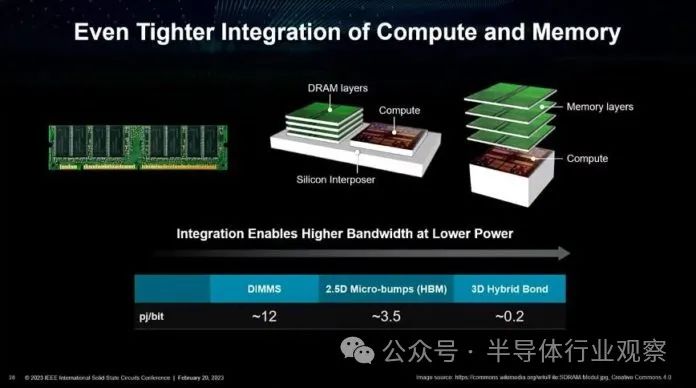

不幸的是,逻辑和存储器(DRAM、NAND)制造工艺非常不同。因此,它们是在不同的晶圆上生产的并且不能通过缩放来集成。更糟糕的是,SRAM 位单元缩放已停止在 5 纳米节点。

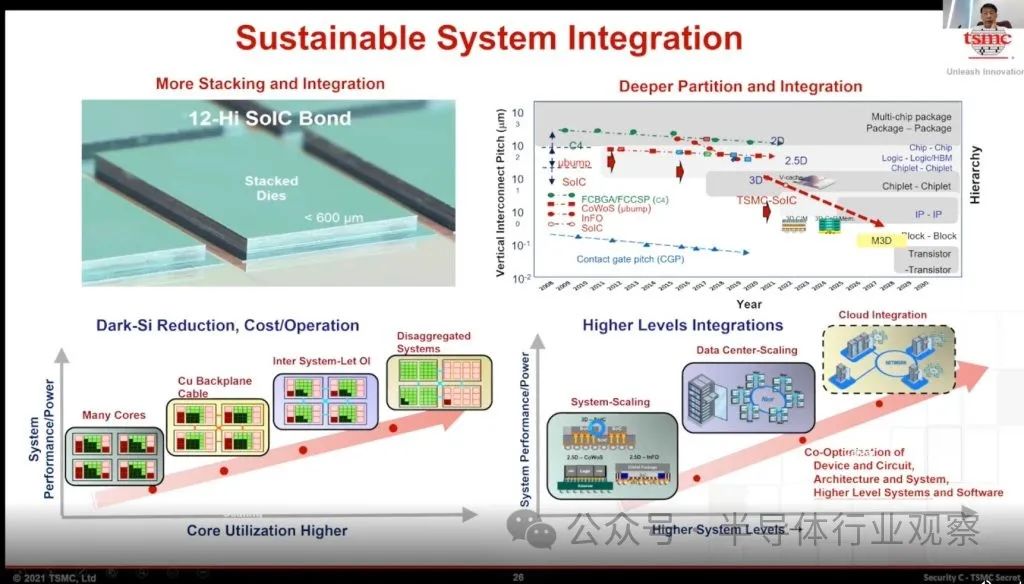

AMD 和台积电似乎都 了解这些趋势,并在过去几年中采用了混合键合技术,以实现未来计算性能的进步。

虽然当前的实施(例如 AMD 的 3D V-Cache)是充分发挥 3D 集成潜力的垫脚石,但仍然存在重大障碍。其中包括架构思维的根本转变,从传统的边缘互连转向新颖的 3D 集成方法。此外,要实现广泛采用,还需要在系统级冗余、晶圆级集成、甚至片上射频网络方面进行创新

拯救摩尔定律的终极办法

正如IMEC 负责计算扩展的逻辑副总裁Julien Ryckaert所说:“整个半导体行业目前正在经历一场巨大的变革。十多年来,很明显,受摩尔定律(更具体地说是登纳德定律)启发的尺寸缩放不能用作预测 CMOS 技术节点未来的晴雨表。”

这源于我们现在称为“缩放墙”的几个因素。不仅扩展 CMOS 组件的特征尺寸变得极其困难和昂贵,而且行业在其复杂系统中也面临着严重的功率和速度障碍。

在技术层面,新的器件架构和缩放助推器——由威廉希尔官方网站 协同优化 (DTCO) 支持——可以在接下来的几个 CMOS 节点中保持一定的面积缩放。但是这些将不可避免地失去动力,或者至少不足以提供未来应用程序的系统扩展期望。

在架构级别,复杂的内存层次结构、多核和多线程以及单个片上系统 (SoC) 或小芯片中的核心专业化 (xPUs...) 已成为克服这些扩展的方法墙壁。

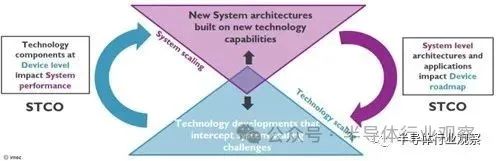

“我们今天面临的问题是,早期的创新很少是真正的系统架构到技术优化循环的结果。向前迈进的最大挑战将是解决可以解决主要系统扩展瓶颈的正确技术成分,以及探索一些技术中断如何能够实现新的计算方式。这就是系统技术协同优化 (STCO) 框架的目的。”Julien Ryckaert接着说。

在IMEC看来,由于自身需要在定义未来技术方面处于领先地位,因此他们现在必须通过系统扩展挑战来丰富其技术路线图。这种演变从根本上意味着我们需要跳出传统的“通用”技术产品,接受这样一个事实,即解决方案是由如人工智能、高性能计算 (HPC)和增强现实/虚拟现实等特定应用需求驱动的。

此外,最佳系统实施将是跨多种技术(例如极端 CMOS 逻辑缩放、高级 3D 封装、新型存储元件甚至 Si 光子学)的微妙优化的结果。到目前为止,这些不同的技术研究活动是分别进行的,每个活动都有自己的 DTCO 研究和路线图。

为了为系统驱动的扩展过渡做好准备,IMEC重组了核心项目,并将所有 DTCO 活动整合到一个项目中,该项目将研究所有核心技术项目中的技术到威廉希尔官方网站 优化,并用 STCO 计划补充了这个 DTCO 计划,这将确保 DTCO 研究和系统应用空间之间的联系。

“此 STCO 计划的目标是以自上而下的方式将未来的系统需求和瓶颈转化为技术需求。它还将探索利用独特和新颖的技术能力启用新架构的可能性。”Julien Ryckaert说。

据他所说,在IMEC的每个核心技术项目中,都开始了独立的研究活动,这些活动已经需要一定程度的系统评估。

一个很好的例子是其在 2022 年 VLSI 研讨会上展示的背面供电网络。这项工作是 3D 程序活动和逻辑活动共同开发电力传输系统解决方案的结果。背面技术严重影响逻辑缩放路线图,因为它需要 3D 技术功能,例如晶圆处理和硅通孔 (TSV) 处理。但要了解背面供电网络为何以及如何带来真正的系统性能优势,需要评估其在更复杂环境中的行为,并深入研究系统配置。

另一个例子是新兴存储器,其中一些预计将取代片上 SRAM。这样的内存方案必然会影响逻辑缩放路线图,只能在系统仿真框架中进行评估。更不用说其中一些记忆可能会以 3D 方式堆叠。

当我们开始为这些示例解决系统级挑战时,我们很快意识到,对于每个示例,所有技术解决方案都相互纠缠在一起。很明显,逻辑、内存和 3D 程序中的技术研究不能再在单独的“孤岛”中处理:它必须同时完成并由系统应用程序目标驱动。

”好消息是我们不是从头开始,因为我们已经有许多从系统角度分析的研究活动。我们现在需要的是将这些活动组织成一个共同的愿景,并为它们制定路线图。”Julien Ryckaert表示。

Julien Ryckaert进一步指出,IMEC的 DTCO/STCO 活动围绕系统的 3 个基本扩展壁进行了阐述:内存/带宽壁(即,如何以足够的速度获取数据以馈送逻辑内核)、功率/热壁(即,如何有效地处理功率传输和散热)和尺寸缩放墙。

IMEC希望能与其合作伙伴一起校准这个研究路线图,并确保我们正在为行业应对正确的挑战。这将需要与所有的合作伙伴进行深入讨论,而这些已经开始进行。

Julien Ryckaert表示:“尽管人们和我们一样认为这是一个雄心勃勃的计划目标,但我们确实看到了围绕这一倡议的很多兴奋。我们必须明智地选择我们的战斗,那些与未来系统扩展最相关的战斗,同时利用我们独特的技术能力。”

在他看来,真正的 STCO 研究需要将许多学科整合在一起,每个学科都处理广泛不同的规模,并在不同的抽象领域运作他们的科学。一个真正的挑战是在不丢失关键信息的情况下,构建从一个域到另一个域的一组适当的抽象层。这是从上到下和从下到上传播信息以执行完整系统优化的唯一方法。

而要正确地做到这一点,您不仅需要每个领域的所有正确专业知识,而且还需要这些学科彼此密切互动。Imec 拥有独特的基础设施,其中大多数学科都在同一屋檐下紧密合作。这有助于思想的交流、信息的顺利传播以及扩大对结果和解释的批判眼光。

“我对在这个 STCO 领域向前迈进感到非常兴奋,因为我们所有人,无论我们来自哪个领域,都明白在未来半导体研究中发挥作用的将是通过 STCO 框架。而 imec 是这种计划起飞的合适地点。”Julien Ryckaer说。

审核编辑:黄飞

-

小芯片能否“续写”摩尔定律?电子学习 2023-02-08

-

晶圆和摩尔定律有什么关系?2011-12-01 0

-

摩尔定律也适用于EPON芯片商用之路?2011-09-27 0

-

半导体行业的里程碑“摩尔定律”竟是这样来的2016-07-14 0

-

摩尔定律在测试领域有哪些应用?2021-04-13 0

-

请问摩尔定律死不死?2021-06-17 0

-

IC芯片的密度和计算机的速度能够一直按照摩尔定律前行吗?2021-07-22 0

-

摩尔定律,摩尔定律是什么意思2010-02-26 1591

-

摩尔定律_摩尔定律是什么2012-05-21 2788

-

摩尔定律变数下,中国“芯”如何迎接挑战2017-03-20 931

-

摩尔定律会不会终结_摩尔定律还适用吗2018-03-09 12287

-

摩尔定律的终结篇:英特尔受困 NVIDIA反受益2018-05-03 1011

-

2nm芯片符合摩尔定律吗 摩尔定律能够延续下去吗2022-07-05 1583

-

超越摩尔定律,下一代芯片如何创新?2023-11-03 939

-

中国团队公开“Big Chip”架构能终结摩尔定律?2024-01-09 840

全部0条评论

快来发表一下你的评论吧 !