解析FPGA竞争格局背后的驱动因素

可编程逻辑

描述

投资摘要:

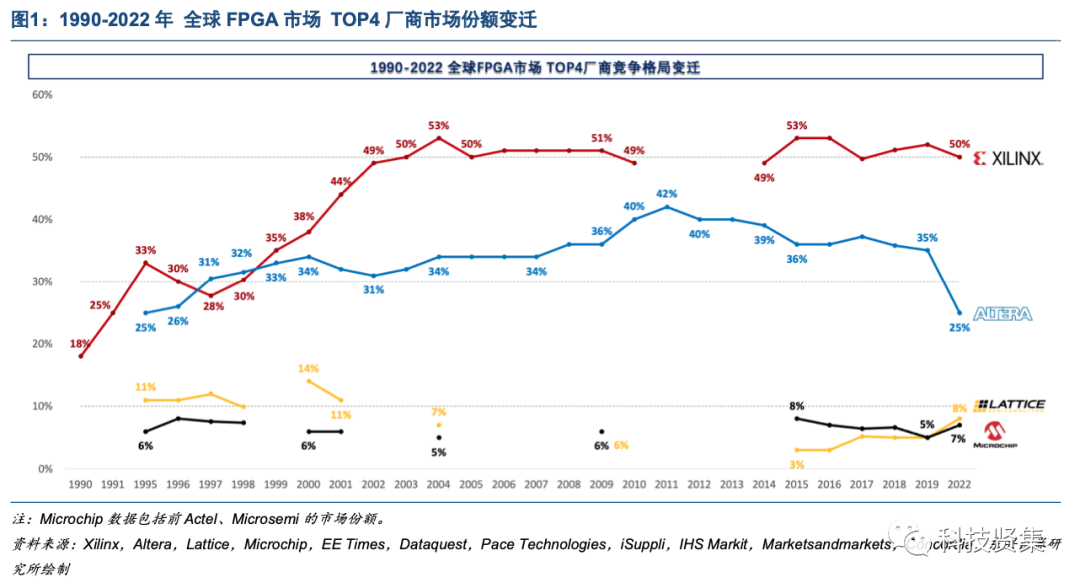

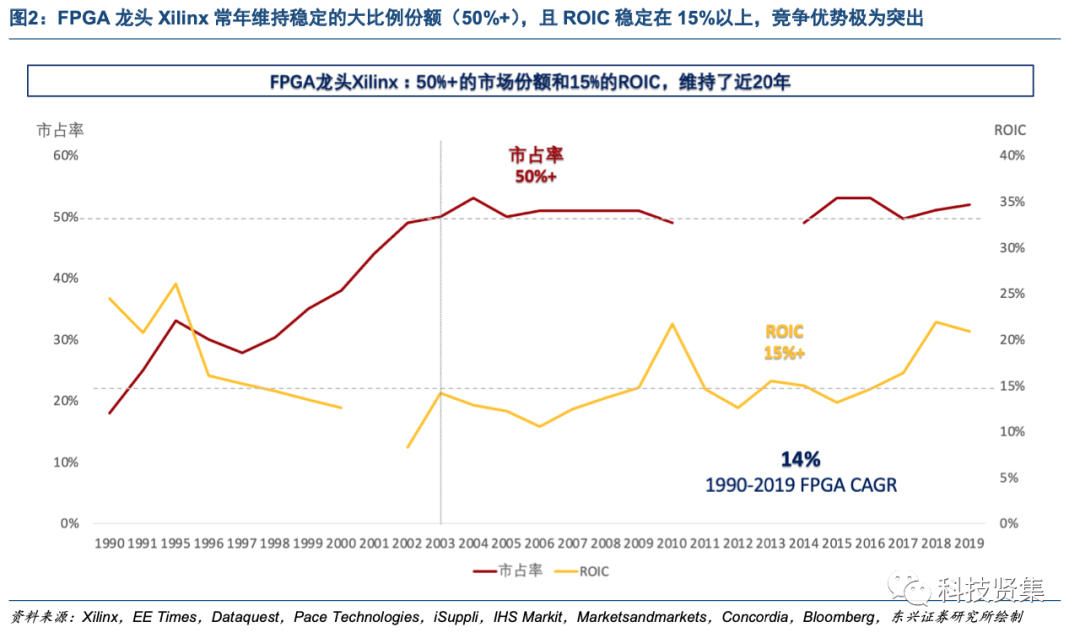

FPGA是一个高度集中的市场,龙头赛灵思占据过半份额,前4名玩家合计份额90%+。凭借高进入壁垒,清晰且确定的竞争格局,美股FPGA厂商的估值在同类数字芯片公司中均位居前列。此外,龙头赛灵思在快速增长的市场,维持了近20年50%+的市场份额,以及较高的ROIC水平,足以说明其极强的竞争优势。 我们在系列报告一《FPGA给用户提供了什么价值?》中,阐述了FPGA的价值在于高灵活的特性和高并行的架构,我们亦提到了FPGA竞争的关键点在于:制程领先、产品定义、架构创新以及EDA工具的易用性。

在本篇系列报告四中,我们将阐述FPGA清晰的竞争格局背后的原因,通过对FPGA全球三大公司Xilinx、Altera和Lattice的发展历史进行了详尽的复盘,系统地回答这些问题:FPGA商业模式的本质是什么?FPGA厂商自身的价值在哪里?为什么龙头能有这么强的护城河? 我们认为,FPGA的商业模式的本质是,用高标准化的芯片覆盖长尾市场以产生经济性,龙头之所以能有强的垄断性份额,是因为其在一种客户锁定下的规模经济下运作,使得龙头可以在多轮迭代中不断积累自身优势,侵蚀其他玩家的份额,在这一过程中,落后的厂商不断被淘汰,而行业的进入壁垒在不断地提高。赛灵思成为龙头的原因在于:1)制程领导者;2)对客户的需求把握最好,优秀的竞争策略制定和执行能力;3)生态的培养效果最好。

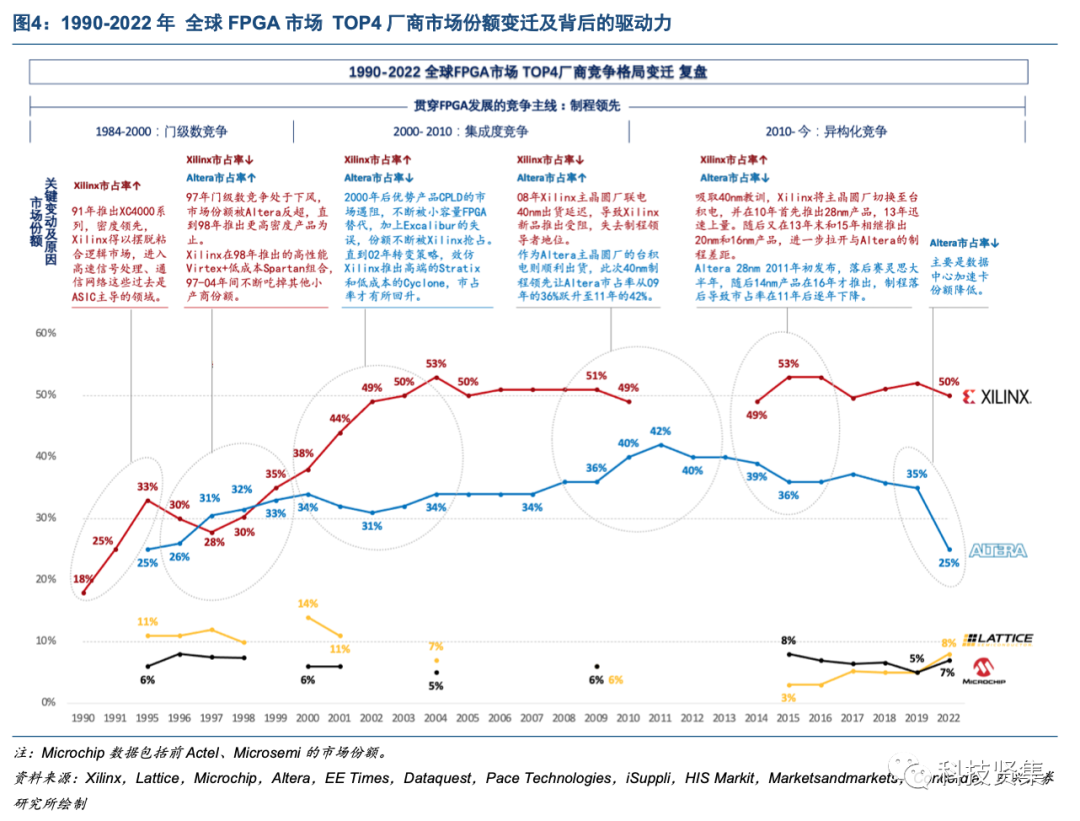

复盘1990-2022年FPGA竞争格局演变,我们发现了什么?制程竞争是贯穿FPGA整个发展历史的竞争主线,制程领先是FPGA市场份额最直接的决定因素。除此之外,在FPGA发展的不同阶段,有着不同的阶段竞争主线,实质是FPGA不同阶段的性能突破点:门级数竞争是FPGA厂商第一阶段的竞争主线(1984-2000),FPGA不断提升自身容量以获得替代ASIC的市场,门级数领先者往往获得大部分市场份额。集成度竞争是FPGA厂商第二阶段的竞争主线 (2000-2010),将板上分立的DSP等器件纳入到FPGA,背后是减少威廉希尔官方网站 面积、降低功耗和系统成本的需求,先推出高集成度FPGA的厂商获得了更多的替代DSP等竞争产品的份额。异构化竞争是FPGA目前的竞争主线 (2010-今),FPGA厂商竞相推出SoC FPGA,通过将板上的CPU等处理器嵌入到FPGA中,使得SoC既具备CPU的灵活性,又具备FPGA的高并行计算能力,进一步提升系统性能、减少板上面积和功耗,不断并获得来自嵌入式处理的市场。

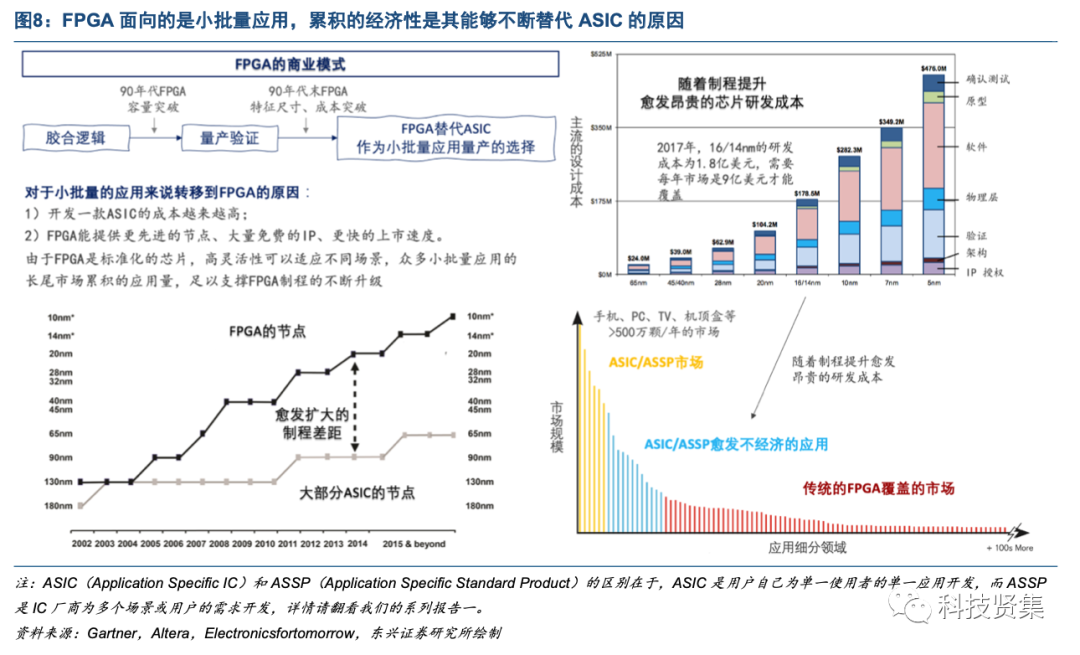

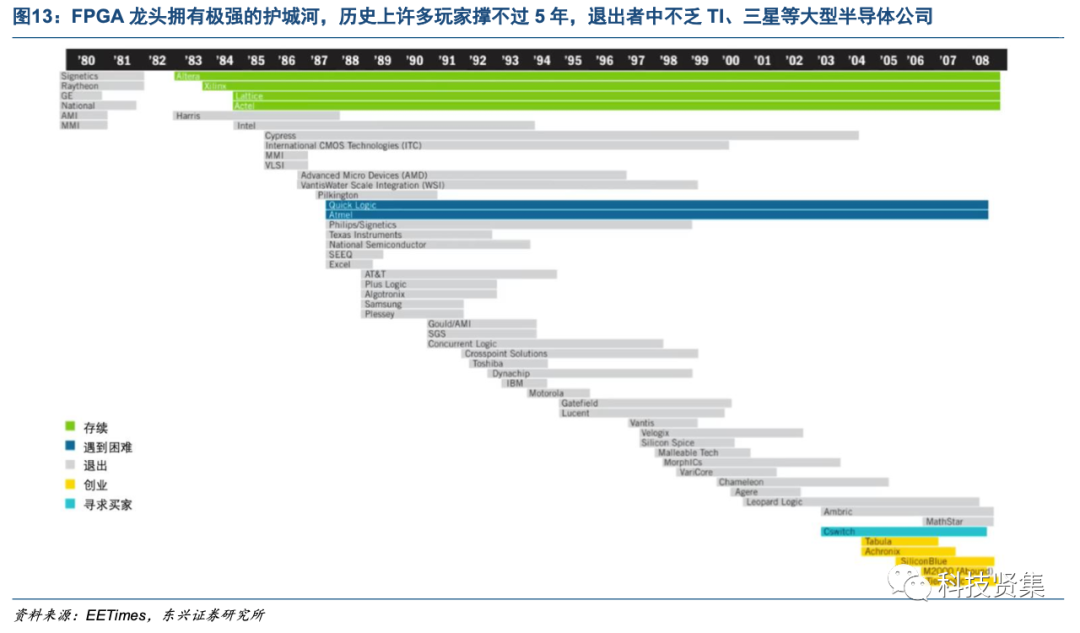

FPGA商业模式的本质?用高标准化的芯片覆盖长尾市场以产生经济性,这些小批量应用累积起来的出货量足以支撑FPGA的制程不断升级。FPGA是高度标准化的芯片,通过改变FPGA中LUT4里面的16位掩码,就能灵活地对应不同的组合威廉希尔官方网站 ,再结合寄存器,可以完成时序威廉希尔官方网站 的功能,从而实现任意威廉希尔官方网站 的“可编程”。随着芯片制程的提升,研发成本变得愈发昂贵,为小批量的应用开发一颗ASIC/ASSP变得越来越不经济,越来越多的客户转向使用FPGA。 为什么龙头能有这么强的护城河?因为其在一种客户锁定下的规模经济下运作,使得龙头可以在多轮迭代中不断积累自身优势,侵蚀其他玩家的份额,在这一过程中,落后的厂商不断被淘汰,而行业的进入壁垒在不断地提高。

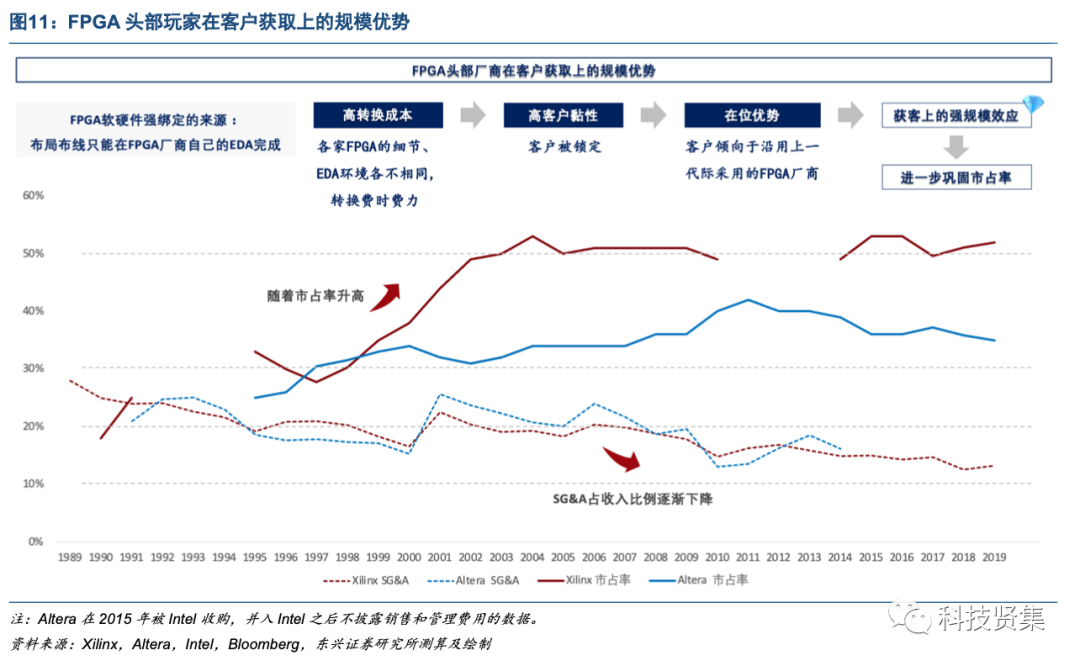

FPGA如何锁定客户?由于最关键的布局布线只能在FPGA厂商自己的EDA中进行,使得FPGA的软硬件形成极强的绑定。如无必要,客户通常不会更换FPGA厂商,而是根据自身的量产计划每年重复订购,展现非常强的客户粘性。同样地,为了减少转换成本,客户会倾向于沿用上一代FPGA的供应商,跨代际的客户黏性也非常强。

如何理解FPGA的规模经济?

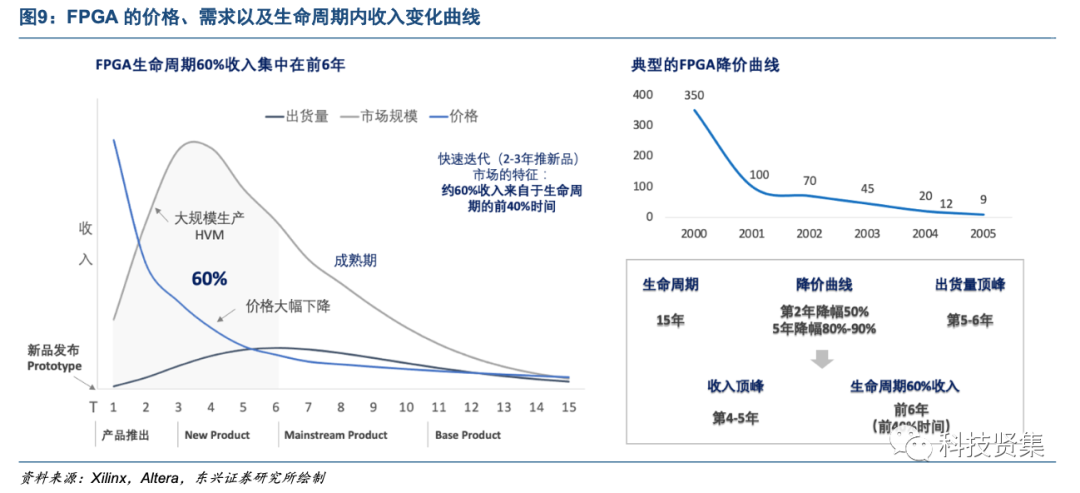

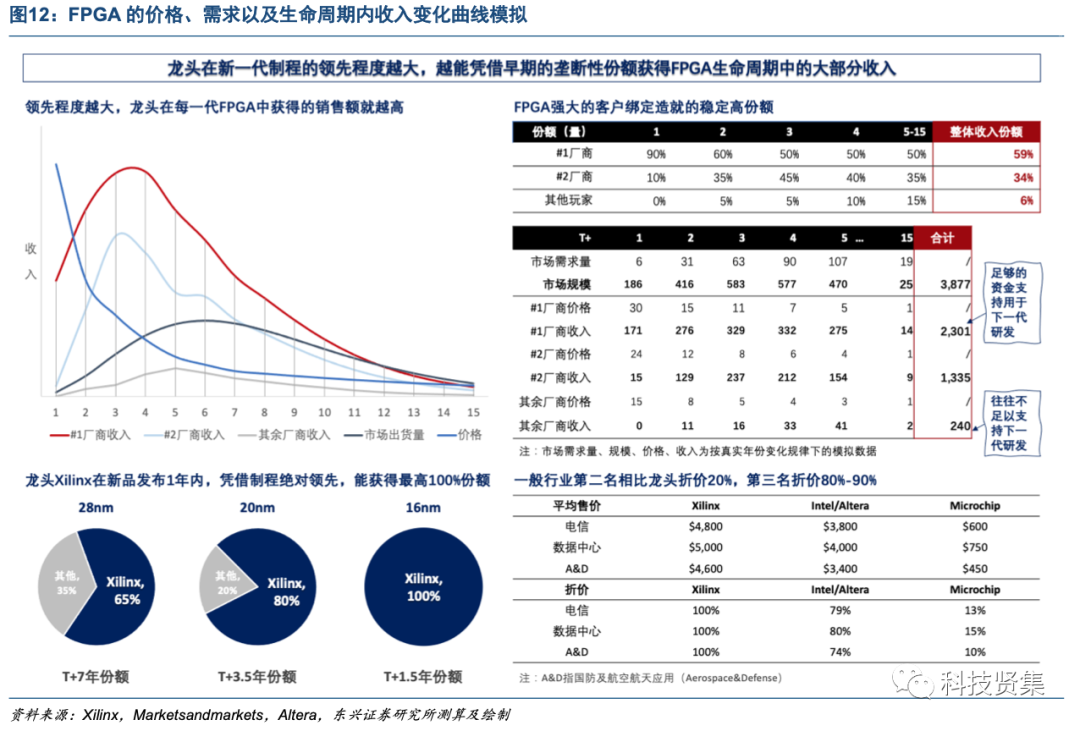

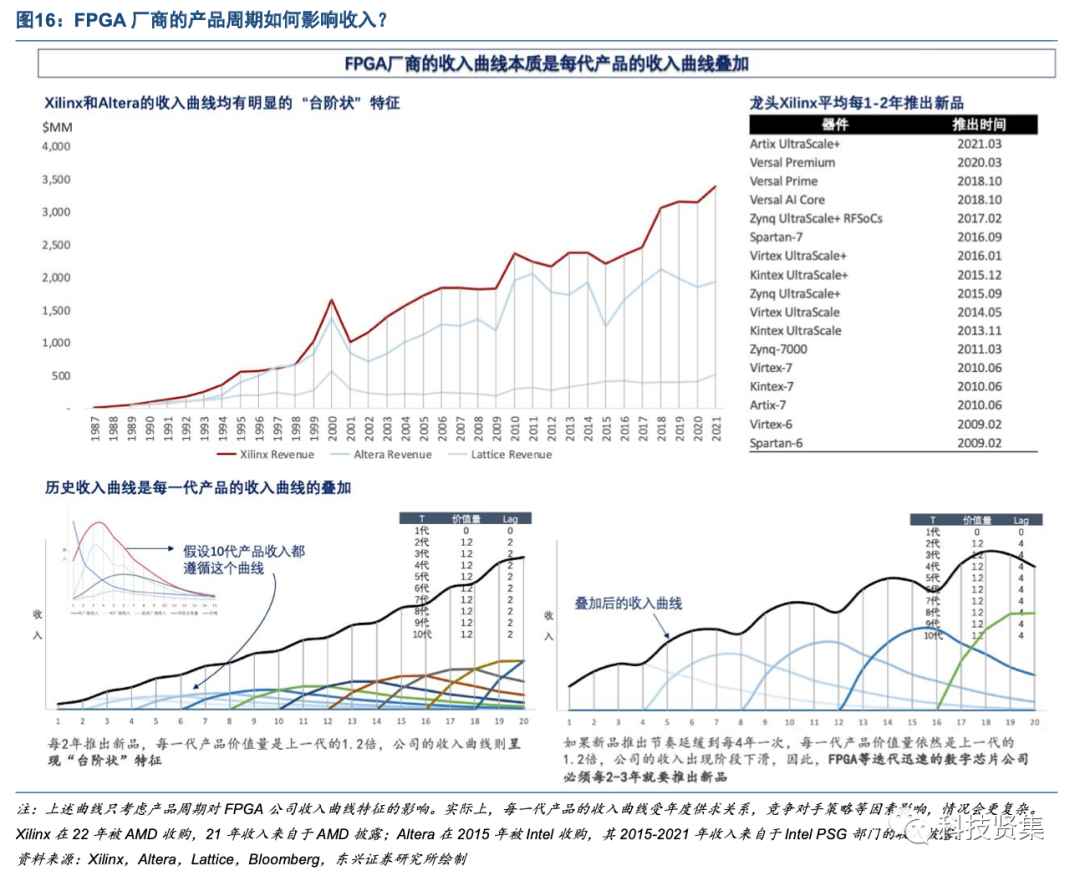

价格上,FPGA有着非常陡峭的降价曲线;需求上,出货量的顶峰一般在第5-6年达到,这使得FPGA生命周期中约60%的收入在前6年发生,后9年FPGA参与者通常面对的是量价齐跌的市场。由于量大的客户在前两年就会被领先的玩家锁定,如果不能做到前两年内推出新一代制程的产品,基本就会错失这一代产品市场收入最多的阶段。因此,对于FPGA厂商来说,竞争策略就是尽可能领先对手推出新一代的产品,在前2年完成尽量多的Design-wins,以获得更多被锁定的客户。在获得强劲的Design-wins之后,FPGA厂商凭借HVM(High-Volume Manufacture)阶段的大量订单迅速降低成本,并进一步开启激进的降价,以阻止落后的竞争者进入。由于FPGA的EDA和硬件强绑定的特性,客户转换成本极高,FPGA的头部厂商在获客成本上出现规模经济,高的在位优势进一步提升了行业的进入壁垒。在2-3轮制程迭代后,落后的厂商愈发无法获得足够的收入以投入到下一代产品的开发,选择退出,市场上其他玩家的比例会大幅减少,市场份额会向头部集中,清晰的格局使得FPGA头部厂商的毛利率均稳定维持在60%+的高水平区间。FPGA龙头在研发上同样具有规模经济。此外,FPGA厂商收入曲线的本质是每一代产品收入曲线的叠加,必须每2-3年推出新品,以避免产品周期造成的收入下滑。

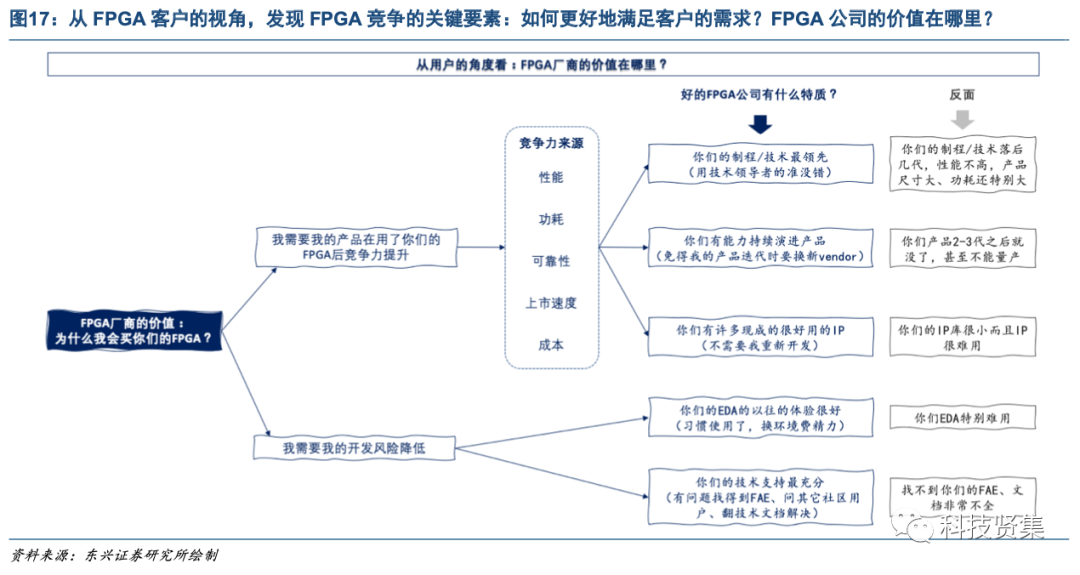

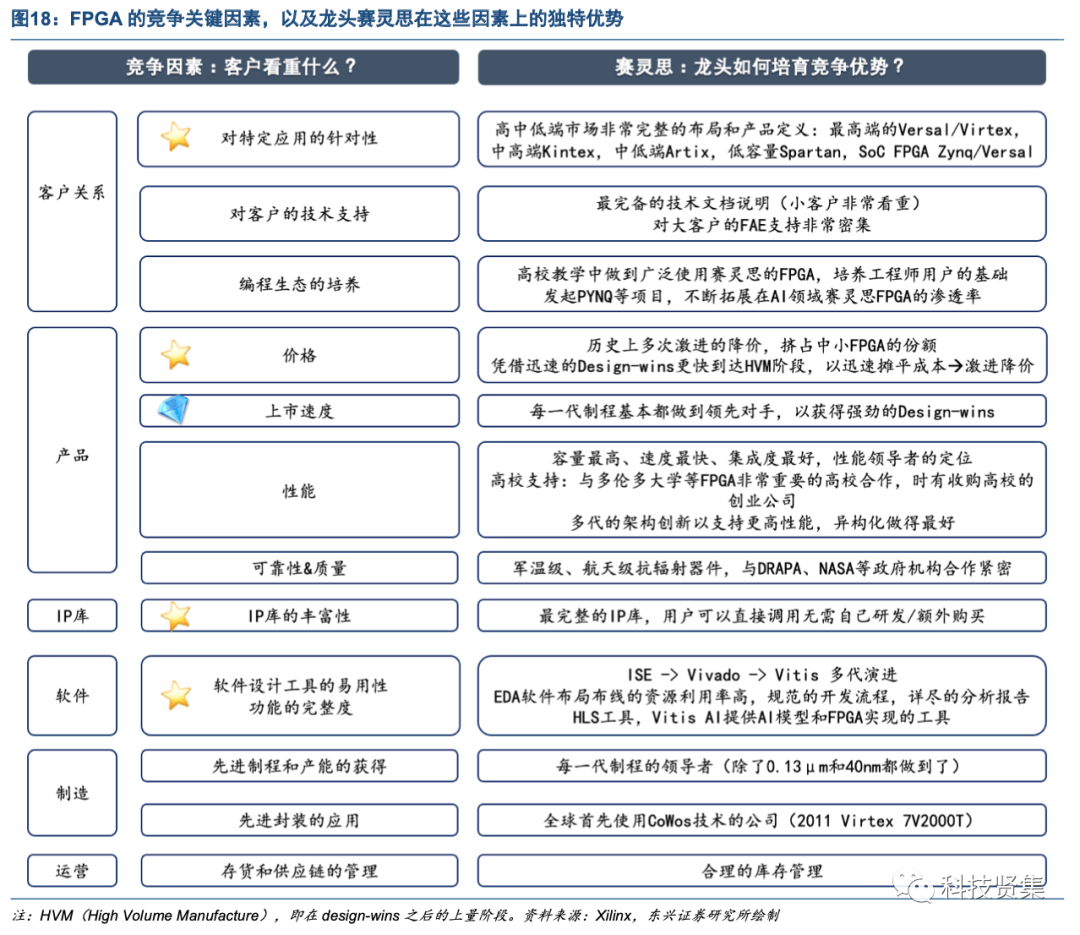

我们从FPGA的客户的视角分析,发现客户对FPGA主要有两大诉求:一是为自己的产品获得竞争力的提升,二是降低开发的风险。从客户的视角延伸到FPGA竞争的关键因素,我们总结为以下六点:客户关系、产品、IP库、软件、制造和运营能力。 我们认为,赛灵思成为龙头的原因在于:1)制程领导者。 2)对客户的需求把握最好,优秀的竞争策略制定和执行能力。 3)生态的培养效果最好。

风险提示:下游需求不及预期,中美贸易摩擦加剧。

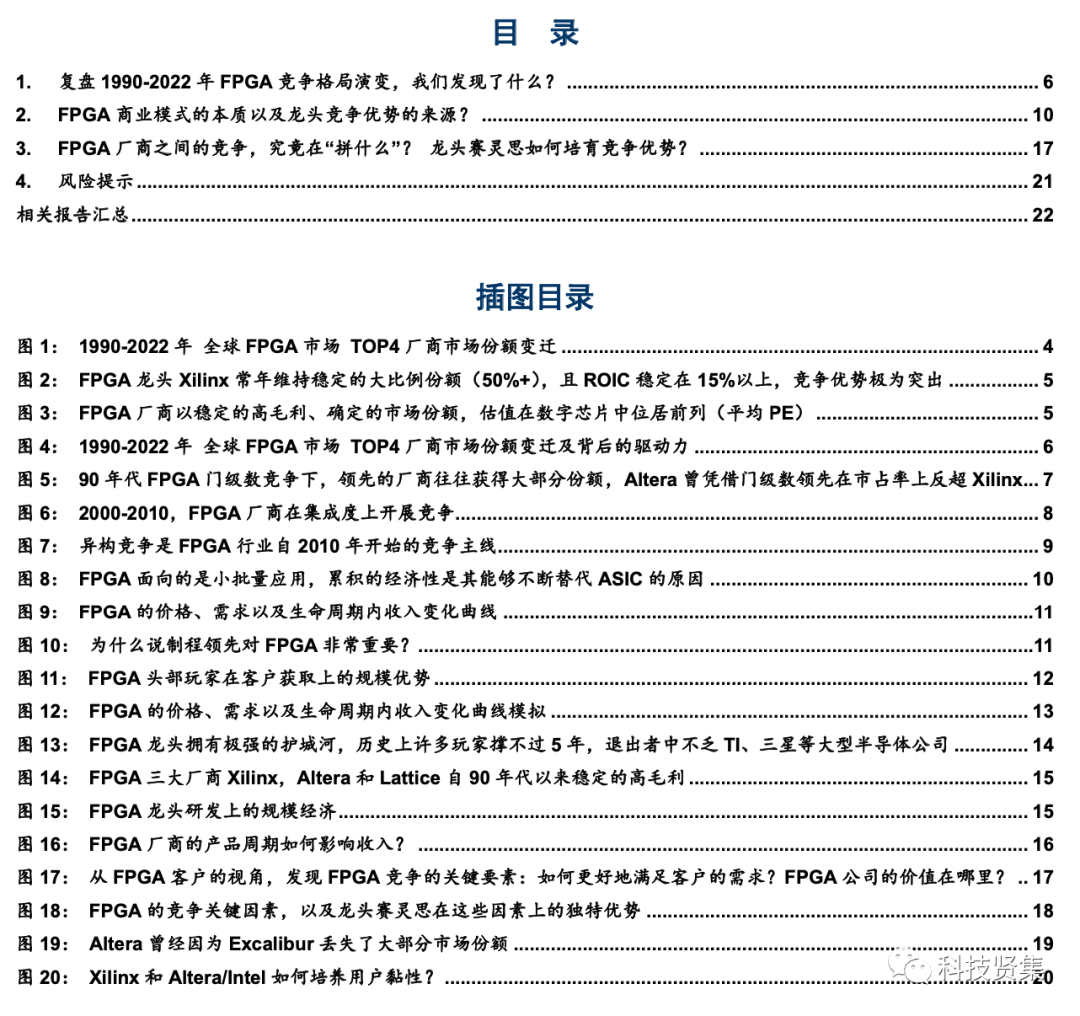

我们在系列报告一《FPGA给用户提供了什么价值?》阐述了FPGA的价值在于高灵活性及高并行超低时延的计算能力,我们亦提到了FPGA竞争的关键点在于:制程领先、产品定义、架构创新以及EDA工具的易用性。在本篇系列报告四中,我们将系统地回答这些问题:FPGA厂商自身的价值在哪里?FPGA厂商的竞争究竟在拼什么?龙头赛灵思是如何培育竞争优势的? FPGA是一个高度集中的市场,龙头赛灵思占据过半份额,前4名玩家合计份额90%+。根据Marketsandmarkets数据及我们估算,2022年,FPGA龙头赛灵思全球市场占有率为50%,与第二名英特尔(收购Altera)的25%拉开了明显差距,而作为行业第三、第四名的Lattice和Microchip(收购Microsemi)市场份额接近,均不超过10%。行业呈现高度集中态势,CR4超过90%,且均为美国公司。其中,龙头赛灵思在2003年市占率超过50%,在随后20年间,基本保持在50%以上。

龙头赛灵思维持了近20年的50%+的市场份额,以及较高的ROIC水平,足以说明其极强的竞争优势。赛灵思自1984年发明FPGA以来,市场份额从1990年的18%一路爬升到2003年的50%,并在随后20年间基本维持在50%上下,而在1990-2019近30年间,FPGA市场复合增长率为14%,一直保持着较高速度的增长。赛灵思在03年后的ROIC一直维持在15%上下的较高水平,并在2018-2019年爬升至20%+。在一个快速成长的行业中,龙头能在15%+的ROIC水平维持近20年的50%的市场份额,足以说明FPGA龙头有着非常强的竞争优势。

美股FPGA公司高估值的原因?高进入壁垒,清晰且确定的竞争格局。FPGA虽然是一个不大不小的市场(2022全球83亿美元),但凭借高进入壁垒,以及确定且清晰的竞争格局,使得美股FPGA厂商的估值在同类数字芯片公司中均位居前列。

01

复盘1990-2022年FPGA的

竞争格局演变,我们发现了什么?

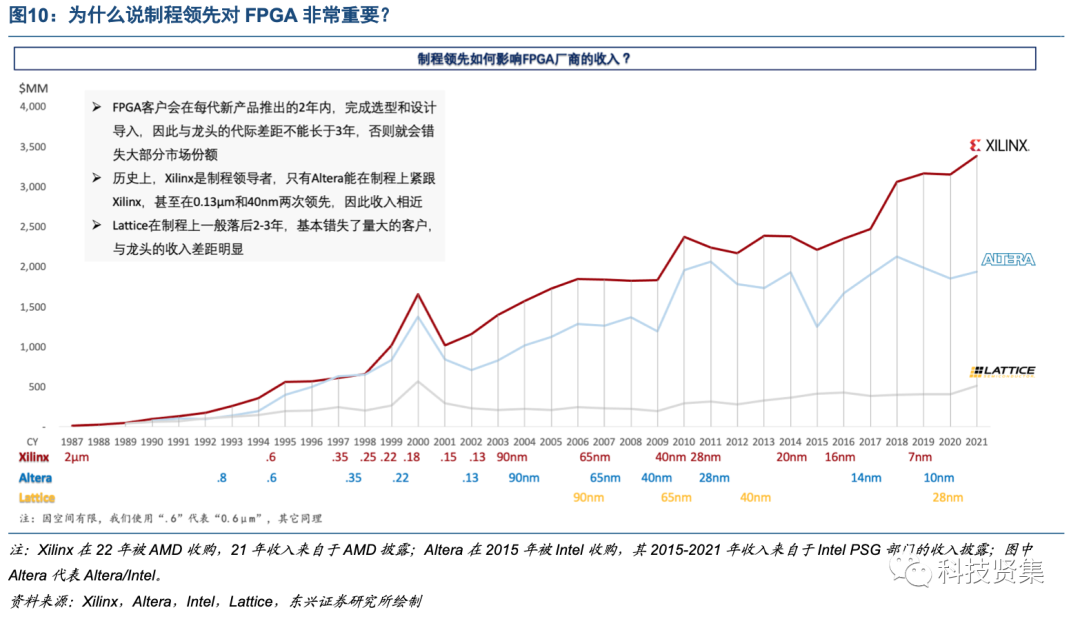

制程竞争是贯穿FPGA发展历史的竞争主线,制程领先是FPGA市场份额最直接的决定因素。FPGA的通用性使其走线和面积比起ASIC来说不是最优。因此,FPGA必须在制程上做到领先ASIC或者ASSP数代,以带来更有竞争力的性能表现,这使得FPGA对制程的追逐是必然的选择。此外,FPGA从新品发布到量产阶段中间存在客户导入环节,在这期间客户评估不同厂商新推出的FPGA,最后确定一家在后续量产的产品中使用,并在上面完成自己的威廉希尔官方网站 设计,即一个Design-win,这一过程通常需要9-12个月。由于开发环境、产品架构等各不相同,一旦确定了之后,用户转移到另一家FPGA是非常困难和费时的。这种高绑定的特点,造就了FPGA非常强的壁垒,使得最先推出的玩家往往能赢得大部分市场份额。一般来说,在最新制程的design-wins能预测2-3年后在FPGA市场的份额,而且能在下一轮制程竞争中享有一定的在位优势,因为客户通常不会轻易更换供应商。FPGA龙头赛灵思历史上是制程领导者,市场份额从2003年后便维持在50%的水平,除了Altera能跟上赛灵思的节奏,行业其他玩家均落后龙头2-3个代际。

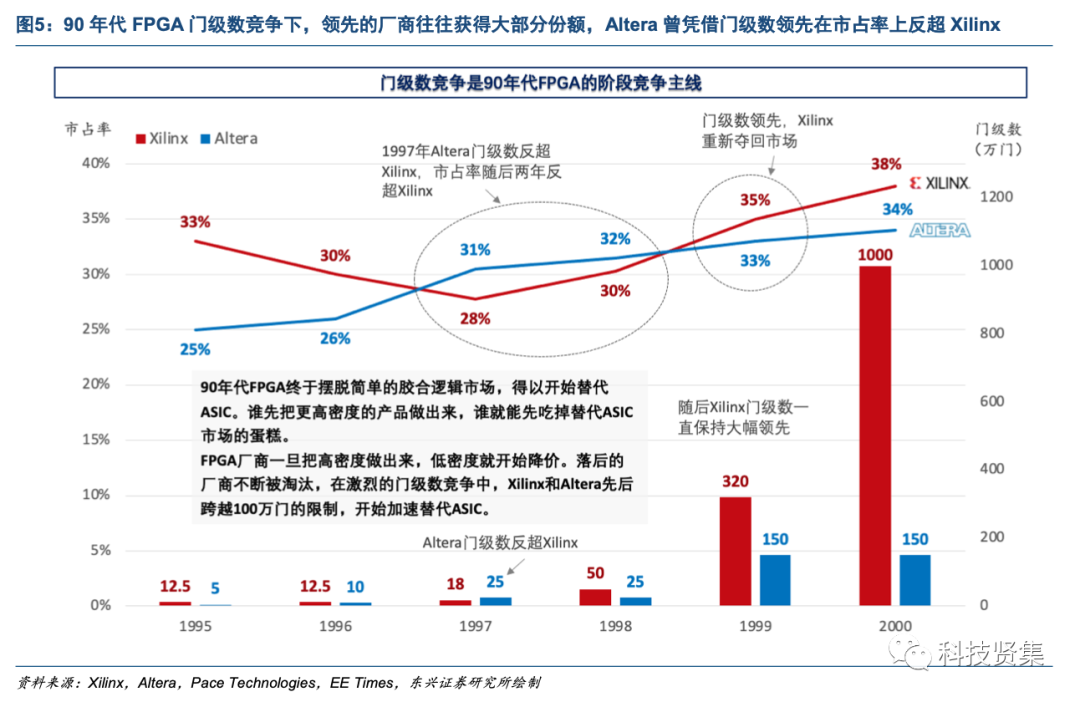

除了贯穿整个历史的制程竞争外,在FPGA发展的不同阶段,有着不同的阶段竞争主线,实质是FPGA不同阶段的性能和技术突破点: 门级数竞争是FPGA厂商第一阶段的竞争主线(1984-2000)。替代ASIC的背后是性能提升的需求,门级数领先者往往获得大部分市场份额。90年代,复杂的电子系统要求百万门级的规模,大多使用标准单元和门阵列实现。90年代初,FPGA的容量只有20-50万门,尽管脱离了胶合逻辑的市场,但仍无法进入更高端的ASIC市场。鉴于此,在整个90年代,FPGA厂商纷纷在门级数上展开竞争,谁先把更高密度的产品做出来,谁就能先吃掉替代ASIC市场的蛋糕。通过LUT输入数量、簇结构、互联形式等的架构改善,辅之以摩尔定律的推动,FPGA的密度和速度得以飞速提升。FPGA厂商一旦把更高密度的产品做出来,低密度就开始大幅降价,落后的厂商不断被淘汰。在激烈的门级数竞争中,Xilinx和Altera先后在1998-1999年跨越100万门的限制,开始加速替代门阵列、标准单元和ASIC,市占率得到持续的提升。

此阶段,FPGA竞争者之间开展激烈的专利战,以捍卫自身在高密度架构和EDA上竞争优势。例如,Altera作为CPLD的发明者,1992年通过推出FLEX进入FPGA市场,Xilinx在1993年便开始与Altera开展了长达8年的专利战,双方互诉对方产品侵权,并不断将对方包括CPLD在内的新品加入侵权列表,最后在01年以近似和解结束——Altera向Xilinx 支付了2000万美元,并互相进行专利交叉互换,承诺5年内不向对方提起专利诉讼。1999年,Altera还与Clear Logic开展诉讼,指控对方利用Altera的EDA软件为客户进行pin-to-pin的FPGA到ASIC的转换,最后使得Clear Logic在2002年退出市场。

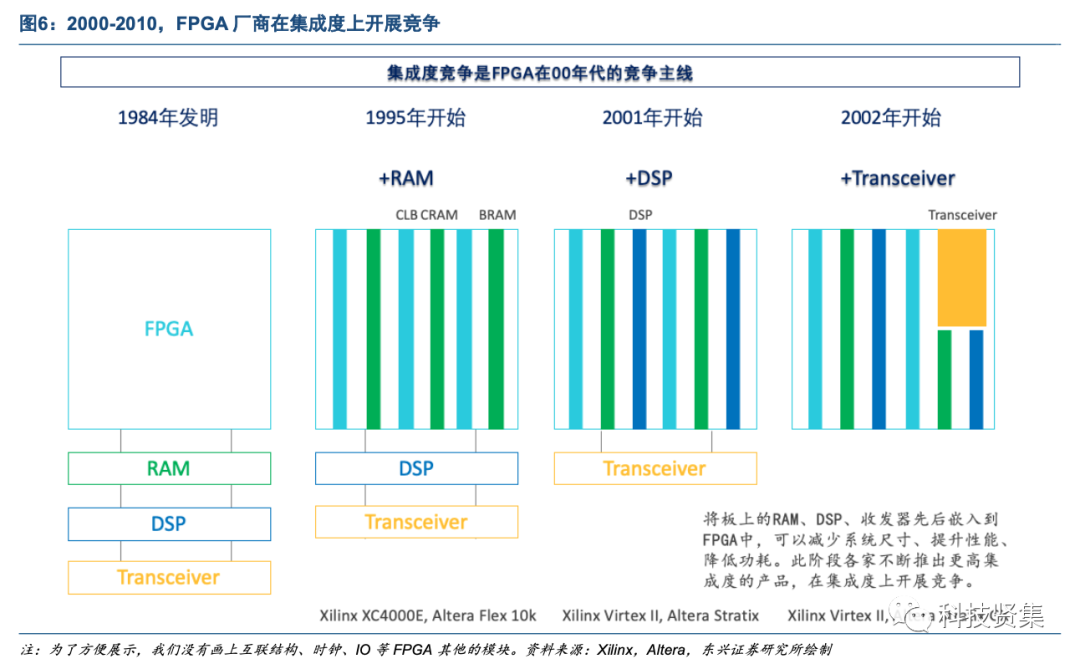

集成度竞争是FPGA厂商第二阶段的竞争主线(2000-2010)。将板上分立的DSP等器件纳入到FPGA,背后是减少威廉希尔官方网站 面积、降低功耗和系统成本的需求,先推出高集成度FPGA的厂商获得了更多的替代DSP等竞争产品的份额。90年代中期,FPGA厂商发现用户在使用FPGA时,会频繁将LUT作为存储使用(即“软”实现),占用了许多逻辑单元,导致FPGA容量出现不够的情况。因此,RAM是第一个被固化到FPGA中的单元。将这些用户频繁使用到的功能固化到FPGA中,可以极大地提升计算效率,用户也不需要为浪费宝贵的逻辑资源而烦恼,而且可以减少板上的走线、管脚和焊盘,进而减少PCB板的面积和功耗。例如,将DSP嵌入到FPGA中(而不是通过万能的LUT+寄存器实现),可以节省80%的功耗和分立的DSP在板上占用的面积。因此,在90年代末完成门级数的超越后,FPGA厂商的竞争主线从门级数转向集成度竞争,先后将原本属于板上的RAM、DSP、收发器等单元嵌入到FPGA中,以降低客户的功耗和总系统成本,并进一步蚕食板上其它分立器件的市场。Altera的FLEX 10K是第一个嵌入了RAM 的FPGA,Xilinx在00年通过收购Rocketchip拥有了高速收发器能力,并在02年3月发布的Virtex II Pro中嵌入了收发器。

然而,并不是一个FPGA上集成了越多固化单元就越好,除了最高端的客户,许多客户往往只需要特定方向上的固化单元集成。因此,FPGA厂商开始将产品线分化,Xilinx推出了高端的Virtex和低成本的Spartan两条线,Virtex针对复杂的通信设备市场,Spartan和CPLD Coolrunner针对消费电子市场。其中,Virtex还区分了多个产品系列,比如Virtex 4中,LX是最高端的FPGA,针对大型的高密度通信应用,而SX系列上嵌入了丰富的DSP资源,用于替代分立的DSP器件,FX加入了高速串行连接。Altera也在02年推出了高端的Stratix和低成本的Cyclone,Stratix还分化了一个包含高速收发器的Stratix GX系列。可见,集成度竞争的背后是产品定义的竞争,反映了FPGA厂商和客户沟通和需求把握能力。

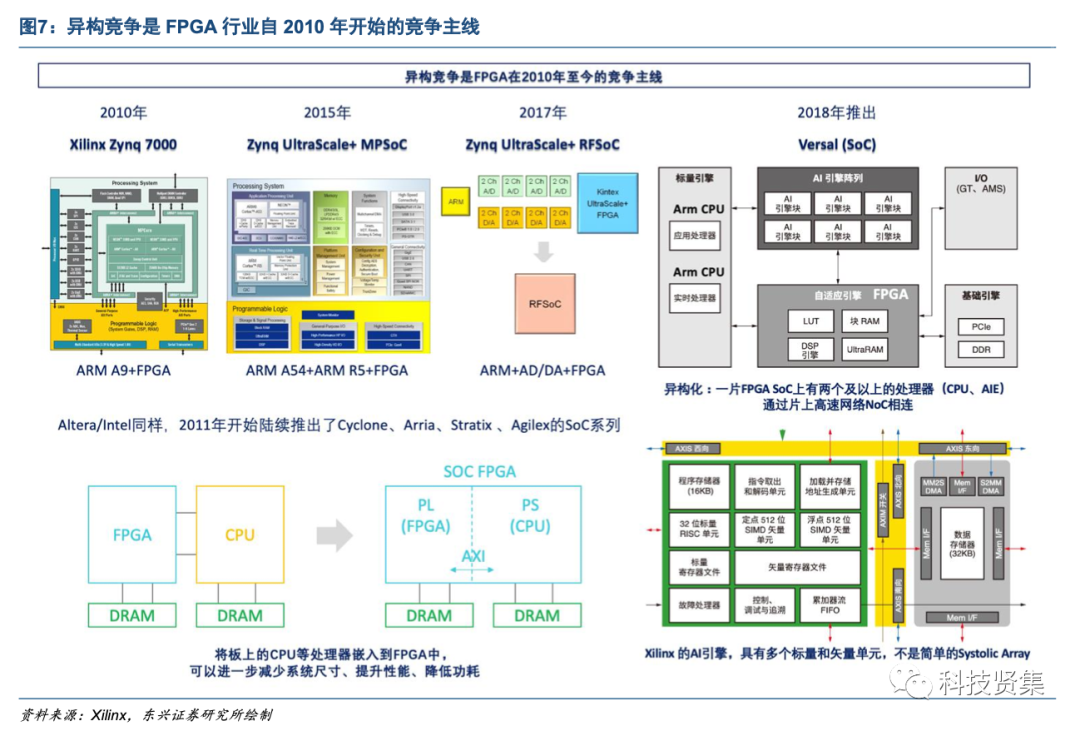

异构化竞争是FPGA厂商目前的竞争主线 (2010-今)。FPGA厂商竞相推出SoC FPGA,通过将板上的CPU等处理器嵌入到FPGA中,不断获得来自嵌入式处理的市场。因为走线从PCB转移到片内,处理时延更短,因此整体性能更高,并进一步减少板上的面积、降低功耗,使得SoC既具备CPU的灵活性,又具备FPGA的高并行计算能力。例如,Xilinx的RFSoC嵌入了ARM+4片ADC+4片DAC+1片Kintex UltraScale+ FPGA,相比分立的方案面积减少了50%,功耗降低30%-40%,成本降低40%-60%,时延比JESD204降低80%-90%。 自从2010年Xilinx推出Zynq 7000开始,FPGA进入了异构竞争的时代,进一步抢占原来使用分立的FPGA+CPU方案的市场。在Xilinx的Zynq系列中,PL(FPGA)与PS(ARM CPU)之间通过AXI总线通信。Xilinx在后续推出了针对高清视频处理的Zynq MPSoC,以及针对无线通信的RFSoC。目前Xilinx的Zynq系列SoC FPGA在工业、多媒体处理、通信、医疗有非常广泛的采用,最新的系列是在18年开始陆续推出的7nm ACAP Versal家族,在FPGA基础上嵌入了CPU和Xilinx的AI引擎,单元之间通过高速NoC相连。Altera/Intel同样,自2011年开始陆续推出了Cyclone、Arria、Stratix和Agilex的SoC FPGA,覆盖低成本、性价比和高端场景。

02

FPGA商业模式的本质

以及龙头竞争优势的来源?

在这里我们将深入为大家解答:FPGA商业模式的本质是什么?为什么龙头能有这么强的护城河?我们认为,FPGA的商业模式的本质是,用高标准化的芯片覆盖长尾市场以产生经济性;龙头之所以能有强的垄断性份额,是因为其在一种客户锁定下的规模经济下运作,使得龙头可以在多轮迭代中不断积累自身优势,侵蚀其他玩家的份额,在这一过程中,落后的厂商不断被淘汰,而行业的进入壁垒在不断地提高。 FPGA商业模式的本质是用高标准化的芯片覆盖长尾市场,以产生经济性,这些小批量应用累积起来的出货量足以支撑FPGA的制程不断升级。正如我们系列报告一提到的,FPGA是高度标准化的芯片,通过改变FPGA中LUT4里面的16位掩码,就能灵活地对应不同的组合威廉希尔官方网站 ,再结合寄存器,可以完成时序威廉希尔官方网站 的功能,从而实现任意威廉希尔官方网站 的“可编程”。这一硬件可编程的特性,使得同一片FPGA既可以在5G的基站中实现信道编码的功能,也可以在重新配置后放在数控机床中实现电机控制的功能。因此,FPGA又被称作“万能”芯片,可以用于实施任何威廉希尔官方网站 设计。而ASIC/ASSP面向的是特定方向的大批量应用,诸如手机、PC、TV、机顶盒等的每年在500万颗以上、甚至上亿颗出货量的市场。针对这些大批量的市场,专门开发一颗ASIC/ASSP足以摊平前期投入的研发成本。然而,随着芯片制程的提升,研发成本变得愈发昂贵,为小批量的应用开发一颗ASIC/ASSP变得越来越不经济,越来越多的客户转向使用FPGA。2017年,16/14nm的节点研发成本为1.8亿美元,往往需要每年9亿美元以上的市场才能覆盖这一成本;开发7nm节点需要3.5亿美元,研发成本和市场容量要求翻倍。而FPGA可以提供几乎是最先进的节点、大量FPGA厂商自研/合作伙伴的免费IP,立刻可用的芯片为用户的产品提供了更快的上市速度。随着越来越多ASIC方案的用户转为使用FPGA进行量产,FPGA市场开始快速成长,从1990年的1亿美元增长为2022年的83亿美元。

FPGA每一代产品一般从推出开始算起,大概在第4-5年达到收入的巅峰,近60%收入来自于前6年。从在售时间计算,一个FPGA的生命周期大概为10-15年,根据Altera的数据,销售收入的顶峰一般发生在FPGA新品推出后的第4-5年,这是由于FPGA有着非常陡峭的降价曲线。Xilinx一般在新品推出的第2年后,价格降幅就能达到50%,在第9年的价格相比刚推出时的价格降幅高达90%,而出货量的顶峰一般在第5-6年达到,这一价格和需求曲线的变化规律,使得FPGA生命周期中约60%的收入在前6年发生,后9年FPGA参与者面对的是量价齐跌的市场。因此,FPGA厂商的策略是尽可能参与到前6年的市场份额分配中。

实际上,前2-3年的制程领先对FPGA市场竞争格局非常重要。因为即使能在后9年获得高市场份额,FPGA厂商得到的收入也非常的少。事实上,量大的客户在前两年就会被领先的玩家锁定,后面新增的客户基本为新转移到更先进代际的客户。因此,如果不能做到前两年内推出新一代制程的产品,基本就会错失这一代产品市场收入最多的阶段。

FPGA如何锁定客户?由于最关键的布局布线只能在FPGA厂商自己的EDA进行,FPGA的软硬件形成了极强的绑定。高转换成本令客户非常容易被锁定,进而在整个生命周期形成稳定的需求量。FPGA厂商在发布新一代产品的原型开始,就会对客户进行送样测试,客户在数个FPGA供应商之间进行选择。一旦完成选型后,FPGA厂商就完成了一个“design-win”,这是因为客户需要在FPGA上完成自己的威廉希尔官方网站 设计,不会再更换FPGA供应商。正如我们系列报告一和前文中解释的,将威廉希尔官方网站 在FPGA上实现,最关键的环节是在布局布线。FPGA之所以能绑定客户,是因为FPGA的布局布线从来只能在对应的FPGA厂商自己的EDA中完成,使得软硬件形成了极强的绑定。并且,由于不同厂商FPGA的细节、EDA环境各不相同,转换到另一家FPGA厂商是非常困难的。对于越大型的设计,转换的难度更高,一般需要重新走一遍“综合-布局布线”的流程,并伴随着大量的调试工作,而这些新FPGA平台的适配工作通常可以耗费近半年时间。因此,如无必要,客户通常不会更换FPGA厂商,而是根据自身的量产计划每年重复订购,展现非常强的客户粘性。这使得头部玩家在获客上有非常明显的规模效应,稳定的客户进一步巩固了市占率。

高客户黏性使得FPGA头部玩家出现获客成本的规模经济,进一步提升了行业的进入壁垒。同样地,为了减少转换成本,客户会倾向于沿用上一代FPGA的供应商,即跨代际的客户黏性也非常强,这使得FPGA的头部厂商在获客成本上出现规模经济。随着Xilinx的市占率从1990年的19%上升到2003年的50%,其SG&A(销售和管理费用)占收入比例从接近30%下降至20%,在Xilinx巩固了市场地位后的20年间,又逐年下降至接近10%的水平。Altera同样,SG&A比例从90年代最高的25%下降至2014年的16%,充分说明了头部在获客上的规模优势。

因此,对于FPGA厂商来说,竞争策略就是尽可能领先对手推出新一代的产品,在前2年完成尽量多的Design-wins,以获得更多被锁定的客户。由于选型的一过程通常持续9-12个月,如果有厂商在新品发布上可以做到领先对手大半年以上的时间,那客户通常只能选择这家厂商的产品进行设计,并在1-2年后量产,领先厂商因此能在早期获得100%的份额。这也是为什么FPGA的制程领先往往能够预测2年之后的市场份额。例如,Xilinx在2015年9月发布16nm的UltraScale+新品,而竞争对手Altera在2016年10月才发布14nm的Stratix 10,落后Xilinx一年以上的时间,这使得2017年6月时,Xilinx在新一代产品的市场份额达到了100%。

在获得强劲的Design-wins之后,FPGA厂商凭借HVM(High-Volume Manufacture)阶段的大量订单迅速降低成本,并进一步开启激进的降价,以阻止落后竞争者的进入。在客户完成选型后,便开始自己的系统设计,完成最终的下游客户送样之后,就开始向FPGA厂商下大批量生产的订单,一般客户会在2年内完成选型到系统设计。一旦开启HVM阶段,FPGA厂商可以迅速摊平前期投入的包括NRE、软件研发等的固定成本,并开始激进地降价。例如,Xilinx新品推出后每年降价30%,两年累计降价50%。因此,制程落后2年以上的FPGA厂商,往往面临着非常强的进入壁垒。我们测算,即使在第5年开始每年获得市场上15%的需求量,在整个历史周期获得的累计收入也仅有整体市场的6%,往往不足以支撑下一代新品的研发。而龙头可以获得这一代FPGA在整个生命周期中59%的收入,足够用于下一代产品的研发。换句话说,落后厂商会愈发落后,龙头在新一代产品的竞争者会越来越少。

这也是为什么历史上许多玩家撑不过5年的原因,落后的厂商无法获得足够的收入投入到下一代产品的高昂的开发中,选择退出。在2-3轮迭代后,市场上其他玩家的比例会大幅减少,市场份额会向头部集中。

除了成本之外,龙头在产品定价上具有明显的溢价。行业龙头之外的玩家的产品普遍出现折价的情况。例如,行业第二名Intel/Altera的产品布局与Xilinx类似,其高、中、低产品线指标与Xilinx相近,但在电信、数据中心和A&D三个市场,平均售价均比Xilinx低20%以上。而行业第3-4名Microchip的产品集中在低价的中低容量领域,因此平均价格比Xilinx低80%-90%。

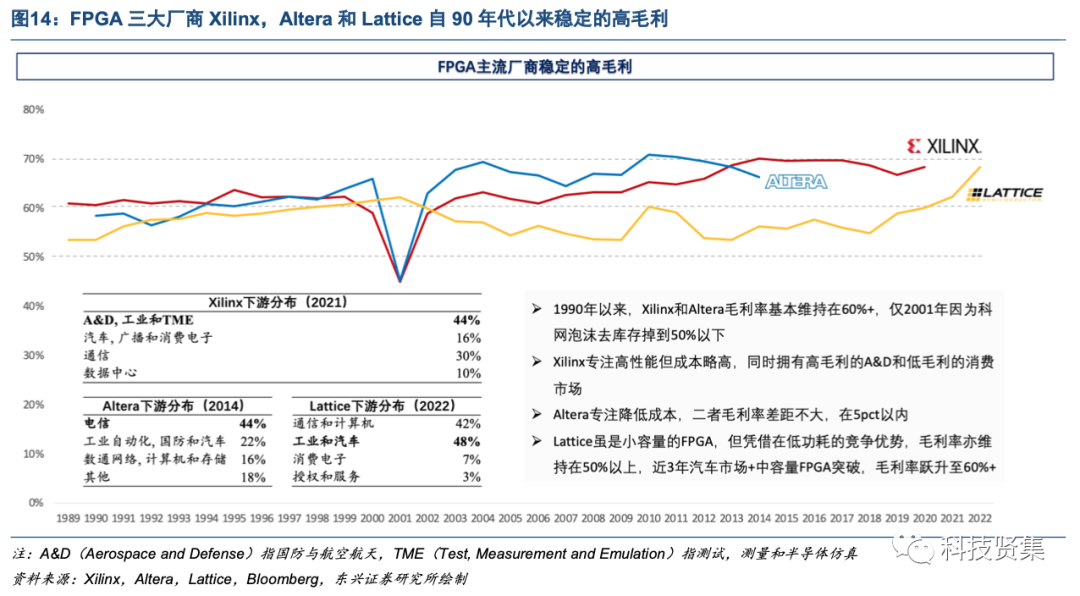

FPGA头部厂商毛利率均稳定维持在60%+的高水平区间。1990年以来,Xilinx和Altera的毛利率基本维持在60%以上,仅2001年因为科网泡沫去库存掉落至50%以下。其中,Xilinx专注高性能,但同时成本亦略高,下游来看,Xilinx同时拥有高毛利的A&D和低毛利的消费市场;而Altera下游集中在通信市场,来自A&D市场的收入占比较低,虽然价格低于Xilinx,但专注降低成本。综合考虑下来,二者毛利率差距不大,在5pct以内。Lattice虽然是中小容量的FPGA,但凭借在低功耗的竞争优势,毛利率也能维持在50%以上,近3年来更是凭借汽车市场的优势和中容量FPGA的突破,将毛利率提升至60%+。

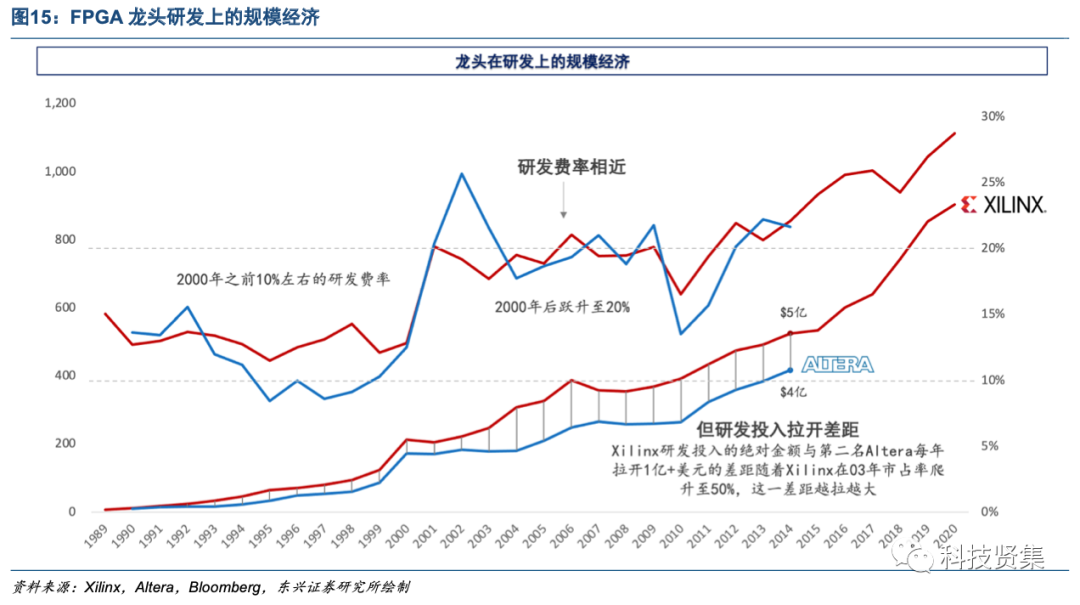

FPGA龙头在研发上同样具有规模经济。作为龙头,Xilinx可以在研发费率正常的情况下,绝对金额与第二名Altera每年拉开近1亿美元以上的差距,随着Xilinx在03年市占率爬升至50%,这一差距越拉越大。每年在研发上多出来的投入可以用于加强自身的竞争优势,比如更多的技术/架构创新、更完善的EDA开发、更快的研发进度等方面,而不必损失盈利能力。

FPGA厂商收入曲线的本质是每一代产品收入曲线的叠加,必须每2-3年推出新品,以避免产品周期造成的收入下滑。我们测算,如果FPGA公司每2年推出新品,每一代产品价值量是上一代的1.2倍,公司的收入曲线将呈现“台阶状增长”的特征。如果新品推出节奏延缓到每4年一次,在每一代产品价值量依然是上一代的1.2倍,公司的收入会出现阶段性的下滑。因此,FPGA等迭代迅速的数字芯片公司,必须每2-3年就要推出更高价值量的新品,以避免收入出现“青黄不接”的情况,龙头Xilinx更是每1-2年就推出新品。除了产品周期外,FPGA厂商的收入曲线还叠加了当年的宏观经济、个别下游需求、库存水平等因素的影响。例如,1996-1997年、2000-2001年、2007-2009年、2012年、2015年、2018-2019年都有宏观经济下滑背景下半导体行业去库存的情况。

03

FPGA厂商之间的竞争,究竟在“拼什么”?

龙头赛灵思如何培育竞争优势?

我们从FPGA的客户的视角分析,发现客户对FPGA主要有两大诉求:一是为自己的产品获得竞争力的提升,二是降低开发的风险。一般来说,系统的竞争力来自于在性能、功耗、可靠性、上市速度和成本上的综合表现,FPGA的客户——工程师在设计其产品时往往是基于以上五个维度思考,并在产品设计上做出自己的权衡。通常来说,更先进代际的FPGA能提供更好的性能和功耗表现,能做到更小的芯片或者相同面积下更高的性能,使得自家产品更受消费者的青睐。因此,选择制程领导者是惯例。除此之外,在以上五个维度的表现最贴近自身情况,即产品定义最接近需求的FPGA,往往会获得青睐。

第二,工程师会优先选择能持续迭代的产品,需要FPGA公司做出产品演进的承诺,以避免发生自己产品迭代时需要更换FPGA厂商的情况。更重要是,由于从新品推出到量产往往需要9-12个月,工程师会优先选择那些有可靠量产历史的厂商,以避免出现FPGA厂商倒闭,导致的自己产品不能量产的风险。此外,FPGA厂商提供的各种软IP对于工程师来说是非常有吸引力的,从EDA的IP库中调用FPGA厂商的提供的IP,可以极大地节省他们的开发时间和难度,如果FPGA厂商提供的IP很少、或者可靠性不高,则是扣分项。

除了产品竞争力以外,工程师的另一大诉求是降低开发风险,他们在选择某一个厂商的FPGA时,往往是由于过去在这家厂商的开发体验很好,而换开发环境是每一个工程师竭力避免的。由于各家FPGA和EDA细节各不相同,在一家FPGA厂商能跑通的设计,直接不加调试转移到另一家FPGA厂商能跑通的可能性非常低,其中的工作量往往具有高度的不确定性。因此,为了降低开发的成本和风险,如无必要,工程师往往不愿意切换到新的FPGA厂商。此外,FPGA厂商的技术支持也是非常重要的考虑,在FPGA的开发中的时常会遇到各种问题,对于大客户来说往往有充分的FAE对接支持,但是FPGA更多的是中小客户群体,此时FPGA如果有充分的技术文档、或者有完备的开发社区,就能减少大部分开发遇到的问题。 从客户的视角延伸到FPGA竞争的关键因素,我们总结为以下六点:客户关系、产品、IP库、软件、制造和运营能力,并在图中逐一回答了赛灵思在这六个因素中如何做到独一无二,即赛灵思是如何培育自己的竞争优势的。 我们认为,赛灵思成为龙头的原因在于:1)制程领导者。正如我们前文分析,制程是FPGA市场份额的最直接竞争因素。除了0.13μm和40nm之外,赛灵思一直是行业内制程领导者的角色,能持续开启“技术领先-订单-成本优势-客户黏性-下一代研发投入”的正向循环;

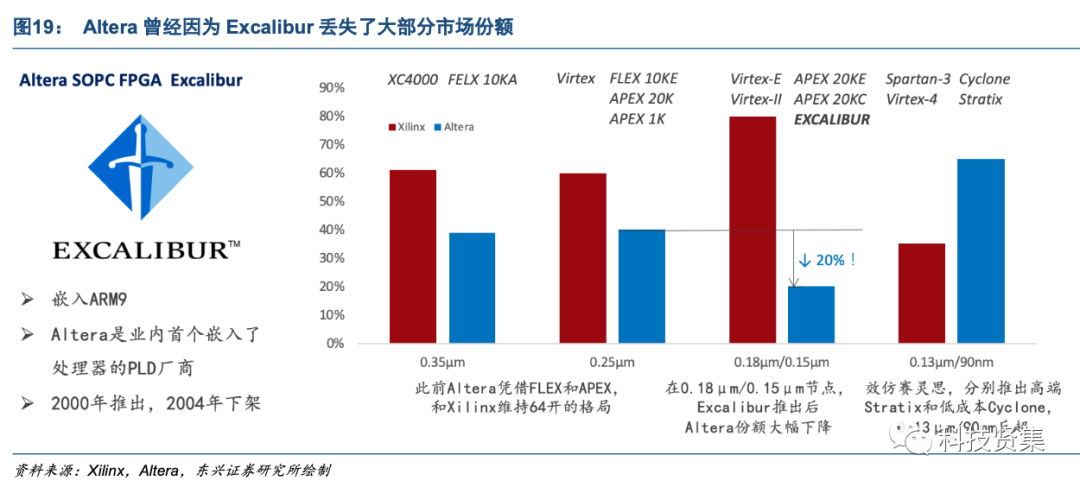

2)对客户的需求把握最好,优秀的竞争策略制定和执行能力。在FPGA中嵌入固化单元,往往比使用LUT、寄存器等万能资源来说,拥有更低的功耗和面积。尽管如此,要嵌入哪些固化单元需要设计者权衡,因为FPGA的开发者购买的是整个芯片,他们仍有可能为自己不需要或者不使用的功能付费;另一方面,如果FPGA的固化功能太少,其在市场上的竞争力就大为降低,因为客户不得不使用太多的宝贵的可编程逻辑资源,去实现本来应该固化的功能,功耗和时延均大幅增加。这都需要FPGA公司有非常好的客户的沟通。因此,早在1998年,赛灵思就区分了高端和低容量的市场,针对低容量市场推出了低成本的Spartan,面向那些需要FPGA的灵活性和高并行性,但又不需要通信市场一样需要收发器等高性能的硬核的场景。而00年Altera专注于推出最高性能的Excalibur,并没有重视低容量市场,直到Excalibur失败后,2002年Altera才效仿赛灵思推出高端的Stratix和低成本的Cyclone。除了产品,赛灵思在98年第一个在Virtex上实现了FPGA的远程升级功能,只需要简单地将编程文件发送到联网的设备中,就可以使其符合不断变化的通信标准,不需要工程师走到基站一个个升级软件,而这一点是当时很多ASIC所没办法做到的。这一远程重配置功能的加入为客户节省了大量的时间和金钱的成本,使得Virtex在通信市场大受欢迎,推动Xilinx的市场份额从98年的30%提升至03年的50%。 Altera历史上在Excalibur的失败,说明了产品定义和需求匹配的重要性。在FPGA上嵌入处理器硬核,早在2000年就有过尝试。在0.18/0.15μm节点中,Altera为了和赛灵思在性能上竞争,将ARM9嵌入到了其最新的SOPC FPGA Excalibur中,成为业内首个将处理器嵌入到FPGA的厂商。然而,刚刚经历科网泡沫的客户将功耗提升到了和性能同等重要的位置,不愿意为过高性能的FPGA付费,对FPGA需求仍然在灵活性上,使得Altera在0.18/0.15μm的FPGA市场份额陡降至仅有20%,而此前赛灵思和Altera一直都维持在6-4分成的局面。Altera之后吸取了教训,在嵌入固化单元时进行了非常小心的考虑,不再一味强调产品的性能,而是强调了解客户需求,并在2002年推出了针对高端市场的Stratix和中低容量的Cyclone,在0.13μm/90nm市占率反超赛灵思。然而, Xilinx在FPGA全市场的市占率已经和Altera拉开了明显差距。1999年,Xilinx和Altera市占率分别为35%和33%,相当接近;在2000-2002年,Xilinx凭借高性能的Virtex在业内树立了技术领导者的地位,以及低成本的Spartan迅速扩大客户群和出货量,市占率迅速爬升,在2002年达到了49%,而Altera市占率降低到了31%,基本错失了最佳的追赶期。

3)生态的培养效果最好。赛灵思有着所有FPGA厂商中最完备的文档说明,这一点对于中小客户来说非常有吸引力,因为他们通常没有大客户拥有的FAE支持。在用户群体培养中,在高校中FPGA教学中几乎都会以赛灵思为例,工程师的基础最好。在IP库中,赛灵思拥有最完整的IP库,910个IP中,近60%是自研IP,用户可以直接调用,不需要自己重新研发,而Altera约为278个,选择范围远小于Xilinx。除此之外,Xilinx在多个维度上有非常强的综合表现,包括EDA的迭代速度、易用性等。

审核编辑:黄飞

-

风门执行器在汽车暖通空调系统中有什么驱动因素?2019-07-30 0

-

什么因素推动射频半导体格局的变化?2019-09-02 0

-

哪些因素推动着市场格局不断变化2021-01-15 0

-

FPGA | 竞争冒险和毛刺问题2023-11-02 0

-

快速成熟的智能照明市场有哪些驱动因素2018-12-25 1501

-

战略性新兴产业集群形成驱动因素及模式2021-04-06 3178

-

DC-DC转换器哪些驱动因素会影响电源设计的趋势2022-04-12 1401

-

影响可穿戴诊断设备发展的市场驱动因素2022-10-25 642

-

了解风门执行器以及在它们在汽车暖通空调系统中的驱动因素2022-11-01 439

-

了解风门执行器以及汽车HVAC系统中它们的驱动因素2022-11-01 444

-

电子灯镇流器IGBT门驱动因素2023-07-24 255

-

刚性威廉希尔官方网站 板的9个成本驱动因素2023-10-15 602

-

如何从生产制造环节减少电机振动因素?2023-11-06 707

-

异质芯片组装主流化的驱动因素和方法2023-12-08 670

全部0条评论

快来发表一下你的评论吧 !