FPGA设计的IP和算法应用综述

描述

FPGA设计的IP和算法应用

基于IP的设计已成为目前FPGA设计的主流方法之一,本章首先给出IP的定义,然后以FFT IP核为例,介绍赛灵思IP核的应用。

IP核综述

IP(Intelligent Property) 核是具有知识产权核的集成威廉希尔官方网站 芯核总称,是经过反复验证过的、具有特定功能的宏模块,与芯片制造工艺无关,可以移植到不同的半导体工艺中。到了SOC 阶段,IP核设计已成为ASIC威廉希尔官方网站 设计公司和FPGA提供商的重要任务,也是其实力体现。对于FPGA 开发软件,其提供的IP核越丰富,用户的设计就越方便,其市场占用率就越高。目前,IP核已经变成系统设计的基本单元,并作为独立设计成果被交换、转让和销售。

从IP核的提供方式上,通常将其分为软核、硬核和固核这3类。从完成IP核所花费的成本来讲,硬核代价最大;从使用灵活性来讲,软核的可复用使用性最高。( 这部分内容前面已经阐述,这里再重申一下)

软核(Soft IP Core)

软核在EDA设计领域指的是综合之前的寄存器传输级(RTL) 模型;具体在FPGA设计中指的是对威廉希尔官方网站 的硬件语言描述,包括逻辑描述、网表和帮助文档等。软核只经过功能仿真,需要经过综合以及布局布线才能使用。其优点是灵活性高、可移植性强,允许用户自配置;缺点是对模块的预测性较低,在后续设计中存在发生错误的可能性,有一定的设计风险。软核是IP 核应用最广泛的形式。

固核(Firm IP Core)

固核在EDA设计领域指的是带有平面规划信息的网表;具体在FPGA设计中可以看做带有布局规划的软核,通常以RTL 代码和对应具体工艺网表的混合形式提供。将RTL描述结合具体标准单元库进行综合优化设计,形成门级网表,再通过布局布线工具即可使用。和软核相比,固核的设计灵活性稍差,但在可靠性上有较大提高。目前,固核也是IP核的主流形式之一。

硬核(Hard IP Core)

硬核在EDA 设计领域指经过验证的设计版图;具体在FPGA 设计中指布局和工艺固定、经过前端和后端验证的设计,设计人员不能对其修改。不能修改的原因有两个:首先是系统设计对各个模块的时序要求很严格,不允许打乱已有的物理版图;其次是保护知识产权的要求,不允许设计人员对其有任何改动。IP 硬核的不许修改特点使其复用有一定的困难,因此只能用于某些特定应用,使用范围较窄。

IP Core生成器(Core Generator) 是Xilinx FPGA设计中的一个重要设计工具,提供了大量成熟的、高效的IP Core为用户所用,涵盖了汽车工业、基本单元、通信和网络、数字信号处理、FPGA特点和设计、数学函数、记忆和存储单元、标准总线接口等8 大类,从简单的基本设计模块到复杂的处理器一应俱全。配合赛灵思网站的IP中心使用,能够大幅度减轻设计人员的工作量,提高设计可靠性。

Core Generator最重要的配置文件的后缀是xco,既可以是输出文件又可以是输入文件,包含了当前工程的属性和IP Core的参数信息。

5.7.2 FFT IP核应用示例

ISE提供了FFT/IFFT的IP Core,可以完成实数、复数信号的FFT以及IFFT运算。FFT的IP Core提供三种结构,分别为:

(1) 流水线,Streaming I/O结构:允许连续的数据处理;

(2) 基4,Burst I/O结构:提供数据导入/导出阶段和处理阶段。此结构拥有较小的结构,但转换时间较长;

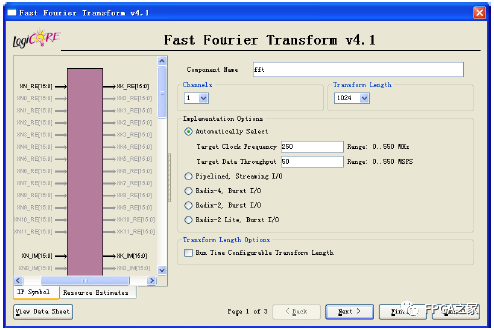

(3) 基2,Burst I/O结构:使用最少的逻辑资源,同Radix-4相同,提供两阶段的过程。其配置界面有3页,第一页如图5-57所示,主要用于配置实现结构;第二页配置数据位宽以及数据处理操作;第三页配置数据缓存空间。

图5-57 FFT IP core的用户界面

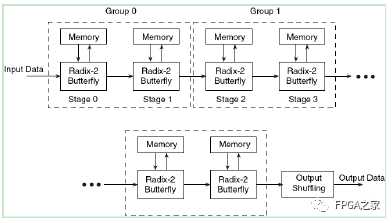

在实际硬件操作中,模块的执行速度是很重要的参数,所以本文分析第一种结构,即流水线Streaming I/O结构,以进行连续的数据处理。在进行当前帧的N点数据时,可加载下一帧的N点数据,同时输出前一帧的N点数据。此结构由多个基2的蝶形处理单元构成,每个单元都有自己的存储单元来存储输入和中间处理的数据,其结构如图5-58所示。

图5-58 FFT模块的流水线,Streaming I/O结构

FFT的计算单元具有丰富的控制信号,其详细说明见下文。

XN_RE、XN_IM :输入操作数,分别为实部和虚部,以2 的补码输入。在使用时应当确定其位宽。

START :FFT开始信号,高有效。当此信号变高时,开始输入数据,随后直接进行FFT 转换操作和数据输出。一个START脉冲,允许对一帧进行FFT 转换。如果每N 个时钟有一个START脉冲或者START始终为高,,则都可以连续进行FFT。如果在最初的START前,还没有NFFT_WE,FWD_INV_WE,SCALE_SCH_WE信号,则START变高后就使用这些信号的默认值。由于此IP Core支持非连续的数据流,因此在任何时间输入START,即可开始数据的加载。当加载N个数据结束后,就开始FFT转换运算。

UNLOAD :对于Burst I/O结构,此信号将开始输出处理的结果。对于流水线结构和比特逆序输出的情况,此端口不是必要的。

NFFT :此端口只对实时可配置应用时有用。

NFFT_WE :此端口是NFFT 端口的使能信号。

FWD_INV :用以指示IP Core为FFT还是IFFT,其等于1时IP Core进行FFT运算,否则进行IFFT 运算。至于采用哪种转换运算是可以逐帧变化的。这一端口给FFT的使用提供了很大的方便。

FWD_INV_WE :作为FWD_INV端口的使能信号。

SCALE_SCH:(1) 在IP Core设计时,如果选择在计算过程中进行中间数据的缩减,那么此信号才可起作用;(2) 输入的位宽等于2*ceil(NFFT/2),其中NFFT = log2(point size)。(3) 流水线结构中,将每个基2的蝶形处理单元视为一个阶段,每个阶段进行一次数据的缩减,缩减的比例以此输入中对应阶段的两比特表示。(4) 每阶段的两比特数可以是3,2,1或0 :它们表示了数据所需要移动的比特数。

SCALE_SCH_WE :作为SCALE_SCH的使能信号。

SCLR :可选端口。

Reset :重置信号端口。Reset=1时,所有工作都停止且初始化。但内部的帧缓存保留其内容。

CE :可选端口。

CLK :输入时钟。

XK_RE,XK_IM :输出数据总线,以2 的补码输出。SCALE_SCH_WE有效时,输出位宽等于输入;否则,输出位宽= 输入位宽+NFFT+1。

XN_INDEX :位宽等于log2(point size),输入数据的下标。

XK_INDEX :位宽等于log2(point size),输出数据的下标。

RFD :数据有效信号,高有效,在加载数据时为高电平。

BUSY :IP Core 工作状态的指示信号,在计算FFT 转换时为高电平。

DV :数据有效指示信号,当输出端口存在有效数据时变高。

EDONE :高有效。在DONE 信号变高的前一个时钟变为高电平。

DONE :高有效。在FFT 完成后变高,且只存在一个时钟。在DONE 变高后,IP Core开始输出计算结果。

BLK_EXP :当使用Burst I/O 结构时可用,若选择流水线,则此端口无效

OVFLO :算法溢出指示。在数据输出时,如每帧有溢出,此信号变高。在每帧开始处,此信号重置。

例5.7.1使用IP Core实例化一个16点、位宽为16位的FFT 模块。

IP Core 直接生成的乘法器的Verilog 模块接口为:

module fft16(sclr, fwd_inv_we, rfd, start, fwd_inv, dv, scale_sch_we, done, clk, busy, edone, scale_sch,xn_re, xk_im, xn_index, xk_re, xn_im, xk_index);

input sclr , fwd_inv_we, start, fwd_inv, scale_sch_we, clk;

input [3 : 0] scale_sch;

input [15 : 0] xn_re;

output rfd, dv, done, busy, edone;

output [15 : 0] xk_im;

output [3 : 0] xn_index;

output [15 : 0] xk_re;

input [15 : 0] xn_im;

output [3 : 0] xk_index;

……

endmodule

在使用时,直接调用multiply 模块即可,如

module fft16(sclr, fwd_inv_we, rfd, start, fwd_inv, dv, scale_sch_we, done, clk, busy,

edone, scale_sch, xn_re, xk_im, xn_index, xk_re, xn_im, xk_index);

input sclr , fwd_inv_we, start, fwd_inv, scale_sch_we, clk;

input [3 : 0] scale_sch;

input [15 : 0] xn_re;

output rfd, dv, done, busy, edone;

output [15 : 0] xk_im;

output [3 : 0] xn_index;

output [15 : 0] xk_re;

input [15 : 0] xn_im;

output [3 : 0] xk_index;

fft fft1( // 调用FFT 的IPCore

.sclr(sclr), .fwd_inv_we(fwd_inv_we), .rfd(rfd), .start(start), .fwd_inv(fwd_inv),

.dv(dv), .scale_sch_we(scale_sch_we), .done(done), .clk(clk), .busy(busy),

.edone(edone), .scale_sch(scale_sch), .xn_re(xn_re), .xk_im(xk_im),

.xn_index(xn_index), .xk_re(xk_re), .xn_im(xn_im), .xk_index(xk_index));

endmodule

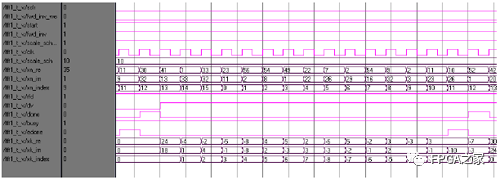

经过仿真测试得到的功能波形图如图5-59所示:

图5-59 FFT的IP core仿真波形

审核编辑:刘清

-

移动自组网IP地址分配技术综述2010-04-23 0

-

FPGA浮点IP内核有哪些优势?2019-08-13 0

-

分类规则挖掘算法综述2009-10-10 564

-

基于Xilinx_FPGA_IP核的FFT算法的设计与实现2016-05-24 809

-

面向SNP的模糊聚类算法及研究综述2021-06-08 809

-

基于机器学习的哈希检索算法综述2021-06-10 649

-

多关系网络的社团结构发现算法综述2021-06-11 696

-

FPGA在视频处理中的应用综述2021-06-19 940

-

基于蚁群算法优化的虚拟机放置策略综述2021-06-19 704

-

异构环境下的多DAG任务调度算法综述2021-06-21 805

-

基于ReliefF剪枝的多标记分类算法综述2021-06-24 611

-

基于强连接网络图的无损压缩算法综述2021-06-27 514

-

基于DNN与规则学习的机器翻译算法综述2021-06-29 693

-

改进双向快速搜索随机树算法综述2021-07-02 603

-

SVPWM控制算法及工具综述2021-09-08 637

全部0条评论

快来发表一下你的评论吧 !