CKS32F4xx系列FSMC功能简介

描述

本课讲为大家讲解CKS32F4xx系列产品的FSMC应用实例,FSMC全称是Flexible Static Memory Controller,读作灵活的静态存储控制器,顾名思义,MCU可以通过FSMC扩展静态内存,灵活则是因为支持PC卡/CF卡、SRAM、PSRAM、NOR Flash和NAND Flash等几种模式,本应用实例主要是帮助读者们学习驱动NAND Flash。注意,FSMC并不能支持如SDRAM这类型动态存储器,需要FMC功能才支持。

FSMC简介

FSMC主要框图

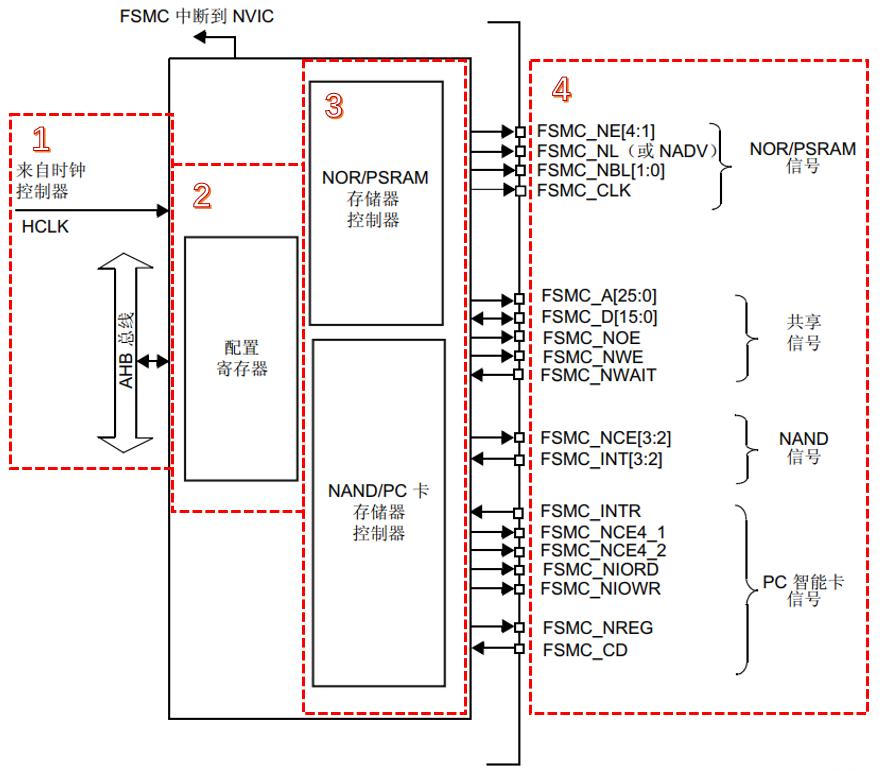

FSMC的主要思路是内核想访问存储器,但是存储器需要接收到特定的数据/地址/控制等信号,内核并不好操作,于是就诞生了FSMC外设,有了这个外设我们就无须自己写复杂的硬件时序,由配置好的FSMC替我们完成。根据配置的不同,FSMC可用于控制ROM、SRAM、NOR Flash、PSRAM和NAND Flash,其结构框图如图1所示。

图1 FSMC框图

从框图可以了解到,FSMC外设包含4个模块:AHB总线接口(包含配置寄存器)、NOR Flash/PSARM控制器、NAND Flash/PC 卡控制器、外部接口。

(1)内核通过AHB总线发送总线事务请求,AHB时钟(HCLK)是FSMC的参考时钟。

(2)配置寄存器按配置形成扩展外设的通信协议,驱动相应的存储器控制器,进而控制外设。

(3)两大控制器用于生成适当的时序,如NOR Flash/PSRAM控制器用于驱动8位、16位、32位的异步SRAM和ROM、异步或突发模式的NOR Flash和PSRAM;NAND/PC卡控制器用于驱动8位或16位的NAND Flash以及16位的PC卡兼容设备。

(4)不同外设共用一组地址数据总线、读写使能和输入等待线,此共用信号基本上涵盖了扩展外设读写所需要的所有信息,地址用于寻址,读写使能和输入等待线用于控制数据传输方向,并标识数据有效时间以同步数据。FSMC每次访问外设时,都会切换片选信号,如NOR Flash的NE信号,NAND Flash和PC卡的NCE信号,其余外设接口信号根据具体外设驱动方式分配。

FSMC设备地址映射

FSMC的外部设备地址映射划分在0x60000000~0x9FFFFFFF这一段存储空间内,我们可以直接以读写内存的形式访问存储设备,类似访问片上外设寄存器一样方便,如图2所示将外部存储器划分为四个存储块(Bank),每个Bank对应256M字节的空间,加起来FSMC总共管理着1G字节的空间。Bank1用于NOR Flash/PSRAM,最多可以连接4个存储器,Bank2/3可以各接入1个NAND Flash,Bank4则用于扩展PC卡兼容设备。本文主要探讨NAND Flash驱动,因此主要讨论块2、块3的相关配置。

图2 FSMC存储区域

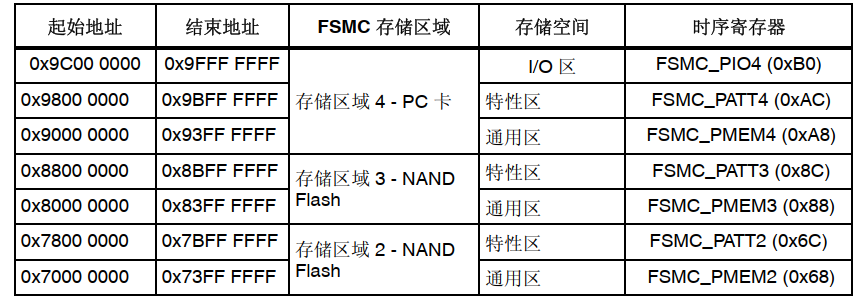

对于NAND Flash/PC卡控制器,块2.3.4被划分为表1所示的访问空间,地址映射分通用区和特性区,块4-PC卡相比多了一个I/O空间,分别由各自的时序寄存器控制访问时序。

表1 NAND Flash/PC卡地址

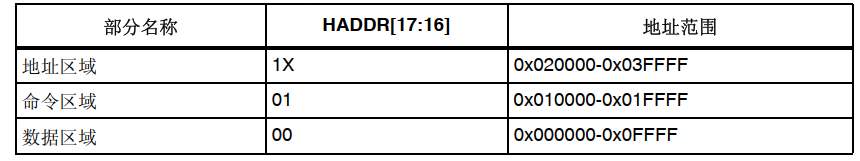

对于NAND Flash,通用空间和特性空间在其低256K字节部分划分了3个区,前64K为地址区,中64K为命令区,后128K为数据区,地址范围如表2所示。访问NAND存储空间流程简单描述为:先发送命令到命令区,其次发送需要操作的地址至地址区,最后在数据区写入或读出数据,以上流程只需要在三个区内任意地址执行即可。

表2 每个存储块的低256K字节

NAND Flash/PC卡存储器控制器

FSMC内部有两个独立的控制器分别用于驱动NOR/PSRAM内存和NAND/PC卡。由于本文所涉及的例子是驱动一个8位NAND Flash(型号K9F1G08U0E),所以这里主要讲述一下NAND/PC卡控制器。

支持设备和接口

表3列出了FSMC支持的NAND设备、访问模式和总线事务,可以看到NAND Flash/PC卡控制器能够以异步方式访问8位或16位的NAND Flash,而请求AHB操作的数据宽度可以是8位、16位、32位,为了保障数据传输的一致性,FSMC遵循以下原则:

1、AHB操作的数据宽度和外部存储器宽度相同时,无传输一致性问题。

2、AHB操作的数据宽度大于外部存储器宽度,FSMC将AHB操作分割成几个连续的较小数据宽度的存储器操作,以适应外部存储器。

3、AHB操作的数据宽度小于外部存储器宽度,异步传输时不能进行写的操作,只能进行读操作,如表3灰色部分所示。

表3 支持的存储器和事务

表4列出了用于连接8位NAND Flash的接口信号,我们主要通过地址区(A17)、命令区(A16)和数据区(D[7:0])这三个区来访问NAND Flash,注意名称前缀N表示低电平有效。

表4 8位NAND存储器接口信号

NAND Flash操作流程

以NAND Flash页读取操作流程为例,说明控制器是怎么参与操作的:

1、 根据所选8位NAND Flash的特性,配置控制寄存器FSMC_PCRx、通用区时序寄存器 FSMC_PMEMx和特性区时序寄存器FSMC_PATTx,进而配置并使能相应的存储区域

2、 根据NAND Flash命令集在通用区域的命令区执行字节写操作,将页读取的命令写入命令区,在NWE低电平时,Flash的CLE输入有效,将命令锁存。

3、 在通用区域或特性区域的地址区写入表示读操作起始地址的相应字节,在NEW低电平时,Flash的ALE输入有效,将地址锁存为读操作起始地址。

4、 借助特性存储器空间,可设置预等待功能,当写入地址结束时,控制器会等待存储器准备好,R/NB信号变为低电平后方可访问新的存储空间。

5、 在通用区域的数据区按字节读出数据完成页读取操作。

6、 后续可继续执行第五步读出数据而无需再进行命令和地址的写操作,或重新执行第三步写入新的地址,或重新执行第二步发送新的命令。

NAND Flash/PC卡寄存器

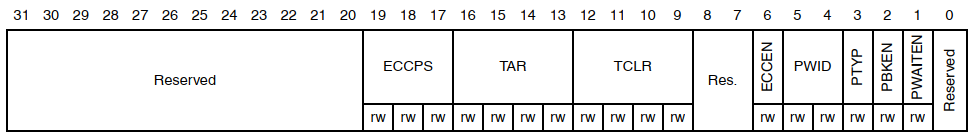

控制寄存器FSMC_PCRx

位1 PWAITE:等待特性使能位=1时,使能等待特性,注意当使能等待特性后,需配置相应等待时间,如使用读芯片忙脚作为反馈时,可关闭等待特性。

位2 PBKEN:NAND Flash/PC卡存储区域使能位=1时使能存储块功能,于FSMC_NANDcmd函数内使能。

位3 PTYP:存储器类型=1时为NAND Flash,设置0时为PC卡、PC卡等。

位5:4 PWID:数据总线宽度,用于定义外部存储器设备宽度,00时为8位,01则16位。位6 ECCEN:ECC计算逻辑使能位=1时使能ECC逻辑。

位12:9 TCLR: CLE到RE的延迟时间,从0000到1111可配置1到16个HCLK周期。

位16:13 TAR: ALE到RE的延迟时间,从0000到1111可配置1到16个HCLK周期。

位19:17 ECCPS: ECC页大小,自定义扩展ECC的页大小,000为256字节,001为512字节,最大配置101为8192字节。

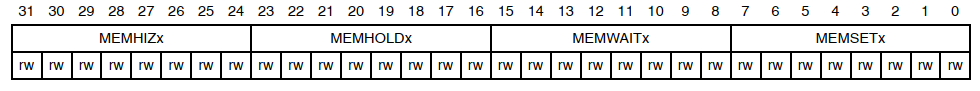

通用存储器空间时序寄存器FSMC_PMEMx

位7:0 MEMSETx:通用存储器x的建立时间,定义为读写使能命令(NWE,NOE)前建立地址所需要的HCLK周期数,可设置0x00到0xFF表示2到257个周期数(NAND Flash)。

位15:8 MEMWAITx:通用存储器x的等待时间,定义为保持读写使能命令(NWE,NOE)所需要的HCLK周期数,可设置0x01到0xFF表示2到256个周期数(再加上NWAIT变低的等待时间),0x00用于保留。

位23:16 MEMHOLDx:通用存储器x的保持时间,定义为读写禁止命令(NWE,NOE)后保持地址信号或数据信号的HCLK周期数,可设置0x01到0xFF表示1到255个周期数,0x00用于保留。

位31:24 MEMHIZx:数据总线高阻态时间,当进行写操作时,数据总线需要保持一段时间的高阻态状态,可设置0x00到0xFF表示1到256个HCLK周期数(NAND Flash)。

特性存储器空间时序寄存器FSMC_PATTx与通用寄存器一样,有同样的4个参数分别为ATTHIZx、ATTHOLDx、ATTWAITx和ATTSETx,可自行对应参考。

驱动NAND Flash示例

FSMC代码示例

(1)FSMC初始化配置:A.首先开启GPIO、FSMC、AFIO复用等三个时钟,按外接引脚配置除PD6以外所有引脚复用推挽输出,PD6忙脚作为上拉输入,然后所有脚开启FSMC复用功能。B.FSMC寄存器配置,使用外接忙脚作为应答,因此关掉等待特性,数据宽度选择8bit,使能ECC校验功能,ECC页大小为512字节,各信号时序因为外接模块,最后初始化并使能复位。

(2)进行读取NAND Flash ID号的操作,按照上一节的控制逻辑,ReadID,必须发送命令90H(H代表16进制)到命令区(命令区、地址区和数据区的地址如表2所示),接着发送0x00到地址区,最后在数据区读回32位的ID号0xECF10095。

(3)写入操作前,需要先整块擦除,命令区输入0x60,然后地址区输入要擦除的地址,再第二轮输入命令区0xD0执行擦除,函数最后返回读取当前状态的值,会持续等待设备擦除完毕或超时退出。

(4)填充TxBuffer用于写入实验,目前填充共2K的空间,刚好一个页容量。

(5)页写入TxBuffer的数据,函数的三个参数为TxBuffer、写入地址和写入页的数量,给定TxBuffer数据,写入地址为WriteReadAddr.Zone = 0x00、WriteReadAddr.Block = 0x00、WriteReadAddr.Page = 0x00,写入页数量为1。当写入页数量不为0、地址状态有效且状态已准备好时,进入循环,发送写入一次命令80H,写入列地址表示页内偏移,无偏移所以为0x00,写入行地址为当前块地址,在将Txbuffer依次连续写入数据区,完成后二次命令0x10结束写入,读NAND Flash的忙脚等待写入完成信号,等待完成后行地址递增,可进行下一个页的写入。

(6)页读取操作同页写入,命令区一次写入0x00,二次写入0x30,列地址0x00,行地址选当前页地址。二次命令写入后才读出数据给到RxBuffer。

(7)最后利用串口打印,读ID、比较TxBuffer和RxBuffer(比较前100个数据)是否一致可以看到ID识别为0xECF10095,TxBuffer和RxBuffer数据一致。

审核编辑:刘清

-

MCU微课堂|CKS32F4xx系列产品时钟配置2022-12-12 834

-

CKS32F4xx系列产品串口DMA传输2023-04-10 1039

-

CKS32F4xx系列DSP功能介绍2024-03-04 1544

-

CKS32F4xx系列RNG功能设置2023-09-08 608

-

CKS32F4xx系列DAC功能2023-11-06 849

-

CKS32F4xx系列ADC多通道DMA电压采集2023-11-06 1097

-

CKS32F4xx系列ADC单通道电压采集2023-11-06 983

-

CKS32F4xx系列低功耗模式STANDBY模式2023-11-06 476

-

CKS32F4xx系列低功耗模式SLEEP模式2023-11-06 674

-

CKS32F4xx系列低功耗模式STOP模式2023-11-06 623

-

CKS32F4xx系列产品Timer的基本使用方法-比较输出2023-11-09 854

-

CKS32F4xx系列产品Timer的基本使用方法-定时操作2023-11-09 618

-

MCU微课堂 | CKS32F4xx系列产品SPI通信2023-10-24 702

-

MCU微课堂 | CKS32F4xx系列产品GPIO口配置2023-10-24 781

-

CKS32F4xx系列ETH通信详解2023-11-10 993

全部0条评论

快来发表一下你的评论吧 !