资料下载

×

EDA,如何突破功率的瓶颈

消耗积分:1 |

格式:rar |

大小:0.5 MB |

2017-12-01

要点:

1,虽然每个小组可以优化局部功耗,但单个团队不可能创建出一个低功耗设计。反之,任何一个小组都可能摧毁这种努力。

2,功率估计是一种精确的科学。但是,只有当你拥有了一个完整设计和一组正确的矢量后,这种概念才为真。

3,对任何问题而言,处理器通常是能效最低的方法,但因为它们具备了功能多重性,一般可以用最小面积获得实现。

4,电源分配网络应能够在不损及电压完整性的情况下,维持负载。

过去十年来,功率已经成为一个关键的设计考虑,并在工程师设计与验证系统方面带来了一些巨大的挑战。物理学不再提供免费便车。

功率是能量被消耗的速率,这在十年前还不是热门,但今天已是一个重要的设计考量。系统的能耗会带来热量、耗尽电池、增加电能分配网络的压力,并且加大成本。移动计算的发展最先推动了对降低能耗的期望,但能耗的效应现在已远远超出这个范围,可能在业界带来一些最大的结构性变化。对于服务器农场、云计算、汽车、芯片,以及依赖于能源获取的泛在式传感器网络,这都是一个关键性问题。

突然改变的原因是,物理学已把工艺技术带到了90nm以下尺度。但是,随着结点尺寸越来越小,电压降低,从而造成功率的相应下降。通常,即使开发人员增加了更多功能,功率预算也会保持不变。在更小尺度下,电压的缩放更加困难,无法维持。当电压接近于阈值电压时,开关时间就会增加。为补偿这一问题,设计人员会降低阈值电压,但这样做显著增加了泄漏电流和开关电流。

设计流程中的每个阶段都对功耗有影响,从软件架构到器件物理。虽然每个小组都可以做局部的功耗优化工作,但没有一个团队可以单独创建出一个低功耗设计。反之,任何一个团队都可能摧毁低功耗的努力。这种状况就产生了一种对协同与交叉学科工具的新需求。功率问题不再止于芯片。它们遍及互连结构、威廉希尔官方网站 板与系统设计、电源控制器等诸方面。当前的EDA工具并非按功率概念而建立,这意味着设计人员要采用改进型方法,而不是从头开始的新方法。

物理原理的角色

一只芯片消耗的功率是开关(或动态)功率和无源(或泄漏)功率之和。功率的动态成分源于设计的容性负载。当某个线网从0转换到1时,这个成分通过一个PMOS晶体管充电。从电源获得的能量等于容性负载与电压平方的乘积。系统将这个能量的一半存储在电容中;另一半则耗散在晶体管上。对于从1至0的转换,不会从电源获得更多能量,但电荷要耗散在NMOS晶体管上。假设结点以频率F变化,则动态功率为FCLVDD2,其中,CL是容性负载,VDD是电压。虽然也存在其它形式的动态功率,但它们要小得多。

由于电压是平方项,因此降低电压有相当显著的效果。不幸的是,性能也与电压相关,因为增加电压会增加栅极的驱动VGS-VT,其中VGS是栅源电压,VT是阈值电压。使用较陈旧的技术时,泄漏功率并不明显。但随着器件尺度的减小,很多区域中的泄漏变得更加显著,包括栅极氧化物隧穿、亚阈值电压、反偏结点、栅极导致的漏极泄漏,以及因热载流子注入而产生的栅极电流等。

二氧化硅是常用的绝缘材料。在低厚度水平下,电子可以隧穿它。这种关系是指数型的,意味着厚度减半,泄漏增至四倍,在晶体管尺度降到130nm以下之前,这还不是一个问题。用高k电介质代替二氧化硅可以提供相近的器件性能,获得更厚的栅级绝缘体,从而降低了这个电流。

晶体管有一个栅源阈值电压,低于这个电压时,通过器件的亚阈值电流就会呈指数倍下降。当降低电源电压以减少动态功耗时,阈值电压也减小,从而使栅极电压摆幅低于器件关断的阈值。亚阈值传导会随栅极电压呈指数式变化。

在扩散区和阱之间,或在阱与基材之间的一个反偏构造,会产生小的反偏结泄漏。在MOS晶体管漏极结上的高电场效应会产生栅极导致的漏极泄漏,这通常要用制造技术来处理。栅极电流泄漏的原因是短沟道器件的阈值电压漂移,并与器件中的高电场有关。对这个效应的控制主要也是靠制造技术。

设计人员要在动态功耗和静态功耗之间做一个折中。降低电压会减小动态功耗,但增加了静态功耗。我们来看一只手机内的典型芯片。当器件工作时,泄漏要占所消耗功率的大约10%;其它90%是动态功耗。但当手机处于待机模式时(可能占到总时间的90%),芯片中的动态功耗就很少。因此,尽量减小两种功耗有着相同的重要性。

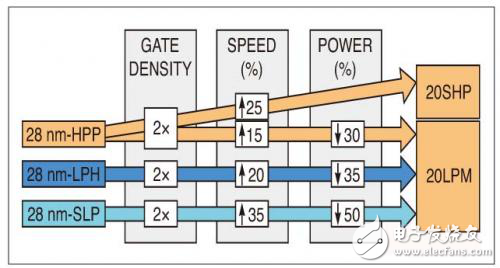

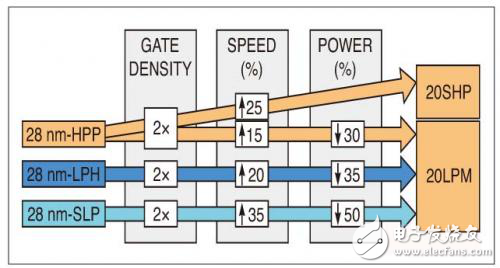

各种器件的功耗方面在持续地改进。例如,在相同频率下,三星的28nm低功耗工艺比45nm低功耗工艺的动态功耗与待机功耗都减少了35%,与采用45nm低功耗的系统单芯片设计相比,28nm工艺在相同频率下的动态功耗降低了60%.台积电28nm高性能低功耗工艺的待机功耗要比其40nm低功耗工艺低40%以上。同时GlobalFoundries公司为其28nm结点提供了三种功率水平(图1)。

图1,台积电的28-HPL工艺待机功耗较40-LP工艺低40%以上。而Global Foundries则为其28nm结点提供了三种功率水平

摩尔定律继续有效,芯片在每个器件中封装了更多功能。据Open-Silicon的营销总监Colin Baldwin称,客户可以用近似的单位成本和两倍的性能,设计出下一代器件,虽然总功耗会增加,但单只器件的功耗是下降的。时钟频率是另外一个缓慢上涨的变量,但在很多市场上增速都慢于工艺。Open-Silicon发现,大多数用户试图在略微增加总体功耗的情况下,集成更多的功能。因此,要维持相同的总功耗,就要看设计流程的其它部分中可以节省的能耗。

1,虽然每个小组可以优化局部功耗,但单个团队不可能创建出一个低功耗设计。反之,任何一个小组都可能摧毁这种努力。

2,功率估计是一种精确的科学。但是,只有当你拥有了一个完整设计和一组正确的矢量后,这种概念才为真。

3,对任何问题而言,处理器通常是能效最低的方法,但因为它们具备了功能多重性,一般可以用最小面积获得实现。

4,电源分配网络应能够在不损及电压完整性的情况下,维持负载。

过去十年来,功率已经成为一个关键的设计考虑,并在工程师设计与验证系统方面带来了一些巨大的挑战。物理学不再提供免费便车。

功率是能量被消耗的速率,这在十年前还不是热门,但今天已是一个重要的设计考量。系统的能耗会带来热量、耗尽电池、增加电能分配网络的压力,并且加大成本。移动计算的发展最先推动了对降低能耗的期望,但能耗的效应现在已远远超出这个范围,可能在业界带来一些最大的结构性变化。对于服务器农场、云计算、汽车、芯片,以及依赖于能源获取的泛在式传感器网络,这都是一个关键性问题。

突然改变的原因是,物理学已把工艺技术带到了90nm以下尺度。但是,随着结点尺寸越来越小,电压降低,从而造成功率的相应下降。通常,即使开发人员增加了更多功能,功率预算也会保持不变。在更小尺度下,电压的缩放更加困难,无法维持。当电压接近于阈值电压时,开关时间就会增加。为补偿这一问题,设计人员会降低阈值电压,但这样做显著增加了泄漏电流和开关电流。

设计流程中的每个阶段都对功耗有影响,从软件架构到器件物理。虽然每个小组都可以做局部的功耗优化工作,但没有一个团队可以单独创建出一个低功耗设计。反之,任何一个团队都可能摧毁低功耗的努力。这种状况就产生了一种对协同与交叉学科工具的新需求。功率问题不再止于芯片。它们遍及互连结构、威廉希尔官方网站 板与系统设计、电源控制器等诸方面。当前的EDA工具并非按功率概念而建立,这意味着设计人员要采用改进型方法,而不是从头开始的新方法。

物理原理的角色

一只芯片消耗的功率是开关(或动态)功率和无源(或泄漏)功率之和。功率的动态成分源于设计的容性负载。当某个线网从0转换到1时,这个成分通过一个PMOS晶体管充电。从电源获得的能量等于容性负载与电压平方的乘积。系统将这个能量的一半存储在电容中;另一半则耗散在晶体管上。对于从1至0的转换,不会从电源获得更多能量,但电荷要耗散在NMOS晶体管上。假设结点以频率F变化,则动态功率为FCLVDD2,其中,CL是容性负载,VDD是电压。虽然也存在其它形式的动态功率,但它们要小得多。

由于电压是平方项,因此降低电压有相当显著的效果。不幸的是,性能也与电压相关,因为增加电压会增加栅极的驱动VGS-VT,其中VGS是栅源电压,VT是阈值电压。使用较陈旧的技术时,泄漏功率并不明显。但随着器件尺度的减小,很多区域中的泄漏变得更加显著,包括栅极氧化物隧穿、亚阈值电压、反偏结点、栅极导致的漏极泄漏,以及因热载流子注入而产生的栅极电流等。

二氧化硅是常用的绝缘材料。在低厚度水平下,电子可以隧穿它。这种关系是指数型的,意味着厚度减半,泄漏增至四倍,在晶体管尺度降到130nm以下之前,这还不是一个问题。用高k电介质代替二氧化硅可以提供相近的器件性能,获得更厚的栅级绝缘体,从而降低了这个电流。

晶体管有一个栅源阈值电压,低于这个电压时,通过器件的亚阈值电流就会呈指数倍下降。当降低电源电压以减少动态功耗时,阈值电压也减小,从而使栅极电压摆幅低于器件关断的阈值。亚阈值传导会随栅极电压呈指数式变化。

在扩散区和阱之间,或在阱与基材之间的一个反偏构造,会产生小的反偏结泄漏。在MOS晶体管漏极结上的高电场效应会产生栅极导致的漏极泄漏,这通常要用制造技术来处理。栅极电流泄漏的原因是短沟道器件的阈值电压漂移,并与器件中的高电场有关。对这个效应的控制主要也是靠制造技术。

设计人员要在动态功耗和静态功耗之间做一个折中。降低电压会减小动态功耗,但增加了静态功耗。我们来看一只手机内的典型芯片。当器件工作时,泄漏要占所消耗功率的大约10%;其它90%是动态功耗。但当手机处于待机模式时(可能占到总时间的90%),芯片中的动态功耗就很少。因此,尽量减小两种功耗有着相同的重要性。

各种器件的功耗方面在持续地改进。例如,在相同频率下,三星的28nm低功耗工艺比45nm低功耗工艺的动态功耗与待机功耗都减少了35%,与采用45nm低功耗的系统单芯片设计相比,28nm工艺在相同频率下的动态功耗降低了60%.台积电28nm高性能低功耗工艺的待机功耗要比其40nm低功耗工艺低40%以上。同时GlobalFoundries公司为其28nm结点提供了三种功率水平(图1)。

图1,台积电的28-HPL工艺待机功耗较40-LP工艺低40%以上。而Global Foundries则为其28nm结点提供了三种功率水平

摩尔定律继续有效,芯片在每个器件中封装了更多功能。据Open-Silicon的营销总监Colin Baldwin称,客户可以用近似的单位成本和两倍的性能,设计出下一代器件,虽然总功耗会增加,但单只器件的功耗是下降的。时钟频率是另外一个缓慢上涨的变量,但在很多市场上增速都慢于工艺。Open-Silicon发现,大多数用户试图在略微增加总体功耗的情况下,集成更多的功能。因此,要维持相同的总功耗,就要看设计流程的其它部分中可以节省的能耗。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

评论(0)

发评论

- 相关下载

- 相关文章