10进制计数器设计方案汇总(六款威廉希尔官方网站 设计原理及程序分享)

应用电子威廉希尔官方网站

描述

计数器是一种能够记录脉冲数目的装置,是数字威廉希尔官方网站 中最常用的逻辑部件。计数器在数字系统中主要是对脉冲的个数进行计数,以实现测量、计数和控制的功能,同时兼有分频功能。计数器由基本的计数单元和一些控制门所组成,计数单元则由一系列具有存储信息功能的各类触发器构成。计数器在数字系统中应用广泛,如在电子计算机的控制器中对指令地址进行计数。本文为大家带来六种10进制计数器设计方案。

10进制计数器设计方案一:JK触发器实现的同步十进制加法计数器

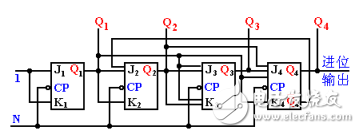

同步十进制加法计数器逻辑图

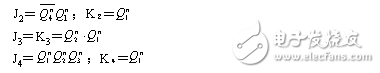

在上图所示的同步十进制加法计数器中:

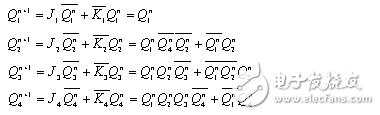

将这些关系代入各JK触发器的特性方程,则得计数器的状态方程为:

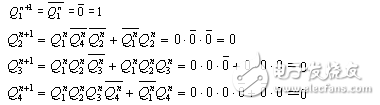

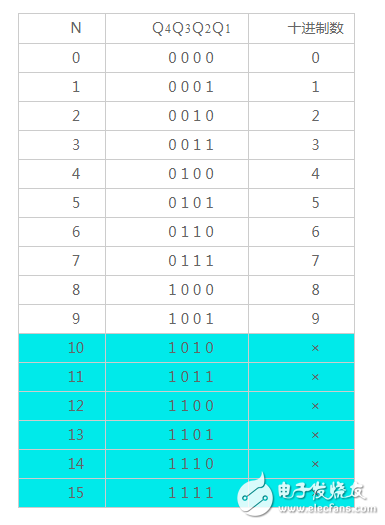

设计数器初始状态为0000,第1个计数脉冲来到后,

即计数器的状态为0001。可以算得,第2个计数脉冲来到后,其状态为0010。以下类推,可以得到如表Z1503所示的状态表。但需注意,在第9个脉冲来到后,亦即计数器处于1001态时, 的低电平封住了F2的置1端,Q1的高电平又使K4=1,故第十个计数脉冲来到后,F2、F3状态不变,F1、F4同时置0,计数器跳过多余的6个状态,完成一次十进制计数循环。结合计数脉冲的触发方式,可以断定该计数器是同步十进制加法计数器。

的低电平封住了F2的置1端,Q1的高电平又使K4=1,故第十个计数脉冲来到后,F2、F3状态不变,F1、F4同时置0,计数器跳过多余的6个状态,完成一次十进制计数循环。结合计数脉冲的触发方式,可以断定该计数器是同步十进制加法计数器。

同步十进制加法计数器状态表

10进制计数器设计方案二:CD54HC160异步复位的BCD同步十进制计数器

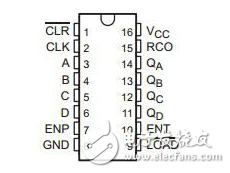

CD54HC160是具有异步复位的BCD同步十进制计数器。其引脚图如图2-30所示。其中,CLR为计数器复位端,CLR=0时,QDQCQBQA=0000;LOAD是计数器的预置端,DCBA是预置数据输入端。当LOAD=0时,在CLK的上升沿作用下,QDQCQBQA=DCBA;ENP和ENT是计数器的功能控制端,ENP和ENT均为高电平时计数器才能计数,它们中有任何一个为低电平时,计数器的装备不会发生变化,而是处于保持状态。RCO是计数器的进位输出,RCO=ENT× QDQA。

CD54HC160引脚图

步骤

1.根据十进制计数器的原理和特点,利用VHDL语言的基本描述语句编写出十进制计数器的VHDL语言程序。

2.对所设计的十进制计数器的VHDL程序进行编译,然后利用波形编辑器对其进行仿真,初步验证程序设计的正确性。

3.利用开发工具软件,选择所用可编程逻辑器件,并对十进制计数器进行管脚配置。

4.通过下载电缆将编译后的*.sof文件下载到目标器件之中,并利用实验开发装置对其进行硬件验证。

程序

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

USE IEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITY CD54HC160 IS

PORT(

CLK,D,C,B,A, CLR, LOAD,ENP,ENT: IN STD_LOGIC;

QD,QC,QB,QA,RCO: BUFFER STD_LOGIC);

END CD54HC160;

ARCHITECTURE behave OF CD54HC160 IS

SIGNAL EN: STD_LOGIC_VECTOR(1 DOWNTO 0);

SIGNAL D_SIGNAL: STD_LOGIC_VECTOR(3 DOWNTO 0);

SIGNAL Q_SIGNAL: STD_LOGIC_VECTOR(3 DOWNTO 0);

BEGIN

PROCESS(LOAD,D,C,B,A,CLK,CLR, ENP,ENT)

BEGIN

EN<=(ENP&ENT);

D_SIGNAL<=(D&C&B&A);

IF (CLR=‘0’) THEN

Q_SIGNAL<=(OTHERS=>‘0’);

ELSE IF CLK‘EVENT AND CLK=’1‘ THEN

IF (LOAD=’0‘) THEN Q_SIGNAL<=D_SIGNAL;

ELSIF (EN=“11”) THEN

IF Q_SIGNAL<“1001” THEN

Q_SIGNAL<=Q_SIGNAL+1;

ELSE

Q_SIGNAL<=(OTHERS=>’0‘);

END IF;

ELSE

Q_SIGNAL<=Q_SIGNAL;

END IF;

END IF;

END IF;

QD<=Q_SIGNAL(3);

QC<=Q_SIGNAL(2);

QB<=Q_SIGNAL(1);

QA<=Q_SIGNAL(0);

RCO<=ENT AND QD AND QA;

END PROCESS;

END behave;

10进制计数器设计方案三:74LS161的六位十进制计数器设计

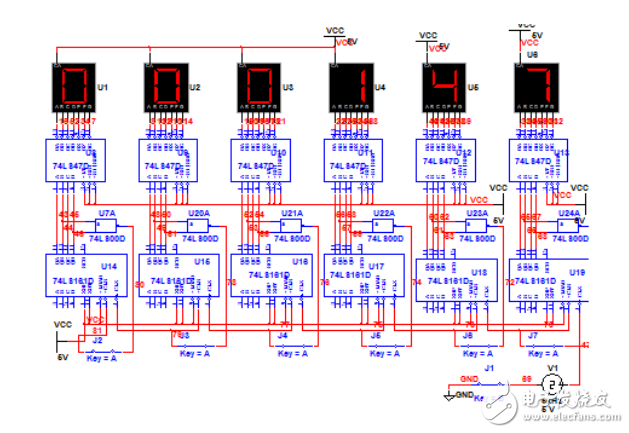

仿真威廉希尔官方网站

(如上图)脉冲信号首先进入74LS161的CLK端,其QA~QD端接入74LS47A~D后B端和D端接逻辑与非门,当74LS161计数到1010使该芯片进位,并产生一个脉冲,到下一个74LS161的CLK端如此循环完成0-999999的计数功能。用开关控制锁存完成锁存功能,其中CLK为数据输入端,QA~QD为数据输出端可以用来驱动74LS47芯片完成正常译码。开关控制CLK和CLR,当CLK和CLR为高电平时,OA---OG为正常逻辑状态,可以用来驱动显示器使其完成0—9的正常显示,当CL为低电平时,即不驱动显示器,但内部的逻辑操作不受影响。CET和CEP为锁存允许端。

10进制计数器设计方案四:verilog设计十进制计数器

设计要求:

1、每当计数器值为4’b001时,自动回到4’b0000

2、每个时钟沿计数器值加1

3、进位输出carry应该与4‘b1001同周期输出

4、异步复位

实验程序:

module cnt10 ( clk, rst_n, carry, cnt );

input clk, rst_n;

output carry;

output [3:0] cnt;

reg carry;

reg [3:0] cnt;

always @( posedge clk or negedge rst_n )

begin

if ( ~rst_n )

begin

cnt 《= 4‘b0000;

end

else if ( cnt == 4‘b1001 )

begin

cnt 《= 4‘b0000;

end

else

begin

cnt 《= cnt + 4‘b0001;

end

end

always @(posedge clk or negedge rst_n)

begin

if(!rst_n)

begin

carry 《= 1‘b0;

end

else if(cnt == 4‘b1000)

begin

carry 《= 1‘b1;

end

else

carry《= 1‘b0;

end

endmodule

View Code

测试程序:

`timescale 1ns/1ps

module cnt10_tb();

reg clk, rst_n;

wire carry;

wire [3:0] cnt;

always #10 clk = ~clk;

cnt10 cnt10_tb(

.clk(clk),

.rst_n(rst_n),

.carry(carry),

.cnt(cnt)

);

initial

begin

clk = 1‘b0;

rst_n = 1‘b1;

#10 rst_n = 1‘b0;

#10 rst_n = 1‘b1;

end

endmodule

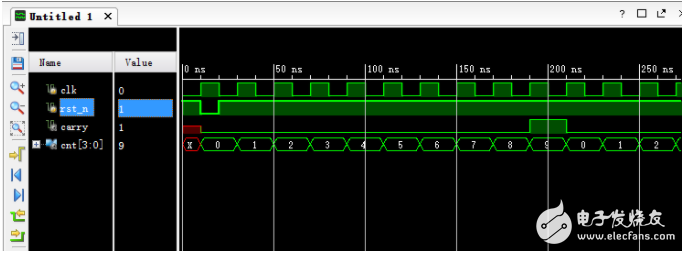

波形图

在这个十进制计数器中,唯一要注意的一点就是进位位carry变化的时刻,如果是为了使下一级能正确接收到前一级的进位位标识,要在计数到九时使进位位有效;如上图波形所示。

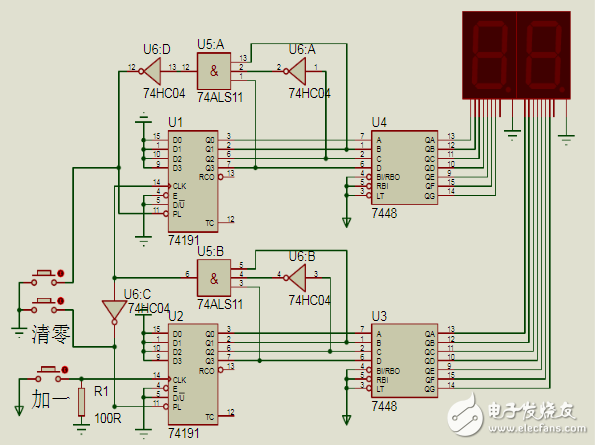

10进制计数器设计方案五:74191设计成两位十进制计数器

功能:U1的D0 D1 D2 D3 输出的个位 ,U2的D0 D1 D2 D3 输出的十位 。加一键按下数据加一,清零键按下数据清零。该单位威廉希尔官方网站

实现的记录“加一”按键按下次数,清零按键清零的功能。

工作原理:利用四位制计数器74191设计成两位十进制。个位、十位74191计数器的D0 D1 D2 D3脚接低电平,S、M脚接低电平。个位74191计数器CP脚接按键,十位74191计数器CP脚接来自个位计数器的进位信号,这样个位,十位都处于计数工作状态。个位计数器由Q3Q2Q1Q0(0000)2增加到(1001)2时产生进位信号,进位信号接传给个位计数器和十位计数器,分别实现了各位清零十位加一的功能。

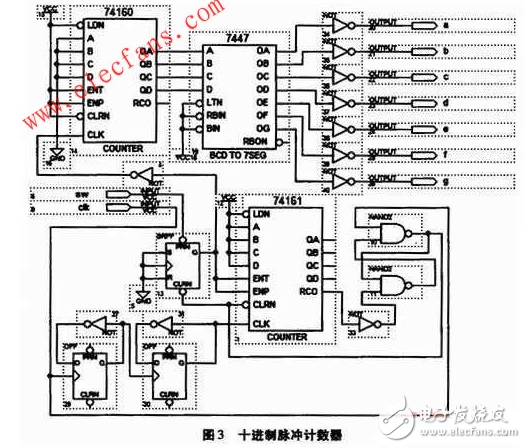

10进制计数器设计方案六:基于MAX+PLUSⅡ的十进制计数器的设计

详细威廉希尔官方网站 设计方案:基于MAX+PLUSⅡ的十进制计数器的设计

本设计采用的七段译码器威廉希尔官方网站 由7447和外部共阴极数码管构成,7447七段译码器将BCD8421码译成数码管所需的七段数显码。

(1)图形设计输入:MAX+PLUSⅡ的图形设计输入较其他软件更容易使用,因为MAX+PLUSⅡ提供丰富的库单元供设计者调用,尤其是在 MAX+PLUSⅡ里提供的mf库几乎包含了所有的74系列的器件,在prim库里提供了数字威廉希尔官方网站 中所有的分离器件。因此只要具有数字威廉希尔官方网站 的知识,几乎不需要过多的学习就可以利用MAX+PLUSⅡ进行CPLD/FPGA的设计。

(2)文本编辑输入:MAX+PLUSⅡ的文本输入和编译系统支持AHDL语言、VHDL语言、VERILOG语言三种输入方式。

(3)波形输入方式:如果知道输入、输出波形,也可以采用波形输入方式。

(4)混合输入方式:MAX+PLUSⅡ设计开发环境,支持图形设计输入、文本编辑输入、波形编辑输入的混合编辑。

-

菲仙子

2018-05-29

0 回复 举报第一个方案是用什么芯片的啊 收起回复

菲仙子

2018-05-29

0 回复 举报第一个方案是用什么芯片的啊 收起回复

-

小信号放大威廉希尔官方网站 设计方案汇总2021-09-14 2821

-

2进制计数器设计方案汇总(五款模拟威廉希尔官方网站 设计原理及过程详解)2018-01-17 23096

-

N进制异步计数器设计方案2011-10-24 3807

-

八进制计数器设计方案汇总(四款模拟威廉希尔官方网站 原理实现过程)2018-01-17 99278

-

20进制计数器设计方案汇总(三款仿真威廉希尔官方网站 设计原理详细)2018-01-17 13156

-

16进制计数器设计方案汇总(四种威廉希尔官方网站 设计原理图及仿真程序分享)2018-01-17 77813

-

12进制计数器设计方案汇总(五款模拟威廉希尔官方网站 设计原理及程序分享)2018-01-17 77295

-

5进制计数器设计方案汇总(三款计数器的威廉希尔官方网站 原理图)2018-01-17 69393

-

6进制计数器设计方案汇总(三款模拟威廉希尔官方网站 原理图分享)2018-01-17 77061

-

7进制计数器设计方案汇总(三种模拟威廉希尔官方网站 设计过程详细)2018-01-17 60620

-

任意进制计数器设计方案汇总(七款模拟威廉希尔官方网站 设计原理详解)2018-01-17 74887

-

乘法器威廉希尔官方网站 设计方案汇总(五款模拟威廉希尔官方网站 设计原理及仿真程序分享)2018-01-17 59856

-

超温报警器威廉希尔官方网站 设计方案汇总(六款模拟威廉希尔官方网站 设计原理图详解)2018-01-29 33883

-

计数报警器威廉希尔官方网站 设计方案汇总(多款模拟威廉希尔官方网站 设计原理图详解)2018-01-29 25908

-

电流检测威廉希尔官方网站 设计方案汇总(六款模拟威廉希尔官方网站 设计原理图详解)2018-02-06 326743

全部0条评论

快来发表一下你的评论吧 !