基于PCI-E接口的网络视频解码系统分析与设计

显示光电

描述

随着视频压缩技术的不断发展,单路1080p@60Hz分辨率的视频可以压缩到几兆进行传输,一个百兆网口可以传输多达10多路的IP视频信号。目前的服务器单纯依靠CPU进行软解码已经显得非常吃力[1];匹配高性能的服务器或者配置多台服务器却有存在高成本的压力。针对这些现状,本文设计了一个基于TI的DaVinci?平台的网络视频解码系统。验证结果显示,采样该网络视频解码系统,可以使得单台服务器增加上百路的IP视频解码,同时不影响服务器的其它性能,性能可靠且成本有很大优势。

1 TI 816X平台简介

DM816x DaVinci?视频处理器[2]是高度集成、可编程平台,其具有强大的视频处理能力,具备1080p@60Hz的H.264编解码能力。该平台在视频领域的应用范围非常广泛,涉及领域包含:视频编码、解码、转码和速率转换、视频安全、视频会议、视频基础设施、媒体服务器和数字标牌。

DM816xDaVinci?视频处理器包含了3个高分辨率视频和成像协处理器(HDVICP2)。每个协处理器能够执行一个1080P@60Hz的H.264编码或解码或者多个较低分辨率或帧速率的编码和解码。另外,也可完成多通道HD至HD或HD至SD代码转换以及多重编码。同时,其具备了一个数字视频输出口、一个数字视频输入口、还有一个数字视频输入输出复用口,其单个输出输入口还具备了多路视频同时分时输出、输入功能。芯片内部集成了Cortex?-A8 32位RISC处理器处理器和DSP内核,同时还集成了3D图象引擎SGX530。DM816x DaVinci?视频处理器提供了丰富的外设。视频接口有同步HD和SD模拟视频的输出和双HD视频输入;网络接口包含了2个具有GMII和MDIO接口的千兆位以太网,两路千兆网提供了多路IP视频接入的传输通道。丰富的外设集提供了控制外围设备以及与外部处理器进行通信的功能。

2 系统结构和工作原理

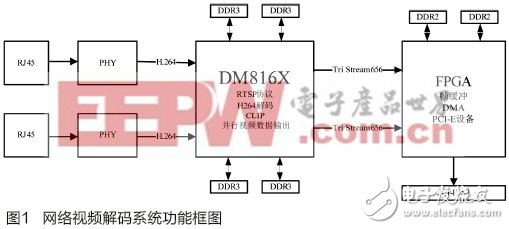

该网络视频解码系统采用DM816X和FPGA的方案,具体功能框图如图1。前端网络采用千兆网络PHY芯片,速率为10M/100M/1000M自适应。一般来说,网络IP视频从异地过来,均是通过一个路由进入到系统的前端网络采集模块;不通的路由支持支持的速率不通,同时线路的连接方式也相异,因此,我们这里采用了速率自适应和线路自适应的PHY芯片。在PHY片的另外一侧是MAC口,对应的是解码芯片的MAC口,采用的是千兆通信方式,网络时钟的速率是125MHz。从带宽上来看,前端网络可以支持高达几百路的D1视频接入,从而保证了海量视频数据接入的可能。

IP视频解码部分是采用TI的DM816X芯片为核心,外挂DDR和Flash等设备组成。在DM816x芯片上嵌入Linux操作系统,作为整个单板的主控系统,管理各种外设,包括网口、DDR、可调电源模块和Flash等,还可通过对FPGA模块进行寄存器读写来管控后端的视频处理环节。目前网络视频大部分带有数据打包协议,我们这个系统可以支持标准的RTSP协议,同时也支持非标准的数据包,只有给出前端打包协议,就可以自定义解网络数据包。网络解包后,得到H.264码流后,便送入到816x内置的解码器(HDVICP2)进行解码;解码后的数据可以利用816x的视频处理系统进行裁剪、缩放和叠加。经过一系列处理后,将图像通过816x的2路视频数据输出通道进行输出。虽然在物理通道上只有2路视频输出口,但是,通过软件编程,可以采用Tri Stream 656的方式,分时输出6路1080p@30Hz的视频信号到视频缓冲和显示处理模块。

视频缓冲和显示处理模块主要由FPGA芯片和位于服务器上的显卡组成。经过解码芯片处理后的视频数据进入到FPGA后,还不能直接进入到显卡。首先,逻辑芯片需要对视频数据进行帧缓存,把数据先放进DDR2中,在DDR2中建立3帧图像存放空间,通过控制读取视频帧的速度达到帧率调整的目的。逻辑内部的PCI-E设备传输数据是采用串行传输,而从缓冲区出来的是并行视频数据,这个时候需要对视频数据进行并串转换。在服务器端的显卡,通过驱动软件可以开辟出一块显存区域用于存放并显示视频数据。一般和PC系统进行数据交互采用DMA方式是最为高效直接的,因此,我们将开辟处理的显存区域映射到PCI-E设备中,通过逻辑程序把视频数据通过DMA方式放入到映射区域。这样,就相当于直接把视频数据放入到显卡中进行显示。

整个视频平台工作上电后,816X首先从Flash中加载相关程序,并将Linux文件系统解压出来在DDR中运行。IP视频信号经过解码后形成6路并行YCbCr信号(每3路共用一个输出通道),加上像素时钟(DCLK)、数据有效位(DE)、行同步信号(HS)、场同步信号(VS)输给后端FPGA进行处理。逻辑芯片接收到并行视频信号后,先根据预定好的分时传输协议中解出6路单独的视频信号,分别放置在DDR的不同区域中;完成6路视频的缓存和仲裁后,根据系统的需求对视频数据进行DMA操纵,通过PCI-E设备把视频数据送入系统进行显示。

3 硬件设计

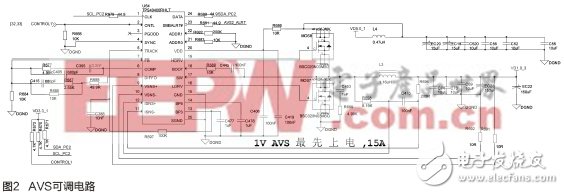

DM816X模块的硬件威廉希尔官方网站 主要由主芯片816X、4片DDR3、Fash、网络PHY片和电源模块组成组成。网络PHY芯片采用Mirel的KSZ9031,该芯片体积小、功能全、支持速率自适应、双绞/直连线调节功能。该芯片和DM816X的EMAC(Ethernet Media Access Controller)口直接连接,把网络数据接入到DM816X。主芯片外部挂有4片DDR3,主要用做816X的内存映射空间和视频处理的缓冲区域,可以在软件小系统中进行自由配置。同时,主芯片外部还带一个Nand Flash,用于存储引用程序和系统文件。在芯片外围,根据应用需要放置硬件配置威廉希尔官方网站 ,把系统配置成网络启动。因为芯片对电源的精度和上电时序均有严格要求,因此专门针对该芯片设计了上电时序威廉希尔官方网站 和AVS可调电源。芯片的上电时序要求为3.3V》1V AVS》1V Constant》1.8V》1.5V》0.9V,为此,采用了专用时序控制芯片LM3881MM对上电时序进行了控制。主芯片因为采用了先进的制造工艺,其核心电压1V AVS对应每个芯片均有一个精准值,在芯片运行过程中,也会因为工作状态而调整核心电压,所以针对该电压也设计了专门的可调电源供电威廉希尔官方网站 [4],具体威廉希尔官方网站 模块见图2。图2中,电源芯片采用TPS40400,其输出端通过反馈威廉希尔官方网站 送回反馈管脚,芯片带有IIC的Slave模块,连接到816x主芯片。在上电开始后,主芯片会读取相关寄存器,反馈给电源芯片具体的电源调整精准值;在系统运行过程中,如果同时开启了3个解码核,会使得芯片功耗需求增加,主芯片也可以通过IIC通讯通知电源芯片调整电源输出。

FPGA硬件威廉希尔官方网站 模块实现相对简单,主要包括了PCI-E接口的FPGA芯片、DDR2、存储Flash、JTAG接口和电源模块。逻辑芯片采用ALTER的A7系统芯片,采用SPI加载逻辑的方式进行加载,外挂4片DDR2使用两个控制器对视频数据进行缓存。JTAG接口主要用于逻辑程序调试。操作系统端连接采用PCI-E接口,由逻辑芯片内存自带的PCI-E硬核实现。

4 DM816X软件设计

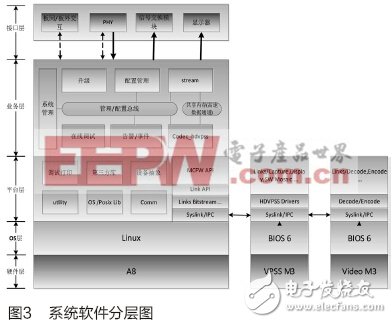

为了便于软件功能的移植、替换、添加和删除,整个软件采用层次式和模块化的软件结构。纵向分布由5个层次组成,从下向上,分别是硬件层、OS层、平台层、业务层、接口层。横向分布由3个子系统构成,从左至右,依次是A8核子系统、HDVPSS M3核子系统、Video M3核子系统,具体结构见图3。

硬件层是软件系统运行的硬件平台,其核心是TMS320数字多媒体处理器,由A8、HDVPSS M3、Video M3、DSP 4个核构成,其中HDVPSS M3、Video M3核是M3核。本软件没有使用到DSP核,所以硬件层由A8、HDVPSS M3、Video M3 3个核构成。

OS层是硬件层上的操作系统层,由Linux、BIOS 6两个操作系统构成。Linux运行A8核上,BIOS 6运行在M3核[5]。

平台层运行在操作系统层上,屏蔽软硬件复杂性,抽象业务层所需要的功能接口,向上支撑业务层。基于A8核的平台层由调试打印、第三方库、设备抽象、utility、OS/Posix Lib、Comm以及MCFW多通道框架接口构成。MCFW是TI提供的一套用来处理多媒体视频的接口。A8核端由Syslink/IPC、Link Bitstream、Link API、MCFW API组成。VPSS M3核端由Syslink/IPC、HDVPSS Drivers、Links Capture/Display/SW Mosaic组成。Video M3核由Syslink/IPC、Decode/Encode、Links Decode/Encode组成。核与核之间的数据交互由Syslink/IPC实现。816X是一个多核SOC设备,各个核之间的通信需要通过软件设计来实现。芯片的主处理器是A8,A8核端的Link API用来创建、控制、连接Links。通常由该处理器引导加载各个从处理器,包括了Video-Media Controller,VPSS-Media Controller等。其中解码核实由Video-Media Controller负责管理的。引导加载过程包括从处理器的电源管理,复位控制,在合适的寄存器中写入从处理器执行的入口点。为了有效地实现多核通信,软件还充分利用了邮箱中断和自旋锁功能实现。Mailbox为处理器通过写寄存器,向其他处理发送中断机制。A8,Media Controller等之间通过系统级的Mailbox进行通信。3个HD VICP2S的IP模块有各自独立的邮箱。SOC通过自旋锁[6](SpinLock)方便实现了系统共享资源的互斥。

业务层由系统管理、在线升级、配置管理、stream、在线调试、告警/事件、codec_hdvpss几个模块组成。管理/配置总线用来实现业务层模块间的通信,共享内存(高速数据通道)用来实现stream模块与codec_hdvpss模块之间的高速数据传递。系统管理模块是A8软件子系统首先执行的一个模块,实现初始化系统资源、创建运行其他的模块,最后监听其他模块的运行状态以及喂狗、控制运行状态。升级模块是一个较为独立的模块,不会与其他模块有数据交互。实现3个核的软件程序文件的在线升级。配置管理是业务层的中控模块,接收主控板发过来的配置信息,控制、协调其他几个模块的运行。Stream模块与网络交互,获取网络发过来的码流数据,经共享内存(高速数据通道)传递到模块做进一步处理。在线调试模块是一个较为独立的模块,不会与其他模块有数据交互,实现软件的在线查看运行状态等功能。告警/事件模块向主控发送本软件的告警/事件信息。Codec_hdvpss模块从共享内存(高速数据通道)获取码流数据,进行codec以及视频处理输出。

接口层有三个部分,分别是板间/外交互、PHY、信号交换模块。板间/外交互是指解码板与主机的交互,接收主控板的配置管理消息,处理并返回。PHY模块是指解码板与网络的交互,获取H.264的码流。信号交换模块是指解码板输出视频数据到逻辑芯片的数据交换模块。

软件系统的主要功能是最大支持同解6路1080P@30 H.264码流,解码延时小于50毫秒(Codec模块收到码流数据到解码输出到FPGA的延时);同时还具备启动、监听其他任务,监控单板硬件状态,管理系统硬件狗、运行灯,接收主控的配置信息,对软件系统以及硬件系统进行配置,检测到有异常或某些重要事件发生等功能。

5 总结

本文根据目前一些网络视频解码应用现状限制,提出了一种带PCI-E接口的网络视频解码系统。该系统采用了目前TI强大的视频编解码平台DM816X并和FPGA逻辑芯片联合应用,实现了单板6路1080P@30Hz/32路D1的网络视频解码;在单台服务器中可以插入多张该单板,从而实现上百路网络视频解码,同时不会降低服务器的性能。该设计系统在笔者设计的视频解码平台中得到实际应用和验证,运行效果良好,并大大降低了单路视频解码的成本,具有很高的实用价值。

-

基于MATLAB的系统分析与设计——时频分析2012-02-28 0

-

解决台式机PCI-E 1X不够难题 :乐扩PCI-E 1X转2口PCI-E 1X扩展卡2017-10-19 0

-

指令系统分析2006-03-21 1139

-

系统分析ppt2008-11-07 771

-

PCI-E接口定义 引脚定义图 PCI-E针脚定义图2008-04-27 78399

-

什么是系统分析?2008-11-07 2830

-

频域相位编解码系统分析2009-02-28 1228

-

基于MATLAB的系统分析与设计信号处理2016-01-15 668

-

基于SVPWM的变频系统分析设计2016-04-18 421

-

系统分析方法2017-12-06 819

-

PCI-E接口的固态硬盘和SATA接口的区别是什么2020-07-28 4746

-

M.2和PCI-E接口固态硬盘的区别是什么2020-07-28 9854

-

pci-e插槽的规格有哪些 各个版本的pci-e的规范区别2023-08-05 9065

-

单端口网络S参数测量系统分析2024-01-05 681

-

测量系统分析2024-10-10 108

全部0条评论

快来发表一下你的评论吧 !