解决串行接口中的信号完整性问题

接口/时钟/PLL

描述

一直以来,信号完整性都是模拟工程师考虑的问题,但是随着串行数据链接的传输速率向GHz级发展,数字硬件设计人员现在也必须关注这个重要的问题。

目前,芯片之间的高速串行链接已经获得了广泛的应用,用于提高较窄的总线带宽的吞吐量。一些最新的DSP和处理器已经开始采用串行RapidIO对于很多硬件设计人员来说,芯片间通讯使用超过300MHz的总线速率是一个新的挑战,而设计出GHz级数据传输速率的高质量数据链接则要求更多的细心和了解,才能确保威廉希尔官方网站 板设计和噪音不会损害到性能。

本文探讨设计人员可能会面临的一些信号完整性(SI) 问题和注意事项,重点介绍他们面临的问题,并提出一些建议。为了举例说明如何应用这些原则,本文介绍了一种16 端口串行RapidIO交换机。

注意事项

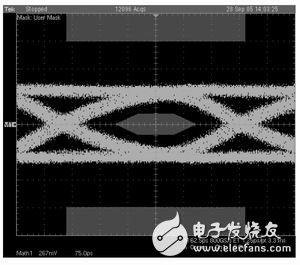

信号质量非常重要,在串行RapidIO 中,它是通过接收眼的大小和形状来量化的。接收眼是一种无限延续的轨迹,在接收眼中,波形会随着上一个轨迹不断延续(图1)。如果信号路径中吸收了噪音或其它随机信号,便会引起信号抖动和接收眼收缩,从而导致信号质量下降。

图1 包含一个接收眼图的范围轨迹

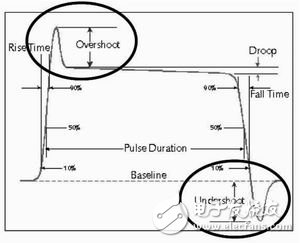

图2 脉冲过冲和下冲的典型特征

在超过300MHz 的频率上,适用于较低频率威廉希尔官方网站 板设计的大部分最佳做法都需要修改。FR4材料或许还能够成功用作基础材料,但是在更高的频率上,则需要在阻抗计算和轨迹建模中重新考虑材料的介电常数和损耗系数。通孔通路的设计也变得十分重要,因为未使用的管状长度会表现出同较厚的威廉希尔官方网站 板和背板不匹配的阻抗。请贴出设计模拟以便对性能进行检验,并注意信号完整性不太理想的路径,同时指出串音区域。

阻抗不匹配造成的反射会导致形成差分对的信号线(图2)出现过冲、下冲和振铃,以及接收眼缩小。

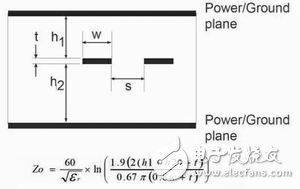

布线层的变更、跳出路径设计不当和连接器选择不当也会造成信号中产生不匹配的人为干扰。串行RapidIO 接口的阻抗要求是100Ω差分。建议的构造方法是采用边缘耦合差分带状线(或称共面带状线),图3 显示的正是这种方法,图中同时提供了单端和差分阻抗的方程式。布线时应当最大限度地减少在不同层之间的转换。除了BGA 衬垫之外,通常每个路径最多允许两个通路。

回流电流路径的定义是电流回到出发点时经过的路径- 通过地层、电源层、其它信号路径以及通过IC。返回路径的完整性可通过绘制一个追踪电流从驱动器经信号导线到达接收器的环路来进行评估- 循环的区域越小,产生的自感应系数也越低。

以下设计规则适用于所有的返回路径。

-不要通过参考层的裂口传送受阻抗约束的信号。

-不要在参考层上传送信号。

-更改信号层不能强迫返回路径对参考层进行更改。如果必须对参考层进行更改,请从一个VSS 参考层更改到另一个VSS 参考层,并在尽可能接近信号通路的地方放置一个连接这两个层的通路。此规则同样也适用于从一个VCC 层到另一个VCC 层进行参考层更改。

-不要通过通路反面衬垫或插槽反面衬垫发送信号。

如果属于不同信号组的路径之间距离太近,则便会造成串音。在串行通讯链接中,结果就是由于抖动而造成接收眼闭合。出现这种情况也可能是因为路径曲线实施不当,一部分信号采用短路径(曲线的跳跃足),而主信号却采用长路径,从而引起路径长度匹配出现问题。在非常密集的设计中,串音可以通过使用保护路径来解决,在保护路径中线路平行地到达信号路径并连接到参考。

时钟产生和缓冲可能会导致噪音,除非非常注意一些细节,例如去耦和制造商的布局指南,这样才能确保最高质量的输出。必须严格控制路径的阻抗,以避免产生不希望的反射。设计的复杂性以及在电源层和地层引入布线间隙也可能会导致时钟产生器产生很高的噪音。

如果没有为瞬时电流提供足够的铜线或者去耦电容器的位置不当,那么便会造成电源分配。单端平行总线会在电源层和地层产生瞬时电流,从而产生噪音。

在高比特率系统中应当使用由专为高频率和G 级应用而设计的电缆和连接器组成的互连。使用错误的类型或者电缆和连接器搭配不当将会降低信号的质量,而且不能恢复。

在选择组件时,必须选择一家合适的制造商,其组件应该专为解决高速设计问题而设计。设备必须提供充足的功耗能力以及正确放置和分隔的地面连接,以避免芯片核心供应不稳定,避免增加噪音,并利用有效的退耦策略进行补充。对于控制噪音来说,核心逻辑电源和地面同I/O电源和地面之间的分隔也是至关重要的。合适的设备加上优秀的设计将有助于满足高速要求,并使设计人员能够有效地解决信号完整性问题。

图3 建议的边缘耦合差分带状线配置,图中给出了单端阻抗Z0 和差分阻抗Zdiff 的方程式

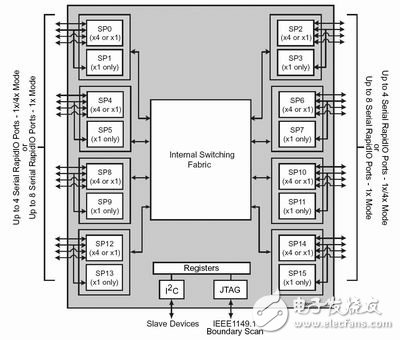

图4 Tsi568A串行RapidIO交换机接口的结构图

16端口串行交换机

Tundra Semiconductor 公司 Tsi568A是一种基于标准的高性能16 端口串行RapidIO交换机。RapidIO 是一种专为满足当前和未来嵌入式应用需要而设计的点对点分组交换互连协议,它能够在处理器、桥、远程内存或嵌入式应用中的数据层处理元素之间提供高速的串行互连。图4 显示了该设备的主要组件。

最典型的应用是无线嵌入式通讯(节点B、无线网络控制器和媒体网关)。

Tsi568A 专为实现最高的信号完整性标准而设计,它包含了低噪音逻辑核心和高性能倒装芯片BGA 封装等功能。

结语

只要遵循一些基本但是十分重要的设计原则,就能够在系统中使用高频率互连(例如RapidIO)而不会遇到传统的信号完整性不佳的问题。如果能够尽量缩短路径和信号通道,采用地层进行屏蔽,或是彼此之间能够保证物理隔离,并且能够仔细避免阻抗不匹配,那么便可以轻松获得良好的信号完整性。

-

时序分析-- 信号完整性问题(SI)2014-05-16 0

-

高速DSP 数据采集的信号完整性问题2009-05-18 416

-

在高速设计中,如何解决信号的完整性问题?2010-01-02 1190

-

数字威廉希尔官方网站 设计的信号完整性问题探讨2011-09-07 1988

-

识别和修复pcb信号完整性问题2019-10-12 2859

-

什么因素导致信号完整性问题?2020-09-26 8578

-

信号完整性问题与PCB设计2021-03-23 773

-

常见的信号完整性问题及解决方案2022-10-09 4187

-

基于PDN共振峰的最坏情况数据模式分析电源完整性对FPGA DDR4存储器接口中的信号完整性的影响2023-09-13 184

-

PCB设计中的信号完整性问题2023-11-08 749

-

高速PCB设计,信号完整性问题你一定要清楚!2024-04-07 546

-

高速PCB信号和电源完整性问题的建模方法研究2024-09-21 171

-

听懂什么是信号完整性2024-12-15 151

-

如何解決信号完整性问题2024-12-25 376

全部0条评论

快来发表一下你的评论吧 !