优化铜互连结构的热应力分析与介电材料选择

描述

摘要:

基于Ansys有限元软件,采用三级子模型技术对多层铜互连结构芯片进行了三维建模。研究了10层铜互连结构总体互连线介电材料的弹性模量和热膨胀系数对铜互连结构热应力的影响,在此基础上对总体互连线介电材料的选择进行优化。结果表明,总体互连线介电材料的热膨胀系数对铜互连结构的热应力影响较小,而弹性模量对其影响较大;各层介电材料热应力与弹性模量成正比,SiN界面热应力与弹性模量成反比。最后,为了降低铜互连结构关键位置热应力,通过选用不同参数材料组合对总体互连线介电材料的选取进行优化,提高了铜互连结构可靠性。

0引言

随着集成威廉希尔官方网站 制造技术进入数十纳米级,金属互连线的宽度不断减小、层数不断增加,更细更长的金属互连线的电阻-电容(RC)延迟时间已无法忽略,因此采用铜、低介电常数(low-k)介电材料代替铝、二氧化硅来降低RC延迟[1-2]。在多层铜互连结构中,封装过程中因芯片与基板间的热膨胀系数不匹配而产生热应力,直接耦合到low-k介质中驱动界面分层[3],引发可靠性问题。对low-k介质热应力的可靠性研究备受关注。

目前,国内外学者们的研究内容是封装过程中芯片与基板间的热膨胀系数不匹配引发的互连可靠性,即芯片封装交互作用[3-11]。X.F.Zhang等人采用了四层铜互连结构,通过计算裂纹扩展的能量释放率研究了介电材料属性对能量释放率的影响[3-4]。S.Raghavan等人计算铜互连结构裂纹扩展的能量释放率,得出能量释放率最大的位置区域[5]。C.J.Uchibori等人采用四层铜互连结构,使用SiO2分别替代M4层介电材料low-k、SiOC层,能量释放率降低了34%、35%[6-7]。L.L.Mercado等人通过计算裂纹J积分研究了铜互连结构介电材料、互连层数对裂纹扩展的影响[8]。L.Lin等人研究了铜柱、焊料、PI开口等尺寸参数对铜互连结构热应力的影响[9-10]。M.W.Lee等人研究了硅层厚度、基板厚度、PI层厚度、铜柱高度、焊点数量等对铜互连结构low-k层热应力的影响[11]。

在铜互连结构中,互连级与封装级的尺寸相差较大,直接对其建模仿真会占用巨大计算资源。采用多级子模型技术可有效解决这一问题。对于铜互连结构,可采用四级子模型技术进行建模[3-4,6-7],但计算精度不高。也可采用二级子模型技术建模[8-9],但需总体模型精细网格来保证子模型的计算精度。

本文提出了一种降低铜互连结构关键位置热应力的优化方法。综合考虑计算资源和精度,本文采用三级子模型技术进行结构建模。采用针对10层铜互连结构,研究不同的总体互连线介电材料对铜互连结构介电材料热应力的影响。在此基础上,进一步对总体互连线介电材料进行优化,降低超低介电常数(ultralow-k,ULK)和SiN界面热应力,最终提高了铜互连结构的可靠性。

1建模与参数选择

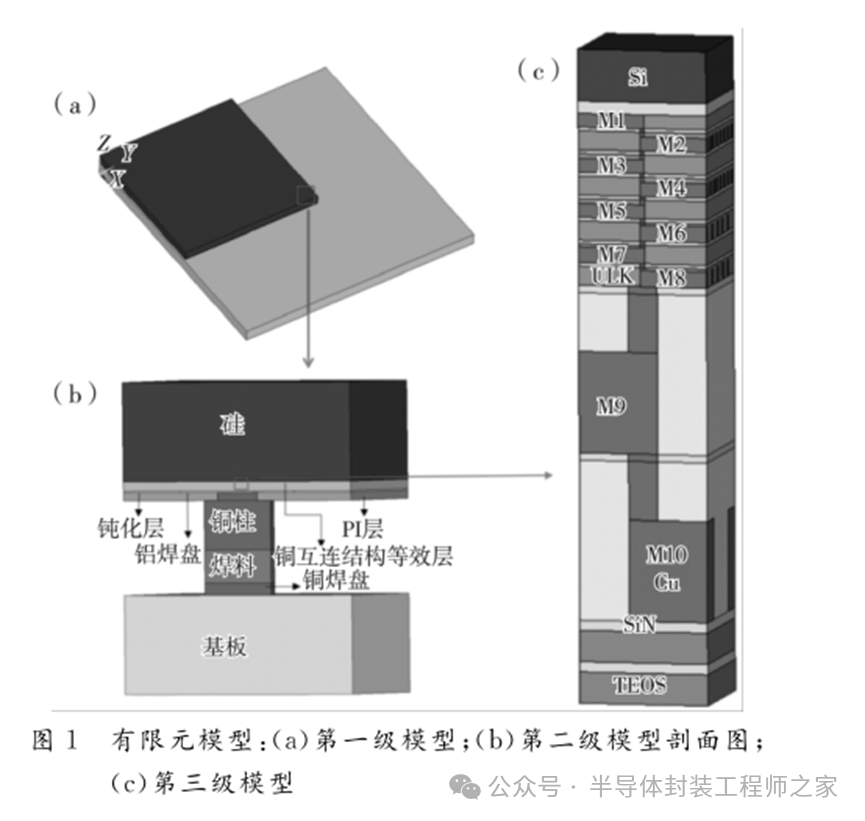

本文使用对称边界条件约束对称模型中心点的所有自由度,禁止产生刚性位移。基于有限元软件,本文采用三级子模型技术,建立了铜互连结构芯片的三维模型,有限元模型如图1所示。

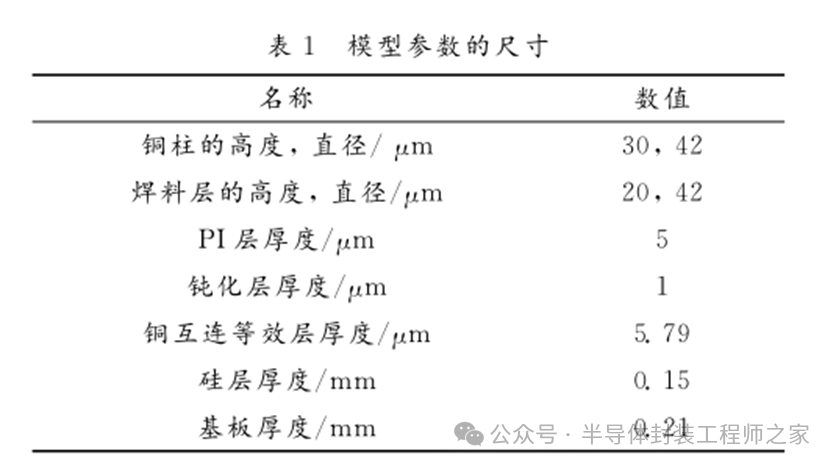

考虑到芯片对称性,采用芯片的1/4结构建模,第一级模型如图1(a)所示。铜互连结构部分比整个芯片模型的基板和硅层的厚度都薄很多,构建第一级模型时采用均匀等效层替代铜互连结构,使铜互连结构参与芯片整体模型的形变,该方法的精度不受影响[9-10,12]。第一级模型包括PI层、钝化层、等效层、铜焊点、基板、硅层等,它们的尺寸如表1所示[13-14]。

第二级模型主要针对关键焊点区域,其建模区域源自第一级模型的求解结果,即热应力值最大区域,如图1(b)所示。第二级模型区域位于距芯片最远处的焊点位置,模型边界条件是将第一级模型计算的位移场通过插值,施加到切割边界处,切割边界需远离热应力集中区域。第二级模型包括部分硅、部分基板、铜焊点、PI层、钝化层,其中铜焊点包括铜柱、焊料、正八边形铝焊盘和铜焊盘。采用均匀等效层替代铜互连结构。

第三级模型是是铜互连结构模型,如图1(c)所示,其包括10层。模型边界条件是将第二级模型位移场通过插值,施加到切割边界处。M1~M8层使用ULK作为介电材料。

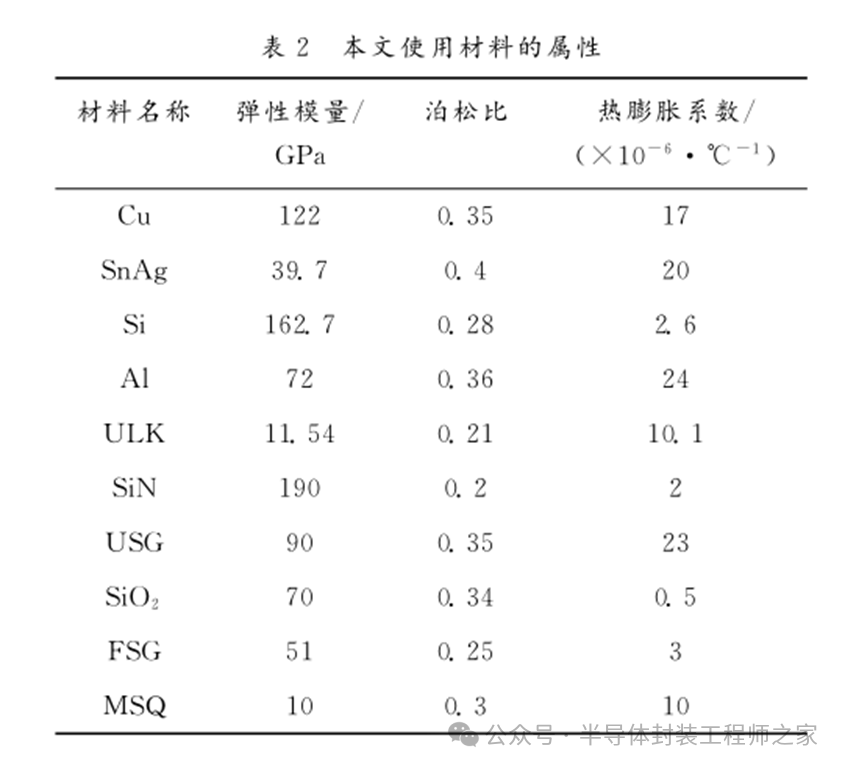

在芯片封装交互作用研究中,常采用芯片回流焊的温度作为载荷。虽然回流焊过程中峰值温度远低于制作工艺的峰值温度,但是,芯片封装交互作用在low-k界面产生的能量释放率远远大于制作工艺产生的能量释放率,且大于low-k界面的临界能量释放率[15]。因此,芯片封装交互作用会导致铜互连结构low-k界面的断裂、分层,引发可靠性问题。将回流焊的温度作为最高温度载荷,因填充胶会缓解铜互连结构的热应力,所以本文仿真模型没有使用填充胶。假设封装过程中整体温度变化均匀,220℃回流焊温度设为焊料的热应力自由温度,温度以1℃/s的速率降至室温25℃。本文使用的材料属性如表2所示[7,10-11,17]。

2结果分析与讨论

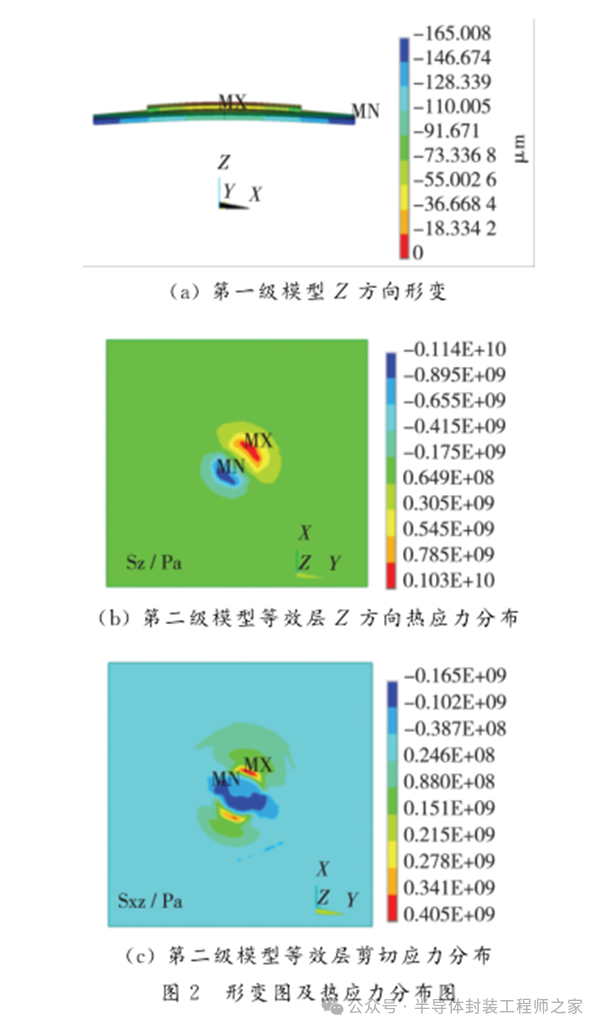

本文第一级模型的形变及第二级模型热应力分布图如图2所示。

温度载荷作用后第一级模型Z方向形变如图2(a)所示。可以看出,封装芯片的形变呈中间凸起状,基板边角部分的形变大于芯片边角部分。基板边角承受了最大的形变。原因是,基板的热膨胀系数(16×10-6·℃-1~23×10-6·℃-1)比硅大得多,且硅和基板在所有材料中的占比最大,降温过程中基板收缩的速度比硅快得多,所以引起模型的形变呈凸起状。

第二级模型等效层Z方向的热应力分布如图2(b)所示。图中,红色部分是拉应力,为正值,蓝色部分是压缩应力,为负值。等效层受拉应力的作用区域大于压缩应力。

第二级模型等效层剪切应力分如图2(c)所示。可以看出,在封装过程中,等效层同样受剪切应力的影响,但其最大值小于Z方向热应力值。可知,铜互连结构Z方向热应力占据主导地位。根据材料力学最大拉应力强度理论,需通过第一主应力对铜互连结构进行研究。

2.1总体互连线介电材料的弹性模量和热膨胀系数对热应力的影响

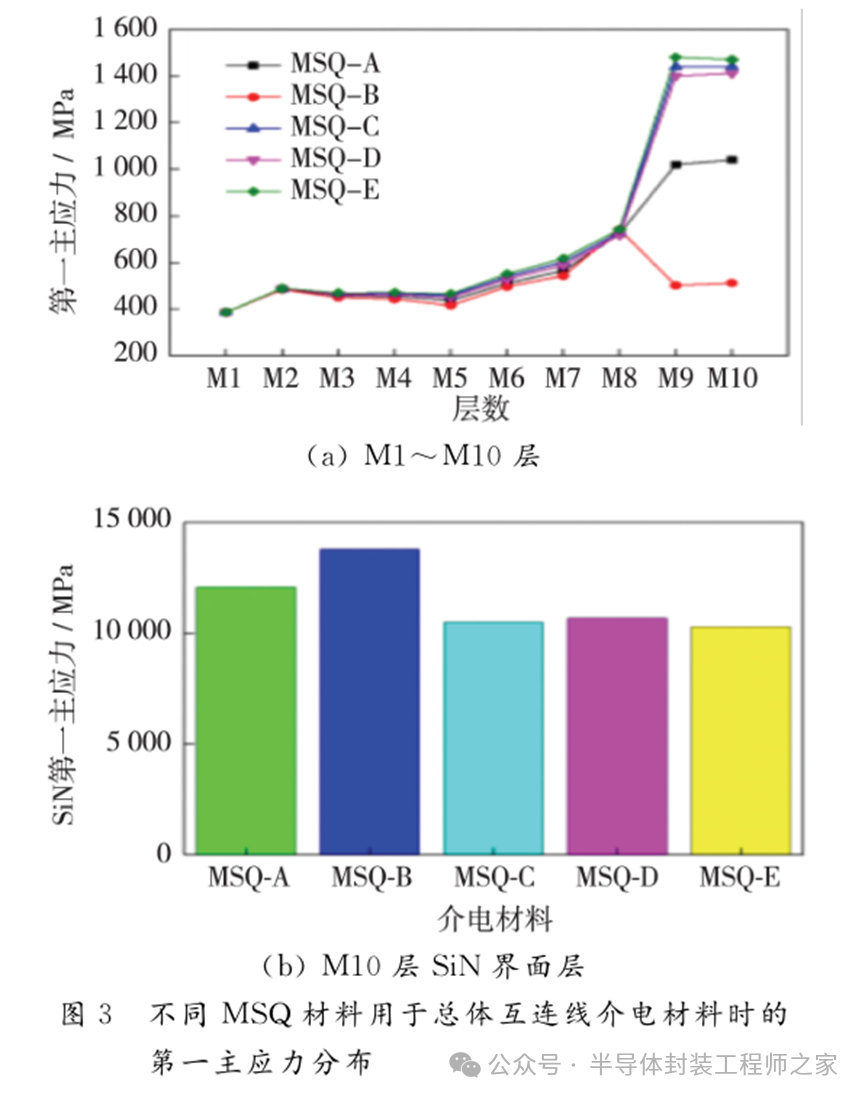

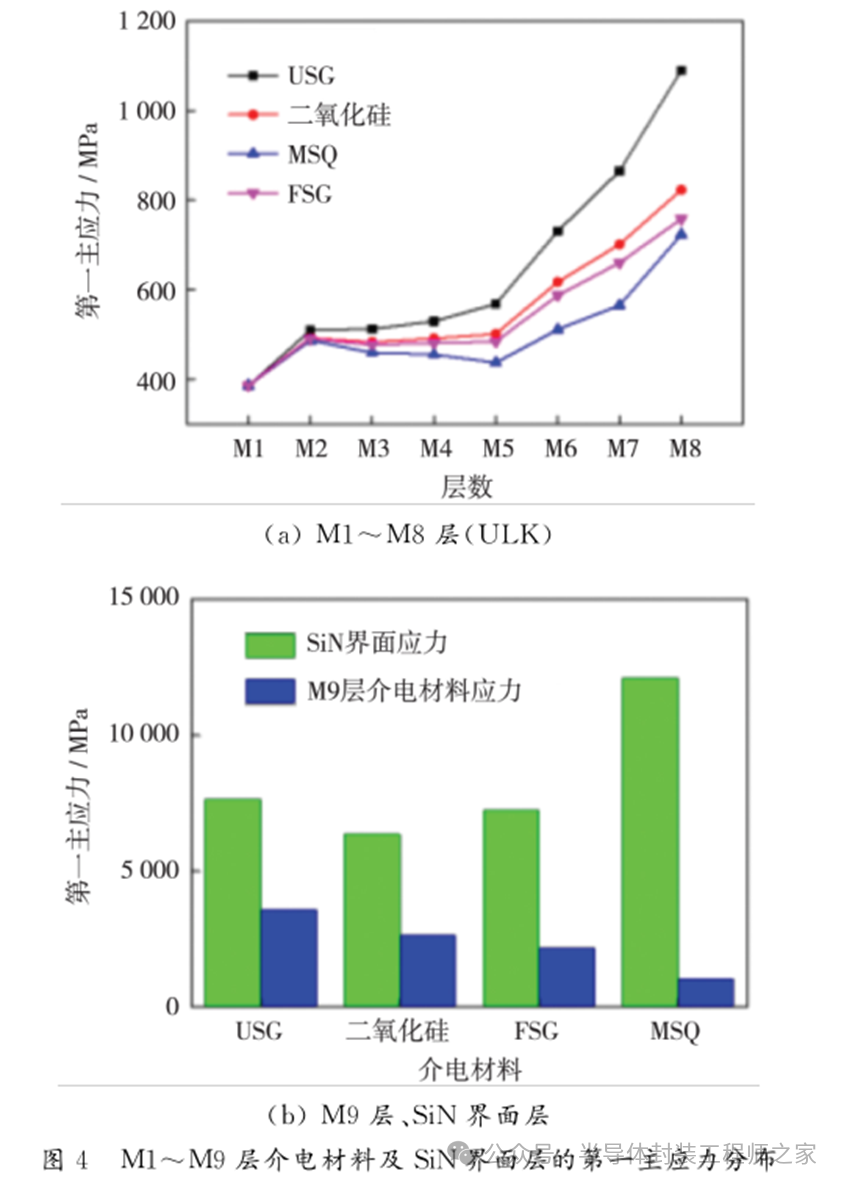

不同MSQ材料用于总体互连线介电材料时的第一主应力分布如图3所示。采用三级子模型技术对10层铜互连结构进行分析。M1~M8层介电材料使用ULK。M9、M10层为总体互连线,介电材料使用不同的MSQ材料(假设),材料参数如表3所示[3]。

图3(a)所示为M1~M10层介电材料的热应力分布。可以看出,总体互连线使用不同介电材料时,对M1~M8层使用ULK时,热应力值很小,变化趋势相同,热应力均在M8层时达到最大值。原因是,铜焊点的热应力值很大,M8层离铜焊点的距离更近,易产生集中热应力而引发可靠性问题,M1层的热应力值最小、安全。不同MSQ作总体互连线介电材料时,M9层与M10层的热应力值基本相同,但随着材料参数的变化,热应力值整体明显变化。MSQ材料热膨胀系数相同时,弹性模量越小,热应力值越小。如MSQ-B中M9层的热应力值小于M8层,原因是MSQ-B与ULK的弹性模量值相差较大,ULK抵抗形变能力比MSQ-B强,导致ULK热应力较大。MSQ材料弹性模量相同时,随着热膨胀系数的变化,热应力变化并不明显。可知,M9层、M10层的热应力取决于其弹性模量。

图3(b)所示为M10层顶部相邻的SiN界面层的热应力分布。可以看出,MSQ-B作总体互连线介电材料时,SiN界面层的热应力值最大;MSQ材料热膨胀系数不变时,SiN界面层热应力与MSQ材料的弹性模量成反比;热膨胀系数对SiN界面层的热应力影响较小。SiN界面层的热应力值明显比M1~M10层大。原因是,MSQ介电材料的弹性模量比SiN界面层小得多,其抗变形能力很弱,导致M10层顶部相邻的SiN界面层出现热应力集中现象,引起SiN界面分层、断裂,从而影响铜互连结构的可靠性。

综上可知,总体互连线介电材料的热膨胀系数对M9、M10层和SiN界面层的热应力影响较小,但对弹性模量的影响较大。根据胡克定理σ=εE(σ、ε表示应力和应变,E表示弹性模量),温度载荷下形变取决于不同材料的热膨胀系数失配,则总体模型形变取决于芯片与基板间的热膨胀系数失配。铜互连结构在总体模型中占比很小,其对总体模型形变的影响很小,所以总体互连线介电材料的热膨胀系数对M9、M10层的热应力影响不大,弹性模量对热应力的影响较大。M9、M10层热应力与总体互连线介电材料的弹性模量成正比,SiN界面层的热应力与弹性模量成反比。

2.2不同的总体互连线介电材料对铜互连结构热应力的影响

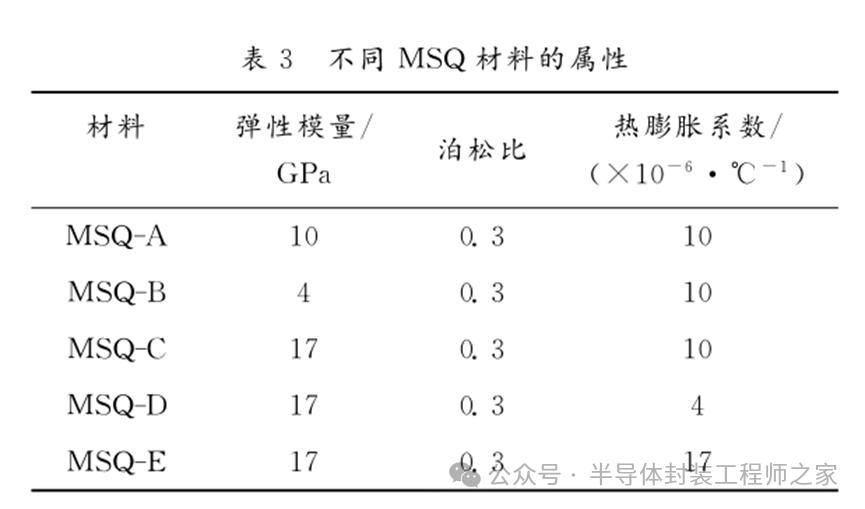

通常采用USG、SiO2、FSG等材料作铜互连结构的总体互连线介电材料[7,10,17]。M1~M9层介电材料及SiN界面层的第一主应力分布如图4所示。

USG、SiO2、FSG和MSQ分别作总体互连线介电材料时,M1~M8层(ULK)的热应力分布如图4(a)所示。可以看出,弹性模量越大,各层热应力值越大,M1层热应力值最小。M1~M2层热应力值迅速增大,之后M2~M5层热应力缓慢变化。原因是,M2层比M1层厚,且M2~M5层厚度相等。从M6层开始,热应力值呈迅速增加的趋势,M8层热应力达到最大值。ULK材料的机械特性低、粘附性差,过大热应力引起铜互连结构的分层、断裂。因此,M8层是易发生断裂失效的关键位置之一。

对于不同的总体互连线介电材料,M9层与M10层的热应力值基本相同(从图3(a)可知),因此图4(b)只给出了M9层和与M10层相邻SiN界面层的热应力对比。显然,与M10相邻SiN界面层的热应力值远大于M9层。可知,与M10相邻SiN界面层也是易发生失效的关键位置之一。

从MSQ、FSG到SiO2,它们的弹性模量不断增大,SiN界面热应力不断减小。USG介电材料的弹性模量虽最大,但其SiN界面热应力值却不是最小、略大于SiO2、FSG,这源于USG有较大的热膨胀系数而引起的较大热应力。

对于不同的总体互连线介电材料,M9层热应力值从大到小的排序为:USG>SiO2>FSG>MSQ。从图4(a)可知,M8层热应力从大到小的排序为:USG>SiO2>FSG>MSQ,表明M8层热应力值与M9层热应力密切相关。为了减小M8层热应力,需使用弹性模量较小的介电材料,但这又使得SiN界面层热应力值较大。因此,需要进一步对总体互连线介电材料选取进行优化。

2.3总体互连线介电材料的选择优化

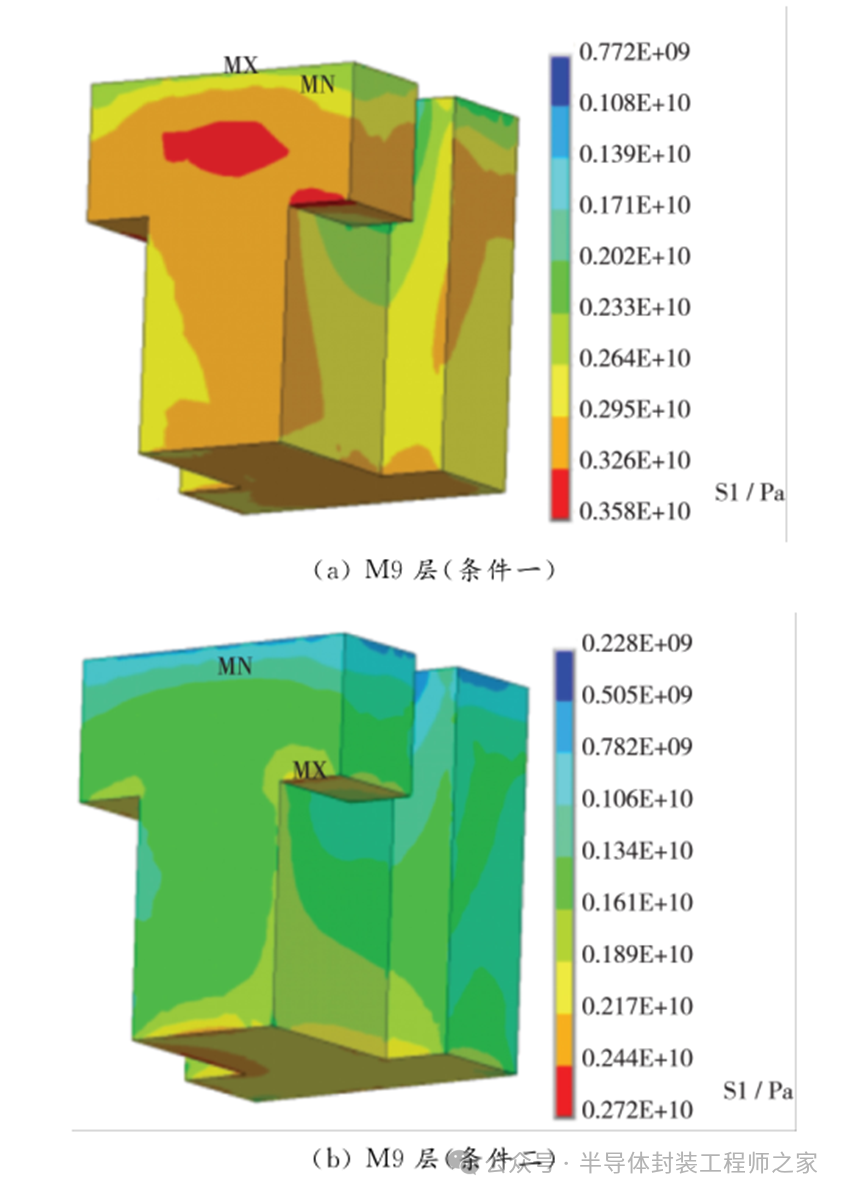

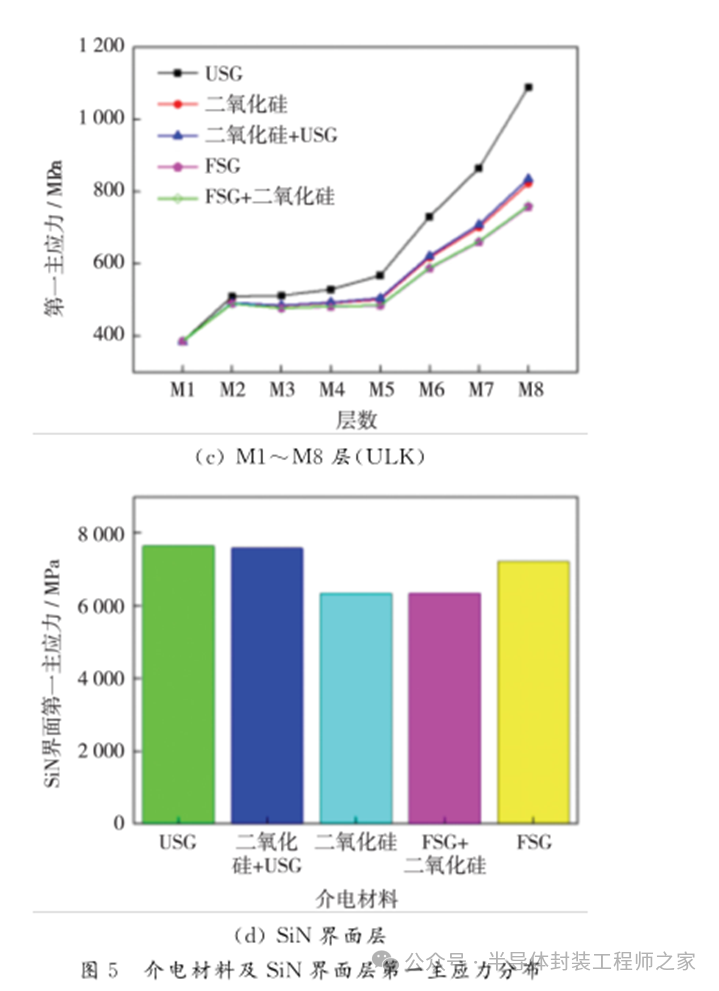

从上述分析可知,为了提高铜互连结构的可靠性,不仅要减小SiN界面层热应力,还要降低M8层(ULK)热应力值。对这两类热应力影响最大的是M9层、M10层介电材料的参数。介电材料及SiN界面层第一主应力分布如图5所示。

图中,“USG”表示M9、M10层均使用USG,“SiO2”表示M9、M10层均使用SiO2。“SiO2+USG”表示M9层使用SiO2、M10层使用USG,“FSG+SiO2”表示M9层使用FSG、M10使用SiO2。以此类推。

采用“USG”时,M9层(条件一)的热应力分布如图5(a)所示。可以看出,热应力最大值位于M9层的边界区。该区域与M8层相邻,造成M8层热应力值增加,易引发可靠性问题。

采用“SiO2+USG”时,M9层(条件二)的热应力分布如图5(b)所示。可以看出,M9层热应力值远小于图5(a)的热应力值,最大热应力值位于M9层中间位置,距离M8层较远,其对M8层热应力的影响降低。这表明,对M9、M10层的优化有助于降低关键位置的热应力。

M9、M10层使用不同介电材料组合时,M1~M8层(ULK)热应力分布如图5(c)所示。可以看出,与采用“USG”相比,采用“SiO2+USG”时热应力值明显降低,而采用“FSG+SiO2”时热应力值进一步降低。采用“SiO2+USG”时,M1~M8层热应力值与采用“SiO2”时热应力值基本相等。采用“FSG+SiO2”时,M1~M8层热应力值与采用“FSG”时热应力值基本相等。这表明,M1~M8层热应力值取决于M9层介电材料,与M10层介电材料关系不大。M9层选择弹性模量较小的介电材料时,能有效降低M8层热应力值。

M9、M10层使用不同介电材料组合时,SiN界面层热应力分布如图5(d)所示。可以看出,采用“SiO2+USG”时,SiN界面层热应力值与采用“USG”时热应力值基本相等;采用“FSG+SiO2”时,SiN界面层热应力值与采用“SiO2”时热应力值基本相等。因此,SiN界面层热应力值与M9层介电材料的关系不大,取决于M10层介电材料。M9、M10层选择合适的介电材料,有利于提高铜互连结构的可靠性。采用“FSG+SiO2”时,M8层、SiN界面的热应力值都达到最小值。

3结论

基于Ansys有限元分析软件,以10层铜互连结构为研究对象,采用三级子模型技术对多层铜互连结构芯片进行三维建模。仿真分析了总体互连线介电材料的弹性模量、热膨胀系数对铜互连结构热应力的影响。结果表明,铜互连结构的热应力取决于总体互连线介电材料的弹性模量,而与其热膨胀系数关系不大。为了提高铜互连结构的可靠性,不仅要减小SiN界面层热应力,还要降低M8层(ULK)热应力值。最后,对M9层、M10层的介电材料进行优化,降低铜互连结构关键位置的热应力,提高器件可靠性。

-

封装中的界面热应力分析2012-02-01 0

-

直接互连结构在数据交换中的应用分析2009-02-23 600

-

什么是直接互连结构(direct interconnecti2009-02-23 1773

-

金属介电核壳结构纳米材料的应用2009-03-06 1025

-

多核密码处理器中的片上网络互连结构研究2017-01-03 615

-

TSV互连结构传输性能分析及故障建模研究2017-01-07 625

-

可延展电子金属导线通用互连结构研究2018-03-16 656

-

热冲击与热应力的相关特点介绍2019-05-17 6665

-

PCB | 高速BGA 封装与PCB 差分互连结构的设计与优化2019-05-29 4270

-

互连应力测试的作用及优势介绍2019-05-30 6263

-

深度分析:BGA封装与PCB差分互连结构的设计与优化资料下载2021-04-19 723

-

高速BGA封装与PCB差分互连结构设计2022-08-26 775

-

技术资讯 I 多层 PCB 的热应力分析2023-04-13 1891

-

多层 PCB 的热应力分析2023-11-27 1003

-

基于数值计算的模拟仿真方法进行碲镉汞芯片的热应力分析2023-11-26 1082

全部0条评论

快来发表一下你的评论吧 !