RGMII接口及其时序规范

描述

1 接口定义

RGMII 由 GMII (Gigabit Media Independent Interface) 简化演变而来,意为 Reduced GMII,是常见的以太网 MAC 和 PHY 之间的通信接口,优点是比 GMII 减少了近一半的管脚,节约设计成本。

RGMII 支持 10/100/1000Mbps 三种通信速率,接口定义如下:

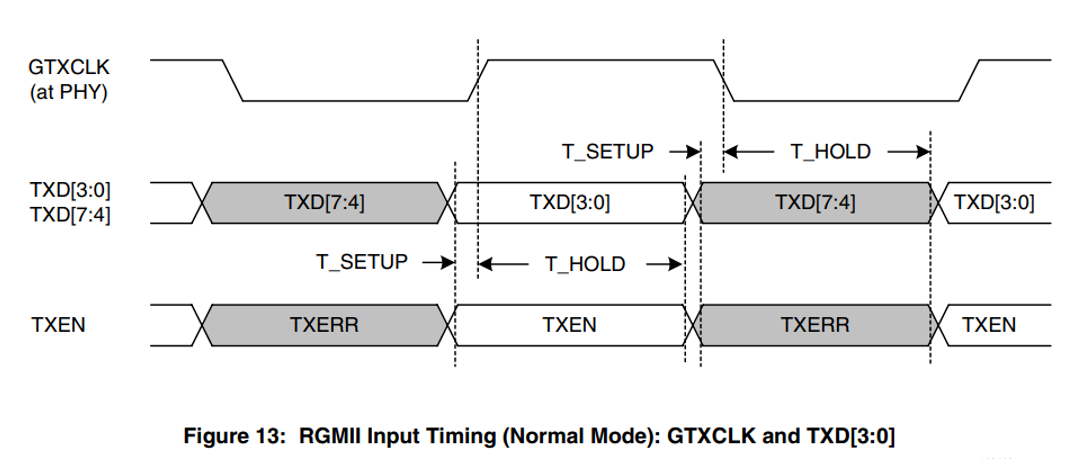

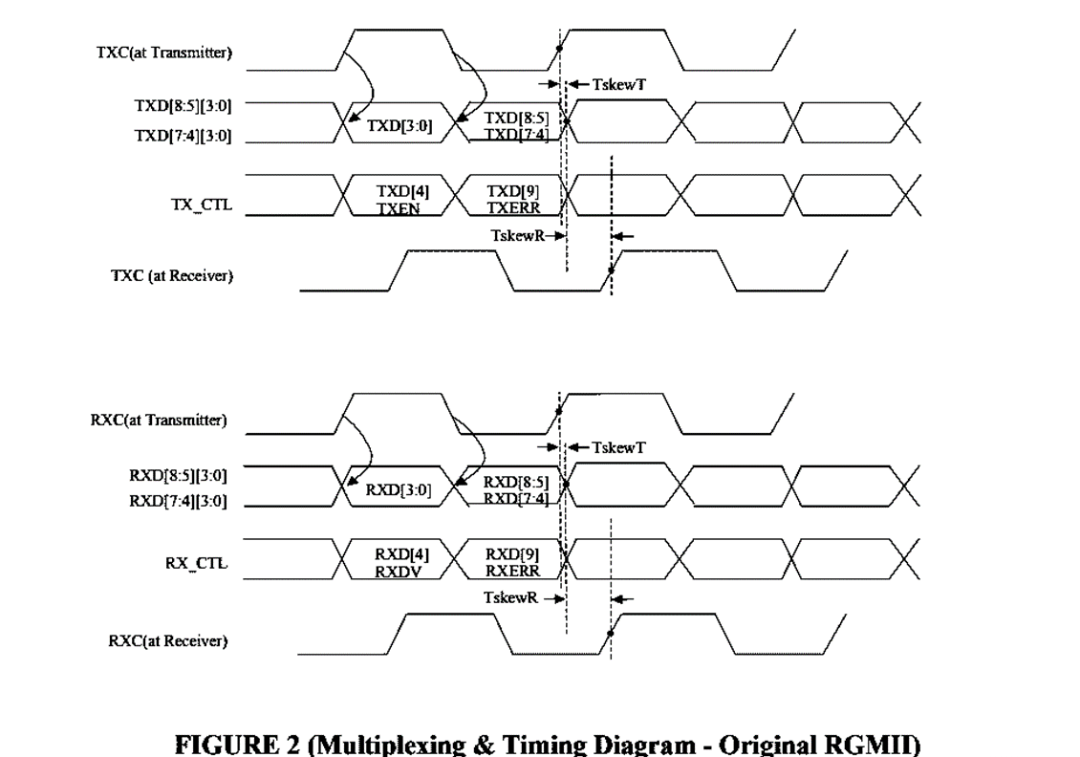

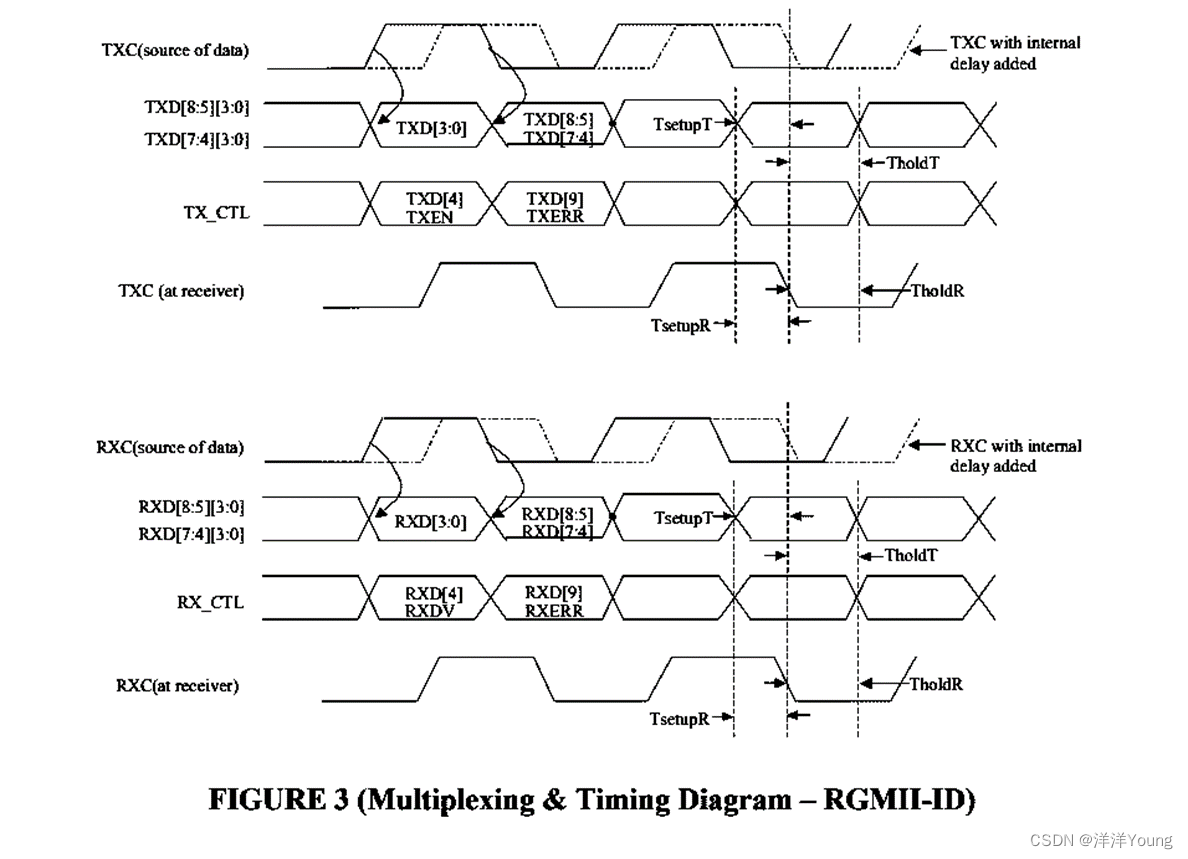

在 10/100Mbps 模式下,TXD[3:0] 和 RXD[3:0] 采用单边沿传输方式。在 1000Mbps 模式下,TXD[3:0] 和 RXD[3:0] 采用双边沿传输方式。对于发送通道,TXC 上升沿传输 TXD[3:0] 和 TXEN;TXC 下降沿传输 TXD[7:4] 和 TXERR(即 TX_EN xor TX_ER)。

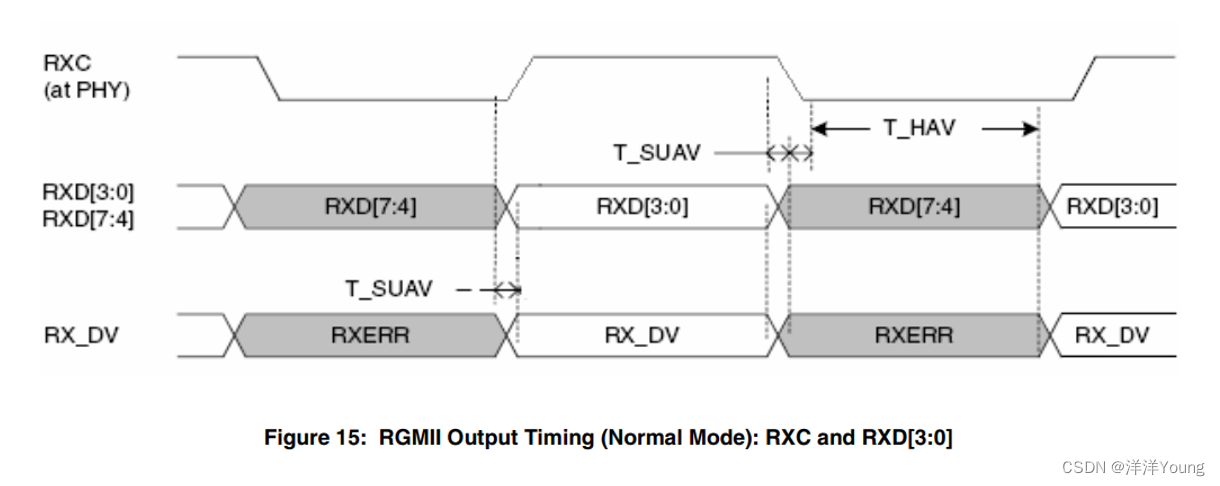

对于接收通道,RXC 上升沿传输 RXD[3:0] 和 RX_DV;RXC 下降沿传输 RXD[7:4] 和 RXERR(即 RX_DV xor RX_ER)。

2 时序规范

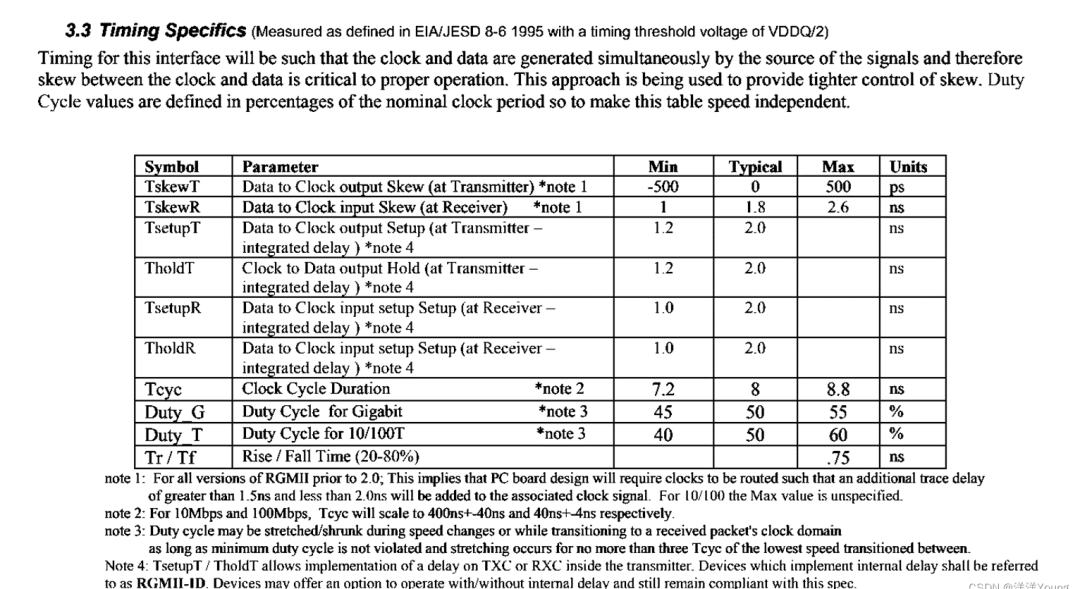

RGMII 接口时序在时钟和数据边沿对齐的条件下进行规范。在 Transmitter 端,时钟边沿与数据边沿的偏差为 ±500ps,建立/保持时间不少于1.2ns;在 Receiver 端,时钟边沿对数据边沿的延迟介于 1.0 ~ 2.6ns 之间(典型值为 1.8ns),建立/保持时间则不少于 1.0ns.

在 1000Mbps 模式下,时钟周期为 8±0.8 ns,占空比为 50±5%,上升/下降时间(20-80% 电压)不超过 0.75ns.

2.1 Original RGMII

在 RGMII v2.0 之前的规范中,Receiver 端时钟延迟由 PCB 布线实现,附加延迟值大于 1.5 ns 且小于 2.0 ns,称为 Original RGMII.

2.2 RGMII-ID

在 RGMII v2.0 中,Receiver 端时钟延迟可以由 Transmitter 端设备实现,称为 RGMII-ID(Internal Delay,意为内部延迟)。带有内部延迟功能的设备仍需遵守 RGMII Timing Specifics.

-

IIC的定义及其时序简析2022-02-23 0

-

单片机网络的例程中底层用的接口是RGMII吗?2022-09-15 0

-

解决以太网RGMII通信的电源时序难题2024-08-27 117

-

FPGA使用RGMII接口的88E1512搭建网络通信系统2021-07-07 0

-

GMII和RGMII主要的接口2021-07-29 0

-

FPGA 控制 RGMII 接口 PHY芯片基础2023-06-06 0

-

如何使用VIO去读取PHY里面对应寄存器测试RGMII接口2020-11-06 4136

-

RGMII接口信号和帧格式_RGMII接口应用框图2020-09-30 31640

-

RGMII应用框图/接口信号/帧格式2020-12-14 7087

-

基于RGMII+phy的典型应用快速入门2021-09-29 6813

-

RGMII接口转GMII接口的实现思路2023-06-09 2410

-

Xilinx KU系列三速以太网IP核RGMII时序约束方法2023-07-07 3951

-

RGMII接口案例:二个设备共享一个PHY2023-11-27 8397

-

通过磁珠解决RGMII延时不够案例2024-01-05 3300

-

SPI、UART、RGMII、JTAG接口的低电压转换2024-08-30 116

全部0条评论

快来发表一下你的评论吧 !