微电子所在高性能注入锁定时钟倍频器方面取得进展

描述

人工智能、机器学习、云计算等应用的发展推动了智算/数据中心交换网络数据传输速率的迅速增长,对高速有线收发机系统中的时钟倍频器的工作速度、抖动、面积和功耗等性能提出了更高的要求。基于环形振荡器的注入锁定时钟倍频器具有低抖动多相时钟产生、紧凑布局、高能效和高鲁棒性等优势,成为有线收发机系统中多相时钟产生的有效解决方案。但注入锁定时钟倍频器面临固有注入相位误差、最优注入脉冲宽度及其随PVT变化的漂移等挑战,限制了注入锁定时钟倍频器性能的进一步提升和推广应用。

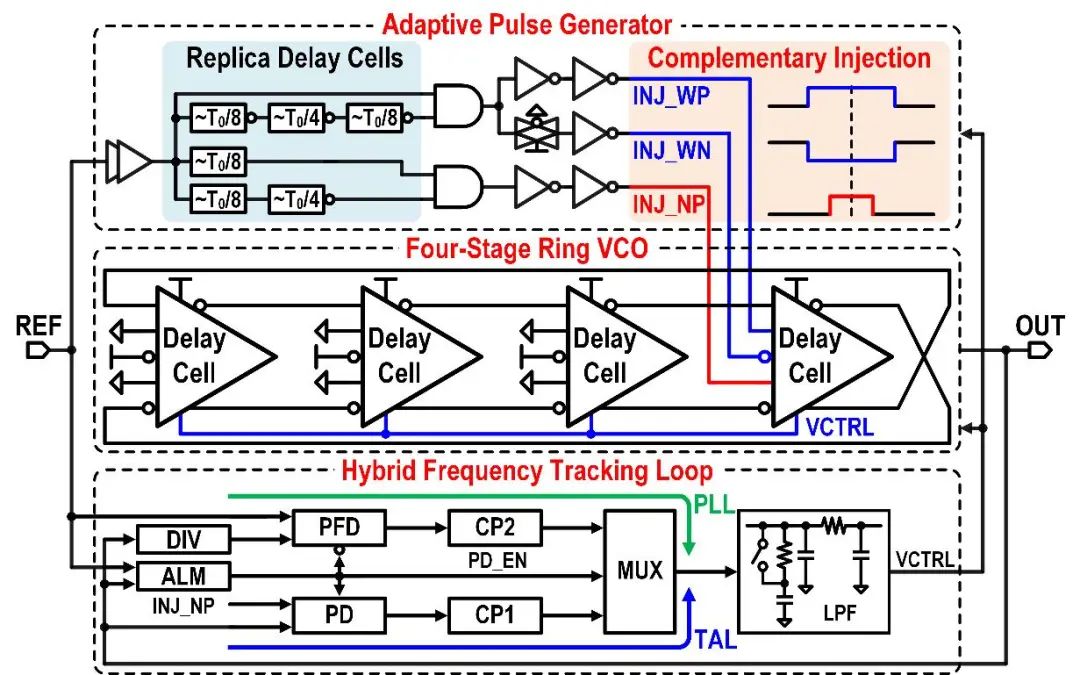

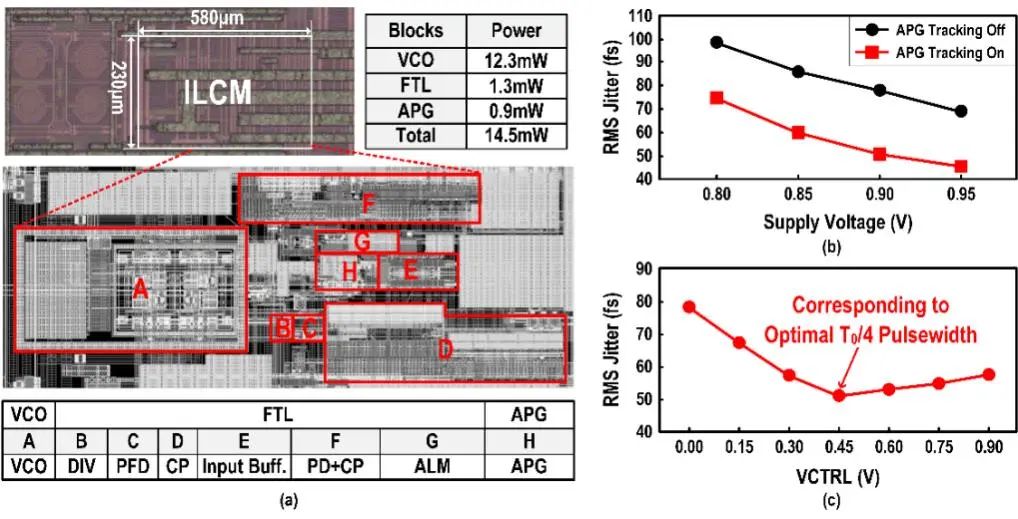

针对上述关键问题,微电子所高频高压中心刘新宇研究员/郑旭强研究员团队提出了一种新型基于环形振荡器的注入锁定时钟倍频器。团队提出了宽脉冲注入和传统窄脉冲注入相结合的互补注入方案,有效消除了窄脉冲注入引入的固有相位误差,同时增强了相位噪声抑制能力;设计了脉宽自适应注入脉冲产生威廉希尔官方网站 ,实现不同PVT下的最佳噪声抑制;开发了基于失锁检测和环路选择的频率追踪环路,扩展了频率锁定范围。该注入锁定振荡器被集成到高速有线收发机,实现了112Gb/s PAM4调制数据传输。

研究成果以“A Low-Jitter and Low-Reference-SpurRing-VCO-Based Injection-Locked Clock Multiplier Utilizing aComplementary-Injection Scheme and an Adaptive Pulsewidth Adjustment”为题发表在集成威廉希尔官方网站 设计领域顶级期刊Journal of Solid-State Circuits(JSSC)上,微电子所研究生王则栋为第一作者,微电子所郑旭强研究员为通讯作者。该项研究得到了国家重点研发计划和国家自然科学基金的支持。

论文链接:https://ieeexplore.ieee.org/document/10742924

图1. 提出的基于环形振荡器的注入锁定时钟倍频器

图2. (a)芯片照片及各模块功耗;(b)RMS抖动随电源电压变化图;(c)RMS抖动随VCO控制电压变化图

-

倍频器的技术原理和应用场景2024-11-29 0

-

微电子所在阻变存储器研究中取得新进展2010-12-29 0

-

方波倍频器2009-04-11 1515

-

高速数字倍频器2009-04-11 953

-

数控倍频器2009-04-11 708

-

数字倍频器2009-04-11 1523

-

变容管/阶跃管倍频器,倍频器工作原理2010-03-05 3192

-

微电子所在阻变存储器微观机制研究中取得系列进展2012-04-13 1310

-

键盘设定时钟的电子钟设计2016-07-04 596

-

6_25Gb_s快速锁定时钟数据恢复威廉希尔官方网站 _钟威2017-01-08 559

-

微电子所在SiC MOSFET器件研制方面的进展2017-11-08 1144

-

三张图了解微电子所在SiC MOSFET器件研制方面取得重要进展2018-04-20 2210

-

倍频器分类2019-01-08 6752

-

微电子所在2019VLSI国际研讨会上展示最新研究进展2019-06-26 4873

-

中科院微电子所:在表面等离激元光纤生化传感器方面取得重要进展2023-06-02 1126

全部0条评论

快来发表一下你的评论吧 !