人眼仿生学原理设计一种嵌入式的微型3D图像传感器

电子说

描述

针对现有3D拍摄设备体积庞大、价格昂贵等问题,利用FPGA高速并行处理能力与图像传感器,设计了微型嵌入式3D图像传感器。通过FPGA同步设置,采集双CMOS图像传感器图像数据,传输至SDRAM进行缓存并按行像素合并后,将左右立体对图像储

裸眼3D技术是《“十三五”国家战略性新兴产业发展规划》中指出的重点发展领域,规划表明了加快虚拟现实、增强现实、全息成像、裸眼三维图形显示(裸眼3D)等核心技术创新发展[1]的决心。影视拍摄的3D摄像机体积庞大、结构复杂且价格昂贵,不适合嵌入式系统的应用,严重制约了裸眼3D技术的产业化应用。而便携式产品、电视机的CPU不具备同步采集3D图像的接口和能力,因此图像3D传感器只能使用FPGA或CPLD器件来高速并行处理图像数据[2]。

本文根据人眼仿生学原理设计一种嵌入式的微型3D图像传感器,研究硬件逻辑方法以实现3D图像的采集、传输、存储及显示,为便携式领域提供获取3D图像数据的手段,力求解决裸眼3D技术产品化面对的技术瓶颈问题。

01系统设计思想

根据立体视觉原理,3D图像应同步采集并满足成像清晰度、光轴会聚、视差匹配等要求。

3D图像传感器系统结构包含两只CMOS型图像传感器及缓存图像数据的SDRAM,为了对两只图像传感器进行同步配置和采集,只能选用FPGA(或CPLD)作为逻辑控制芯片。

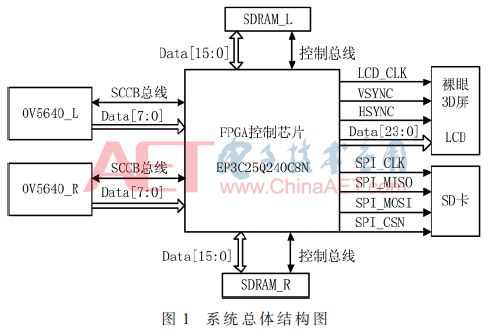

系统总体结构图如图1所示,采用FPGA+双CMOS+双SDRAM硬件结构。FPGA选用Altera公司的EP3C25Q240C8N为主控芯片;为满足图像传感器分辨率的要求,CMOS图像传感器采用500万像素的OV5640;FPGA对OV5640获取的图像数据进行采集并缓存至SDRAM,其容量应满足一帧高清晰度图像数据的存储要求。3D图像传感器的图像拍摄和视频录制方法的指导思想为把同步采集的两只OV5640的图像数据按行像素进行合并,以左右格式的全宽或半宽立体对图像储存至SD卡中。使用裸眼3D液晶屏作为实时监控设备,FPGA逻辑控制左右图像的像素重配后,再输入至裸眼3D显示屏显示。

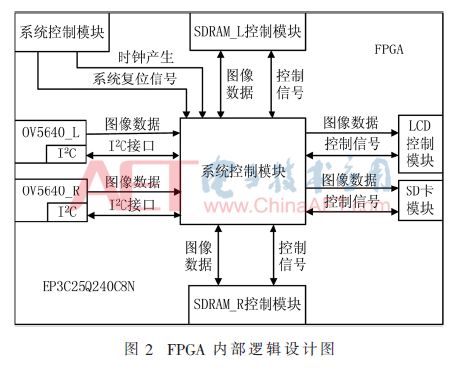

由于FPGA并不是CPU结构,而是一个可定制的能实现复杂逻辑威廉希尔官方网站 的器件,因此需要为所连接的器件设计逻辑控制模块。根据3D图像传感器的功能要求,按照图像数据的流向,FPGA的内部逻辑设计应包括图像采集模块、SDRAM缓存控制模块、SD卡储存模块、裸眼3D LCD显示控制模块及系统控制模块。

OV5640工作时钟为24 MHz,FPGA外部时钟为50 MHz,SDRAM工作时钟为100 MHz,LCD的工作时钟为25 MHz,所以系统控制模块需解决跨时钟域数据通信的问题。FPGA内部逻辑设计如图2所示。

02图像数据采集与缓存方法

3D拍摄时,如果两只图像传感器未有效同步,则运动物体的曝光成像就会存在时间差,其后果是左右眼图像不同步,从而使3D视觉无法形成而导致显示失败。因此3D图像传感器必须保证像素级的同步,使用FPGA的硬件逻辑控制来完成图像传感器准确的同步配置和同步采集。

2.1 图像传感器同步配置及其数据采集

通过SCCB(串行摄像机控制总线)对OV5640的工作寄存器进行配置[3],本文把图像传感器的图像输出数据设置为RGB565,再根据图像监控设备的分辨率1 024×768和800×600,把左右眼图像传感器的分辨率按半宽原则设置为512×768和400×600,帧频为30 f/s,以此来验证FPGA的逻辑算法是否正确。

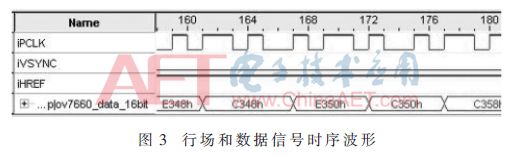

OV5640初始化完成后,图像传感器开始启动工作,按设置的帧频从数据接口输出图像数据。FPGA在PCLK(像素时钟)、HREF(行同步信号)和VSYNC(场同步信号)的控制下开始采集OV5640的图像数据Data[7..0],设计逻辑算法将采集到的相邻的两个字节数据转换为16位的图像数据。使用Signal-tapII在线采集行场信号与数据信号的时序波形如图3所示,当PCLK处于上升沿时检测行场信号,VSYNC处于低电平且HREF为高电平时表示正在采集图像数据,当VSYNC信号由低电平转高电平时,表示开始采集新的一帧图像数据。观察图3波形可知,设计的图像传感器数据采集的逻辑算法正确。

2.2 图像数据缓存

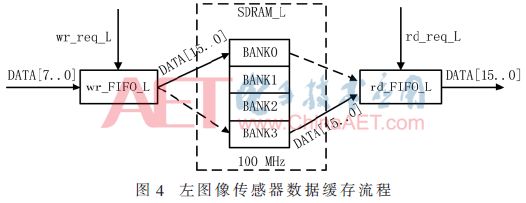

为解决跨时钟域数据通信问题,FPGA内部构建了wr_FIFO和rd_FIFO连接OV5640和SDRAM,wr_FIFO用于接收OV5640采集的图像数据,rd_FIFO用于缓存输出至LCD的图像数据。当wr_FIFO接收到wr_req(写数据请求)时,OV5640采集到的数据缓存至wr_FIFO中;当rd_FIFO接收到rd_req(读数据请求)时,rd_FIFO将缓存的数据输出至LCD显示。

由于3D视频图像数据量大、传输速度高、像素级同步的要求,为了保证数据的有效处理,设计了SDRAM控制模块,运用了轮序法对SDRAM进行分时操作[4]。当SDRAM进行写操作时,数据首先写入BANK0,写完一帧图像数据后,切换为BANK3;当SDRAM进行读操作时采用相同逻辑,切换BANK。根据以上逻辑,将轮序法操作SDRAM算法封装成SDRAM控制器,使得图像数据在SDRAM中的缓存更为简化和高效。左图像传感器的数据缓存操作流程如图4所示。

03图像储存

SD卡具有尺寸小、功耗低、读取速度快等优点,所以在便携式储存领域应用广泛[5]。SPI以主从方式工作,系统采用SPI模式实现SD卡与FPGA的通信,由SPI_CLK(时钟信号)、SPI_MISO(主机输入从机输出)、SPI_MOSI(主机输出从机输入)、SPI_CSN(片选信号)组成。

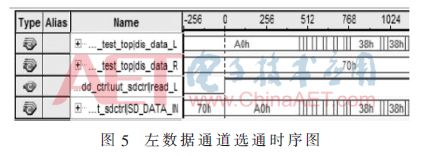

分辨率为2 048×768的左右立体对图像以BMP格式储存在SD卡中,分为三个过程:立体对图像数据转化为BMP图像数据格式;SD卡初始化;SD卡写操作控制[6]。3D图像传感器采集的图像数据为RGB565,SD卡则以真彩色RGB888格式进行储存,所以需RGB565转RGB888操作,有两种方案选择,一是采取低位补零方法,二是RGB565数据向高位移位后低位补原数据的高位,系统对两个方案都进行了实验,观看效果一致。SD卡的初始化按照SD卡的初始化流程实现。采用FAT16文件系统对SD卡进行扇区管理,以便立体对图像数据的正确写入,使用Verilog_HDL(硬件描述语言)将FAT表、根目录及54 B的BMP文件信息写入SD卡对应的物理地址。在左右数据通道的控制下,将左右图像数据写入SD卡的数据区,左数据通道选通时序图如图5所示,右数据通道选通时序关系同理。

04图像显示

采用8英寸裸眼3D显示屏对采集到的图像进行显示,该裸眼3D显示屏能兼容2D和3D显示,所以分别设计了左右立体对显示和像素重配后的3D显示两种逻辑算法。系统采用LCD的驱动模式为DE模式,DE信号相当于行场两个同步信号的复合信号,通过h_cnt和v_cnt两个计数器控制DE_h和DE_v两个同步信号,逻辑为DE=DE_h&DE_v,当DE为高电平时,LCD显示接收到的图像数据。

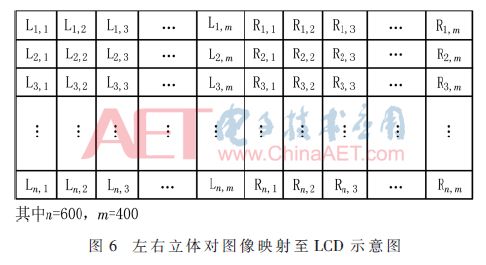

2D显示时,将具有一定视差的左右立体对图像映射至LCD,根据时序标准,切换左、右数据选通信号,使得左、右图像数据按行传输至LCD上显示。硬件上设计了VGA接口和LCD接口,分别将立体对图像映射至液晶电视和LCD上显示,两者映射原理相同,只是时序不同,左右立体对图像映射至LCD的示意图如图6所示。

3D显示时,将左、右图像数据分别映射至裸眼3D显示屏左、右眼亚屏幕[7],即左图像数据映射在屏幕的奇列像素上,右图像数据映射在屏幕的偶列像素上,将左右图像数据进行行压缩逻辑设计,按照时钟频率交替写入LCD中,完成像素重配。裸眼3D显示屏在结构上和普通2D显示屏有很大的不同,观看角度上也存在差异。当人眼处于独立视区时,左右眼能独立地看到左右亚屏幕上的图像,通过大脑视觉中枢融合形成裸眼3D效果[8]。当人眼处于非独立视区时,左右眼分别能看到左右亚屏幕上的图像,此时形成重影而影响观看效果。左右立体对图像像素重配后映射至LCD的示意图如图7所示。

05仿真分析及实验

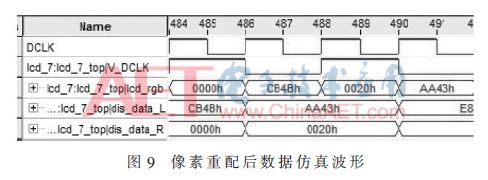

OV5640采集8 bit的图像数据在SDRAM缓存过程中需转换为RGB565格式的16 bit数据,使用嵌入式逻辑分析仪Signal-tapII对该转换进行仿真分析,仿真波形如图8所示,通过观察信号的值可验证该逻辑设计正确。对像素重配后在裸眼3D屏上显示的图像数据进行仿真分析,其波形如图9所示,通过在线仿真可看出3D显示时的图像数据和左右图像传感器获取的图像数据严格一致。

系统使用了液晶电视和裸眼3D显示屏进行了实验,准确稳定地将采集到的高清立体对图像输入并显示。3D图像传感器将立体对图像像素重配后输入至裸眼3D显示屏显示,效果良好。实验结果表明,设计的3D图像传感器及其逻辑算法能对3D图像进行完整的采集、传输、储存、显示,验证了系统硬件逻辑算法的正确性。

06结 论

便携式3D拍摄设备具有广阔的发展前景,根据人眼立体视觉仿生原理设计的3D图像传感器利用了FPGA高速并行处理的优势,使得硬件构架上更为集成化,解决了3D视频图像来源、储存和像素重配等问题。系统工作稳定,移植性好,通过修改模块程序即可支持不同的图像传感器和显示器,支持2D和3D显示,具有较好的兼容性。

3D图像传感器提供了3D图像获取的手段,使用者可随时随地记录3D场景,可在裸眼3D设备上复现三维场景,获得临场感和沉浸感。3D图像传感器的研制为3D图像传感器的专用集成威廉希尔官方网站 设计提供了有益的参考。

-

仿生传感器有什么特点?2019-08-19 0

-

3D传感器如何为车内安全保驾护航?2020-07-29 0

-

3D传感器有哪些类型2020-12-09 0

-

嵌入式3D视觉功能相关资料推荐2021-12-23 0

-

嵌入式3D有何功能呢2021-12-23 0

-

构件化嵌入式3D引擎的研究与设计2009-05-30 623

-

嵌入式应用系统中3D鼠标的应用2009-06-18 449

-

基于WindowsCENET的嵌入式视觉传感器系统的研究2016-04-18 872

-

基于人眼视觉特性的的嵌入式零树图像编码改进算法_刘敬2017-03-16 773

-

走进3D视觉系列(六):新兴应用驱动下的图像传感器2018-08-21 649

-

关于3D图像传感器的性能分析和应用2019-09-24 2998

-

一种微型传感器,可以在一美分硬币的一面安装3万个2020-05-19 3661

-

电化学仿生眼:世界上首个3D人工眼2020-06-23 5171

-

ToF 3D图像传感器的特性介绍2021-09-01 1472

-

用于3D扫描的嵌入式图像预处理2022-11-07 287

全部0条评论

快来发表一下你的评论吧 !