ADCLK854 1.8 V、12 LVDS/24 CMOS输出的低功耗时钟扇出缓冲器技术手册

描述

概述

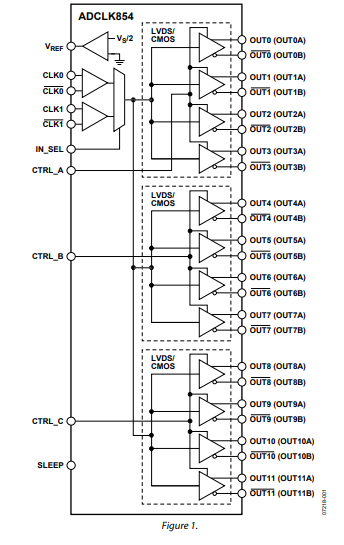

ADCLK854是一款1.2 GHz/250 MHz LVDS/CMOS扇出缓冲器,针对低抖动、低功耗应用进行了优化。其配置范围为12 LVDS至24 CMOS输出,包括LVDS和CMOS输出组合。三条控制线用于确定固定输出块(3/4组)为LVDS输出还是CMOS输出。

ADCLK854提供两路可选输入和休眠模式特性。IN_SEL引脚状态确定被扇出至所有输出的输入。SLEEP引脚可使能休眠模式,以关断器件。

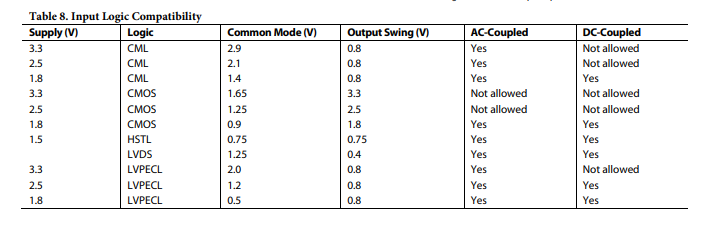

包括LVPECL、LVDS、HSTL、CML、CMOS在内的各种单端和差分逻辑电平均可作为输入。表8列出了各类连接的接口选项。

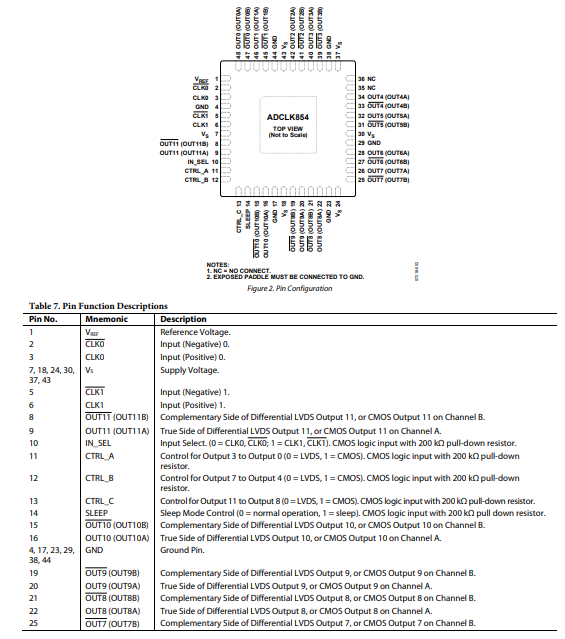

该器件采用48引脚LFCSP封装,额定工作温度范围为−40°C至+85°C(标准工业温度范围)。

数据表:*附件:ADCLK854 1.8 V、12 LVDS 24 CMOS输出的低功耗时钟扇出缓冲器技术手.pdf

应用

- 低抖动时钟分配

- 时钟与数据信号恢复

- 电平转换

- 无线通信

- 有线通信

- 医疗和工业成像

- 自动测试设备(ATE)和高性能仪器仪表

特性

- 2个可选差分输入

- LVDS/CMOS可选输出

- 多达12 LVDS(1.2 GHz)或者24 CMOS(250 MHz)的输出

- 每通道功耗:<12 mW(工作频率为100 MHz)

- 综合抖动:54 fs(12 kHz至20 MHz)

- 附加宽带抖动:100 fs

- 传播延迟:2.0 ns(LVDS)

- 输出上升/下降时间:135 ps(LVDS)

- 输出至输出偏斜:70 ps(LVDS)

- 睡眠模式

- 引脚可编程控制

- 1.8 V电源

框图

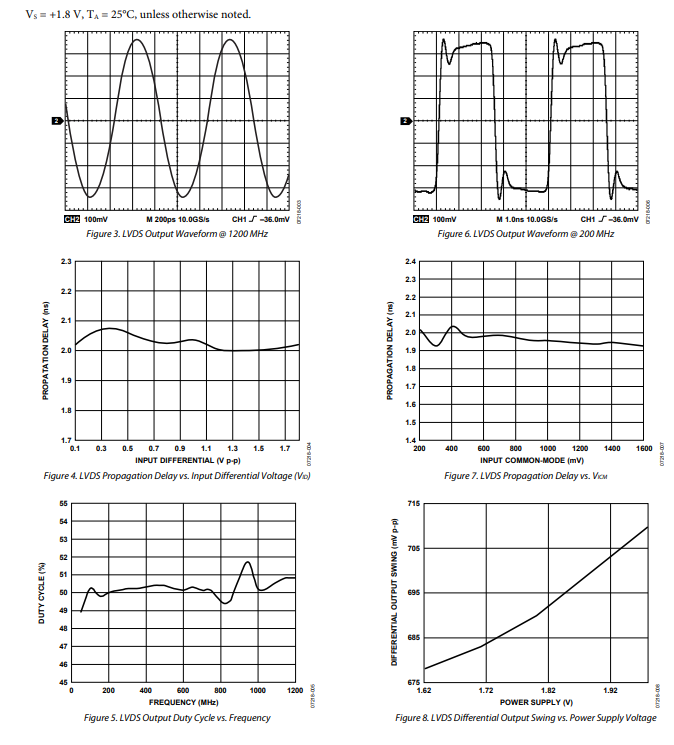

引脚配置描述

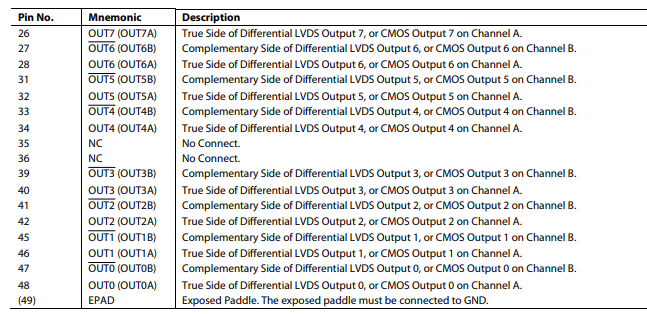

典型性能特征

功能描述

时钟输入

ADCLK854从两个输入中的一个接收时钟输入,并将选定的时钟分配到所有输出通道。输出分为三组,每组三个输出,并且可以设置为LVDS或CMOS电平。这允许从使用LVDS的12种到使用CMOS输出的24种多种逻辑配置中进行选择,以及使用这两种逻辑的其他组合。

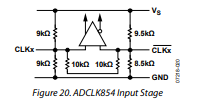

ADCLK854的差分输入在内部进行自偏置。时钟输入有一个电阻分压器,用于设置输入的共模电平。互补输入的偏置比真值低约30 mV,以避免在输入信号停止时出现振荡。等效输入威廉希尔官方网站 见图20。

输入可以是交流耦合或直流耦合。表8提供了输入逻辑兼容性的参考。如果需要单端输入,可以通过交流或直流耦合到差分输入的一侧来实现;将另一个输入通过电容旁路到地。

交流耦合输入应用

ADCLK854为交流耦合提供两种选择。第一种选择不需要外部组件(不包括隔直电容),它允许用户将参考信号耦合到时钟输入引脚。更多信息见图29。

第二种选择允许使用**V_{REF}引脚为ADCLK854设置直流偏置电平。V_{REF}引脚可以通过电阻连接到CLK和overline{CLK}。这种方法允许在ADCLK854处对信号进行较低阻抗的端接(更多信息见图32)。内部偏置电阻与外部偏置电阻保持并联。然而,内部电阻的相对高阻抗使得外部到V_{REF}**的端接起主导作用。当像前面提到的那样,不希望仅使用内部偏置来偏移输入时,这种方法也很有用。

时钟输出

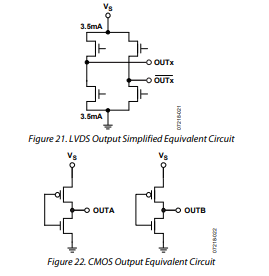

每个驱动器由一个差分LVDS输出或两个单端CMOS输出组成(始终同相)。当LVDS驱动器启用时,相应的CMOS驱动器处于三态;当CMOS驱动器启用时,相应的LVDS驱动器断电并处于三态。图21和图22展示了等效输出级。

-

ADCLK846/PCBZ,ADCLK954高性能时钟扇出缓冲器评估板2019-02-21 0

-

ADCLK854,pdf datasheet (Low Po2009-09-15 592

-

1.8伏6LVDS/12 CMOS输出低功耗时钟扇出缓冲器adclk846数据表2017-10-20 966

-

1.8V,12-lvds/24-cmos输出低功耗时钟扇出缓冲器adclk854数据表2017-10-20 1178

-

ADCLK846 1.8 V、6 LVDS/12 CMOS输出低功耗时钟扇出缓冲器2019-02-22 600

-

ADCLK854 1.8 V、12 LVDS/24 CMOS输出的低功耗时钟扇出缓冲器2019-02-22 506

-

ADCLK854: 1.8 V, 12-LVDS/24-CMOS Output, Low Power Clock Fanout Buffer Data Sheet2021-01-28 613

-

ADCLK846:1.8 V、6 LVDS/12 CMOS输出低功耗时钟扇出缓冲器2021-03-20 796

-

ADCLK946:六路LVPECL输出,SiGe时钟扇出缓冲器数据表2021-04-19 1219

-

ADCLK954:两个可选输入、12个LVPECL输出、SiGe时钟扇出缓冲器数据表2021-04-25 949

-

EVAR-ADCH846 ADCLK846评估板2021-06-03 836

-

EVADCH854 ADCLK854评估板2021-06-06 801

-

ADCLK948 2路可选输入、8路LVPECL输出、SiGe时钟扇出缓冲器技术手册2025-04-11 553

-

ADCLK846 1.8 V、6 LVDS/12 CMOS输出低功耗时钟扇出缓冲器技术手册2025-04-11 653

-

ADCLK946采用SiGe工艺的6 LVPECL输出时钟扇出缓冲器技术手册2025-04-11 641

全部0条评论

快来发表一下你的评论吧 !