ADF4350集成VCO的宽带频率合成器技术手册

描述

概述

ADF4350结合外部环路滤波器和外部基准频率使用时,可实现小数N分频或整数N分频锁相环(PLL)频率合成器。

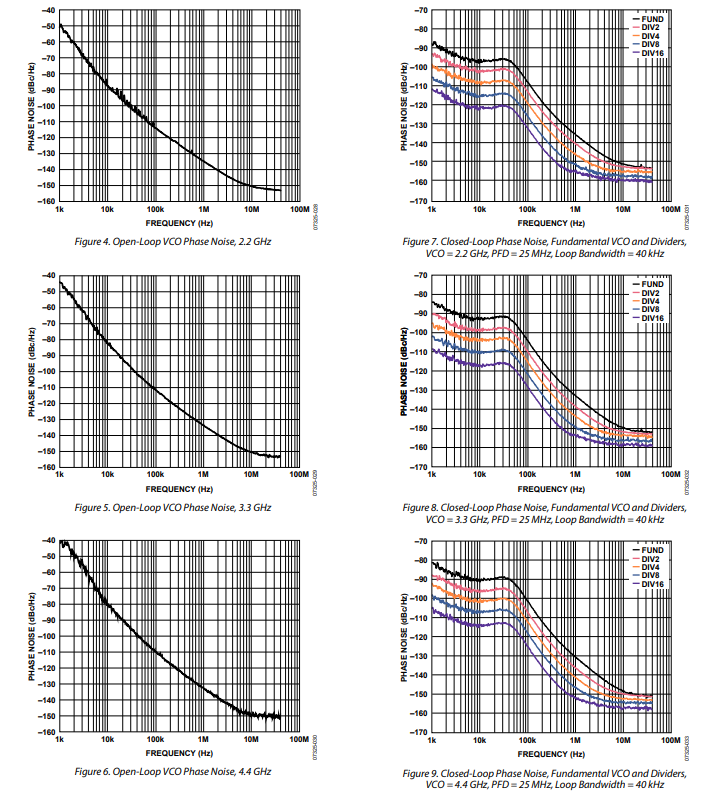

ADF4350具有一个集成电压控制振荡器(VCO),其基波输出频率范围为2200 MHz至4400 MHz。此外,利用1/2/4/8/16分频威廉希尔官方网站 ,用户可以产生低至137.5 MHz的RF输出频率。对于要求隔离的应用,RF输出级可以实现静音。静音功能既可以通过引脚控制,也可以通过软件控制。同时提供辅助RF输出,且不用时可以关断。

所有片内寄存器均通过简单的三线式接口进行控制。该器件采用3.0 V至3.6 V电源供电,不用时可以关断。

数据表:*附件:ADF4350集成VCO的宽带频率合成器技术手册.pdf

应用

- 无线基础设施(W-CDMA、TD-SCDMA、WiMAX、GSM、PCS、DCS、DECT)

- 测试设备

- 无线局域网(LAN)、有线电视设备

- 时钟产生

特性

- 输出频率范围:137.5 MHz至4400 MHz

- 小数N分频频率合成器和整数N分频频率合成器

- 具有低相位噪声的VCO

- 可编程1/2/4/8/16分频输出

- 均方根(RMS)抖动:小于0.4 ps rms(典型值)

- 电源电压:3.0 V至3.6 V

- 逻辑兼容性:1.8 V

- 可编程双模预分频器:4/5或8/9

- 可编程的输出功率

- RF输出静音功能

- 三线式串行接口

- 模拟和数字锁定检测

- 在宽带宽内快速锁定模式

- 周跳减少

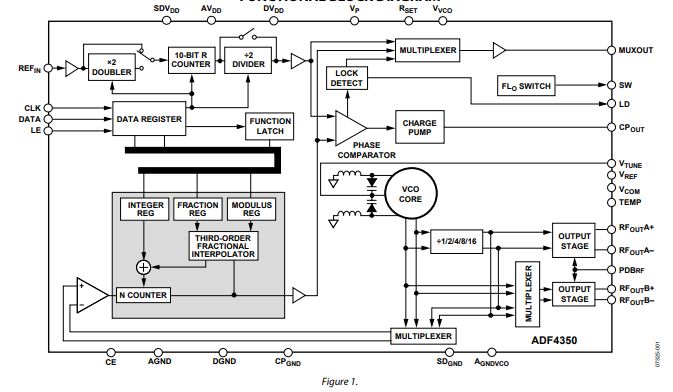

框图

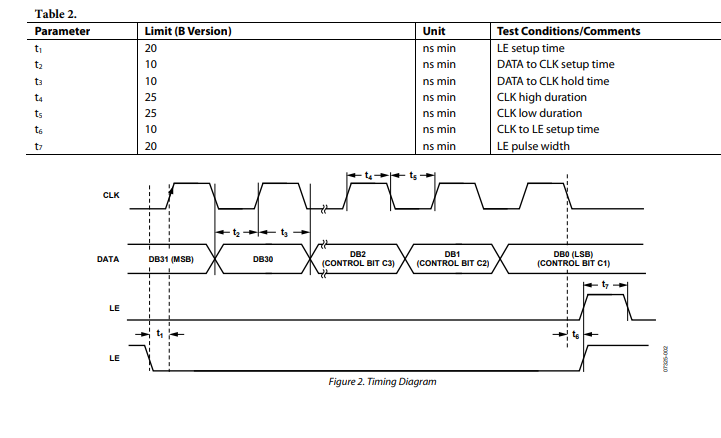

时序特征

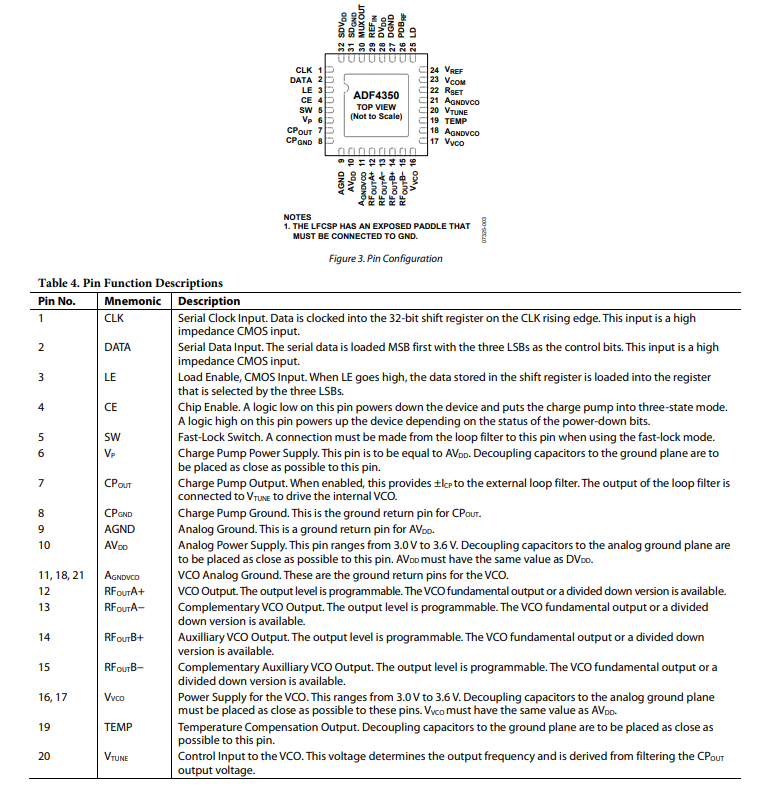

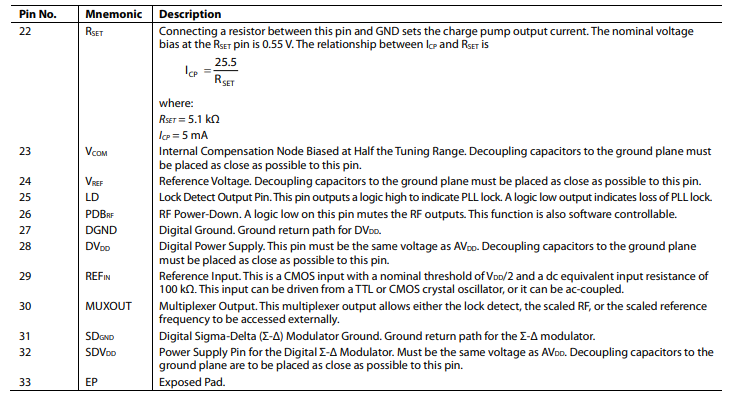

引脚配置描述

典型性能特征

威廉希尔官方网站 描述

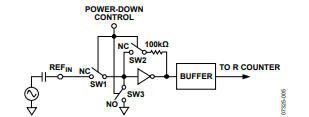

参考输入部分

参考输入级如图16所示。SW1和SW2通常为闭合开关,SW3通常为断开开关。当启动掉电模式时,SW3闭合,SW1和SW2断开。这确保了在掉电期间**REF_{IN}**引脚不会产生负载。

图16. 参考输入级

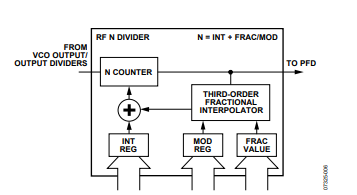

射频N分频器

射频N分频器可在锁相环(PLL)反馈路径中实现分频比。该分频比由INT、FRAC和MOD值决定。

图17. 射频整数分频器

INT、FRAC、MOD和R计数器关系

INT、FRAC和MOD值与R计数器配合,能够生成间隔为鉴频鉴相器(PFD)频率分数倍的输出频率。更多信息请参见“射频合成器——实例”部分。

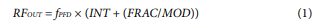

射频压控振荡器(VCO)频率(RF_{OUT})公式为:

其中:

- **RF_{OUT}**是外部压控振荡器(VCO)的输出频率。

- INT是16位二进制计数器的预设分频比(对于4/5预分频器,为23至32,767;对于8/9预分频器,为75至65,535 )。

- FRAC是分数除法的分子(0至MOD - 1)。

- MOD是预设分数模数(2至4095 )。

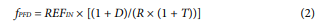

PFD频率(f_{PFD})公式为:

其中:

- **REF_{IN}**是参考输入频率。

- D是**REF_{IN}**倍频位(0或1)。

- R是10位二进制可编程参考计数器的预设分频比(1至1023 )。

- T是**REF_{IN}**二分频位(0或1 )。

整数N模式

如果FRAC = 0且寄存器2中的DB8(LDF)位设为1,合成器将在整数N模式下运行。寄存器2中的DB8(LDF)位应设为1,以实现整数N模式下的数字锁定检测。

R计数器

10位R计数器可对输入参考频率(REF_{IN})进行分频,以产生PFD的参考时钟。允许的分频比范围为1至1023。

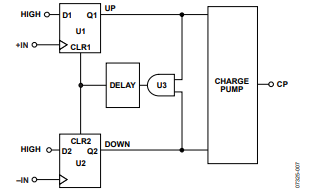

鉴频鉴相器(PFD)和电荷泵

鉴频鉴相器(PFD)对R计数器和N计数器进行计数,并输出与两个计数器之间的相位和频率差成比例的信号。图18是PFD的简化示意图。

图18. PFD简化示意图

PFD包含一个延迟元件,用于设置抗锯齿脉冲的宽度,该宽度通常为3ns 。此脉冲可确保PFD转换功能中不存在死区,并提供一致的参考杂散电平。

-

ADF5611集成VCO的微波宽带频率合成器技术手册2025-04-27 484

-

ADF5355集成VCO的微波宽带频率合成器技术手册2025-04-25 653

-

ADF5612集成VCO的微波宽带频率合成器技术手册2025-04-24 661

-

ADF4377 微波宽带合成器和集成VCO数据表 ADI2023-10-11 270

-

ADF4368:微波宽带合成器和集成VCO数据表 ADI2023-10-10 271

-

EVADF4350 ADF4350 评估板2021-06-03 742

-

CN0245 可与正交解调器实现简单接口的宽带LO PLL频率合成器2021-06-02 1025

-

CN0232 将集成VCO和外部PLL威廉希尔官方网站 的频率合成器杂散输出降至最低2021-05-28 1005

-

ADF4350 IIO宽带合成器Linux驱动程序2021-04-20 1163

-

ADF4350集成电压控制振荡器的性能与应用2019-06-13 3350

-

ADF4350 集成VCO的宽带频率合成器2019-02-22 866

-

基于ADF4350的多频段信号源的设计与实现2013-03-06 1990

-

集成低噪声VCO的ADF4350系列PLL之特性和应用2012-06-08 3279

-

ADF4350低相噪频率合成器在射频无线通信设备中的2011-03-20 1717

全部0条评论

快来发表一下你的评论吧 !