8086cpu由哪两部分组成_8086CPU内部结构图分享

cpu

描述

8086概述

Intel8086是一个由Intel于1978年所设计的16位微处理器芯片,是x86架构的鼻祖。不久之后,Intel就推出了Intel8088(一个拥有8根外部数据总线的微处理器)。它是以8080和8085的设计为基础,拥有类似的寄存器组,但是数据总线扩充为16位。总线界面单元(BusInterfaceUnit)透过6字节预存(prefecth)的队列(queue)位指令给执行单元(ExecutionUnit),所以取指令和执行是同步的,8086CPU有20条地址线,可直接寻址1MB的存储空间,每一个存储单元可以存放一个字节(8位)二进制信息。

8086微处理器的性能特点

16位的内部结构,16位双向数据信号线;

20位地址信号线,可寻址1M字节存储单元;

较强的指令系统;

利用第16位的地址总线来进行I/O端口寻址,可寻址64K个I/O端口;

中断功能强,可处理内部软件中断和外部中断,中断源可达256个;

单一的+5V电源,单相时钟5MHz。

8086cpu由哪两部分组成

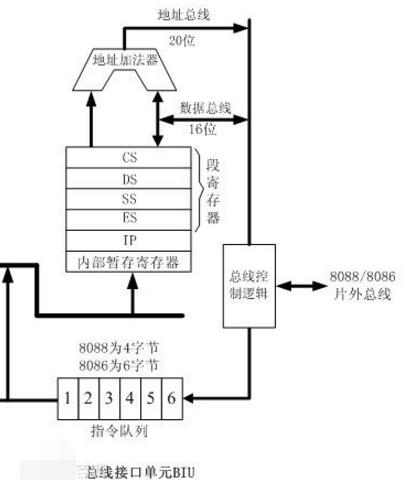

1、总线接口单元

总线接口部件由下列各部分组成

⑴4个段地址寄存器:

CS(codesegment)——16位的代码段寄存器;

DS(datasegment)——16位的数据段寄存器;

ES(extrasegment)——16位的扩展段寄存器;

SS(stacksegment)——16位的堆栈段寄存器;

⑵16位的指令指针寄存器IP;

⑶20位的地址加法器;

⑷6字节的指令队列缓冲器。

2、执行单元

执行部件由下列几个部分组成:

⑴8个通用寄存器:即AX、BX、CX、DX,BP,SP,SI,DI;

其中,4个数据寄存器:AX、BX、CX、DX;

2个地址指针寄存器:BP(basepointer),SP(stackpointer);

2个变址寄存器:SI(sourceindex),DI(destinationindex);

⑵标志寄存器FR(flagsregister);

⑶算术逻辑单元ALU(arithmeticlogicunit)。

EU负责全部指令的执行,同时向BIU输出数据(操作结果),并对寄存器和标志寄存器进行管理。在ALU中进行16位运算,数据传送和处理均在EU控制下执行。

8086cpu结构图

8086CPU内部结构图分享

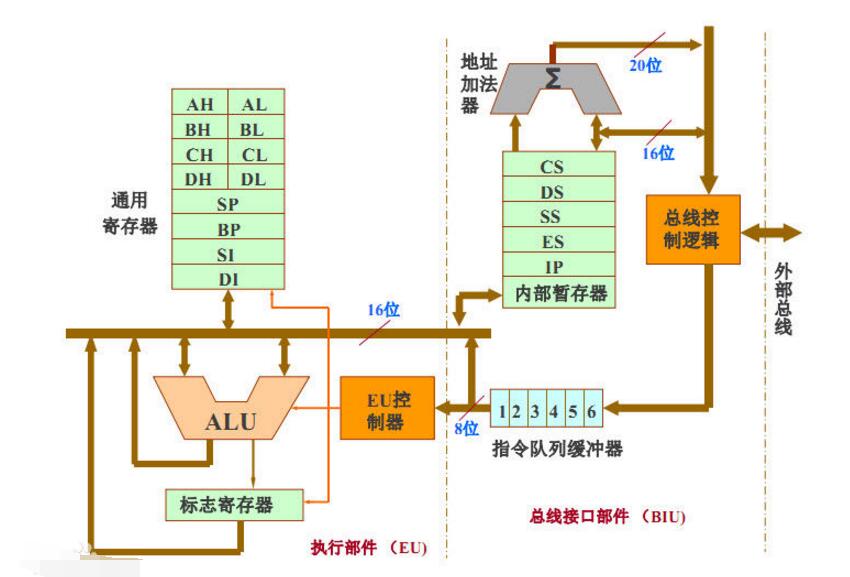

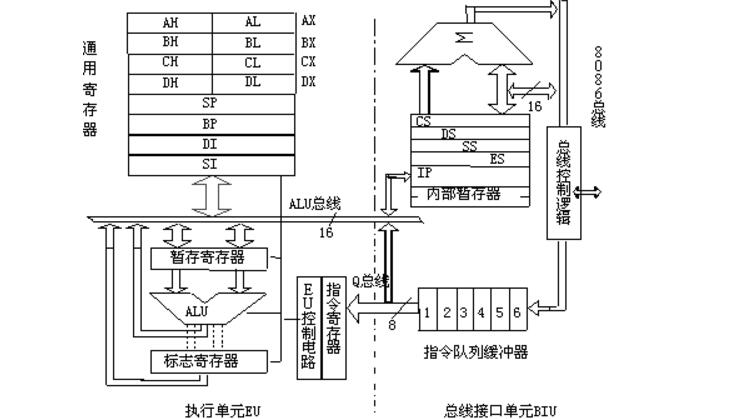

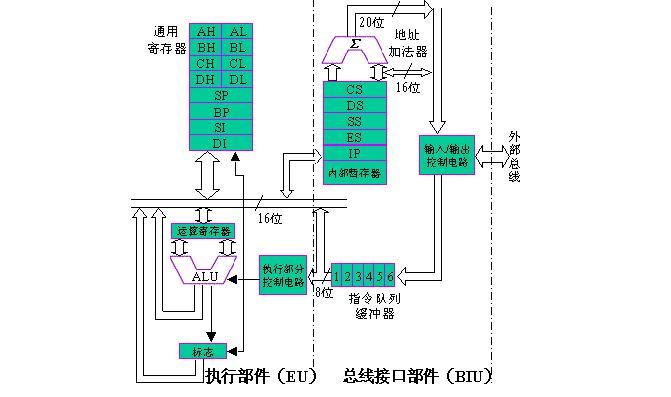

如图,8086CPU从功能上划分成两部分:总线接口单元BIU(BusInterfaceUnit)和执行单元EU(ExecutionUnit)。

EU的组成部分:16位通用寄存器组(AX,BX,CX,DX,SP,BP,SI,DI)、算术逻辑单元(ALU)、标志寄存器(FLAG)、操作控制器威廉希尔官方网站 。

BIU的组成部分:段寄存器组(CS,DS,SS,ES)、指令指针(IP)、地址加法器、指令队列缓冲器、总线接口控制逻辑。

执行单元的功能:

指令译码

指令执行————————-在ALU中完成

暂存中间运算结果—————-通用寄存器

保存运算结果特征—————-标志寄存器flags

总线接口单元的功能:

从内存中取指令到指令预取队列

负责与内存或输入/输出接口之间的数据传送

在执行转移程序时,BIU使指令预取队列复位,从指定的新地址取指令,并立即传给执行单元执行。

8086工作原理图

8086CPU的两种工作模式

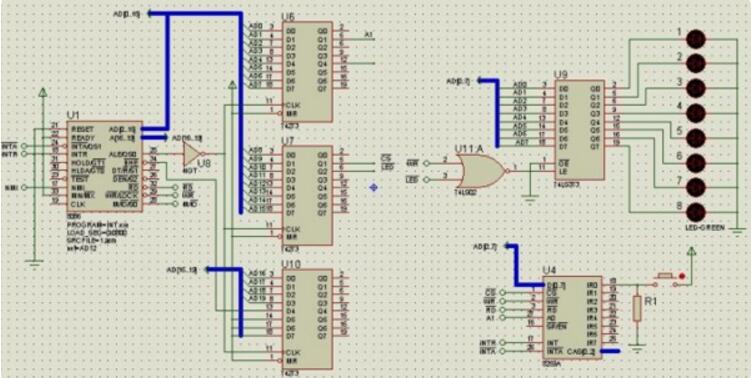

为了适应各种使用场合,在设计8086CPU芯片时,就考虑了其应能够使它工作在两种模式下,即最小模式与最大模式。

所谓最小模式,就是系统中只有一个8086微处理器,在这种情况下,所有的总线控制信号,都是直接由8086CPU产生的,系统中的总线控制逻辑威廉希尔官方网站 被减到最少,该模式适用于规模较小的微机应用系统。

最大模式是相对于最小模式而言的,最大模式用在中、大规模的微机应用系统中,在

最大模式下,系统中至少包含两个微处理器,其中一个为主处理器,即8086/8086CPU,其它的微处理器称之为协处理器,它们是协助主处理器工作的。

与8086CPU配合工作的协处理器有两类,一类是数值协处理器8087另一类是输入/输出协处理器8089。

8087是一种专用于数值运算的协处理器,它能实现多种类型的数值运算,如高精度的整型和浮点型数值运算,超越函数(三角函数、对数函数)的计算等,这些运算若用软件的方法来实现,将耗费大量的机器时间。换句话说,引入了8087协处理器,就是把软件功能硬件化,可以大大提高主处理器的运行速度。

8089协处理器,在原理上有点象带有两个DMA通道的处理器,它有一套专门用于输入/输出操作的指令系统,但是8089又和DMA控制器不同,它可以直接为输入/输出设备服务,使主处理器不再承担这类工作。所以,在系统中增加8089协处理器之后,会明显提高主处理器的效率,尤其是在输入/输出操作比较频繁的系统中。

8086的存储器组织

1.存储容量

8086有20根地址总线,因此,它可以直接寻址的存储器单元数为220=1Mbyte

2.物理地址

8086可直接寻址1Mbyte的存储空间,其地址区域为00000H—FFFFFH,与存储单元一一对应的20位地址,我们称之为存储单元的物理地址。

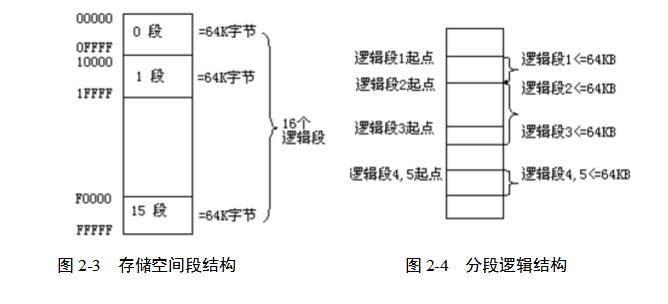

3.存储器的分段及段地址

由于CPU内部的寄存器都是16位的,为了能够提供20位的物理地址,系统中采用了存储器分段的方法。规定存储器的一个段为64KB,由段寄存器来确定存储单元的段地址,由指令提供该单元相对于相应段起始地址的16位偏移量。

这样,系统的整个存储空间可分为16个互不重叠的逻辑段,如图2-3所示。存储器的每个段的容量为64KB,并允许在整个存储空间内浮动,即段与段之间可以部分重叠、完全重叠、连续排列,非常灵活,如图2-4所示。

4.偏移地址

偏移地址是某存储单元相对其所在段起始位臵的偏移字节数,或简称偏移量。它是一个16位的地址,根据指令的不同,它可以来自于CPU中不同的16位寄存器(IP、SP、BP、SI、DI、BX等)。

5.物理地址的形成

物理地址是由段地址与偏移地址共同决定的,段地址来自于段寄存器(CS、DS、ES、SS),是十六位地址,由段地址及偏移地址计算物理地址的表达式如下:

物理地址=段地址×16+偏移地址

例如:系统启动后,指令的物理地址由CS的内容与IP的内容共同决定,由于系统启动的CS=0FFFFH,IP=0000H,所以初始指令的物理地址为0FFFF0H,我们可以在0FFFF0H单元开始的几个单元中,固化一条无条件转移指令的代码,即转移到系统初始化程序部分。

6.存储器分段组织带来存储器管理的新特点

首先,在程序代码量、数据量不是太大的情况下,可使它们处于同一段内,即使它们在64Kbyte的范围内,这样可以减少指令的长度,提高指令运行的速度;

其次,内存分段为程序的浮动分配创造了条件;

第三,物理地址与形式地址并不是一一对应的,举例:6832H:1280H,物理地址为695A0H。

第四,各个分段之间可以重叠

7.特殊的内存区域

8088/8086系统中,有些内存区域的作用是固定的,用户不能随便使用,如:中断矢量区:00000H—003FFH共1K字节,用以存放256种中断类型的中断矢量,每个中断矢量占用4个字节,共256×4=1024=1K

显示缓冲区:B0000H—B0F9FH约4000(25×80×2)字节,是单色显示器的显示缓冲区,存放文本方式下,所显示字符的ASCII码及属性码;B8000H—BBF3FH约16K字节,是彩色显示器的显示缓冲区,存放图形方式下,屏幕显示象素的代码。

启动区:FFFF0H—FFFFFH共16个单元,用以存放一条无条件转移指令的代码,转移到系统的初始化部分。

-

小白求助~~请问,8086CPU能装载exe文件吗?2013-12-25 0

-

8086cpu是16位的,内存单元只有8位怎么写进去?2019-03-12 0

-

求大佬分享关于8086CPU汇编指令速查手册2021-04-12 0

-

8086cpu引脚口诀相关资料推荐2021-05-25 0

-

8086cpu工作原理2021-07-22 0

-

计算机由哪几部分组成2021-07-29 0

-

为什么说8086是16位处理器2021-08-06 0

-

8086微机内部结构由什么组成2022-01-25 0

-

微处理器的外部结构是怎样构成的2022-02-14 0

-

8086CPU设计微机最小系统.ppt2006-06-29 3175

-

8086CPU 汇编指令速查手册2010-10-17 4422

-

8086CPU中文资料汇总(8086引脚图及功能_工作原理及应用威廉希尔官方网站 )2018-04-16 69497

-

8086CPU有哪些寄存器_各有什么用途2018-04-16 74216

-

8086CPU引脚图及功能_8086CPU组成部分2018-04-16 69695

-

微机原理02--8086结构2021-12-09 685

全部0条评论

快来发表一下你的评论吧 !