ltc6803中文资料(ltc6803引脚及功能_特性参数及典型应用威廉希尔官方网站 图)

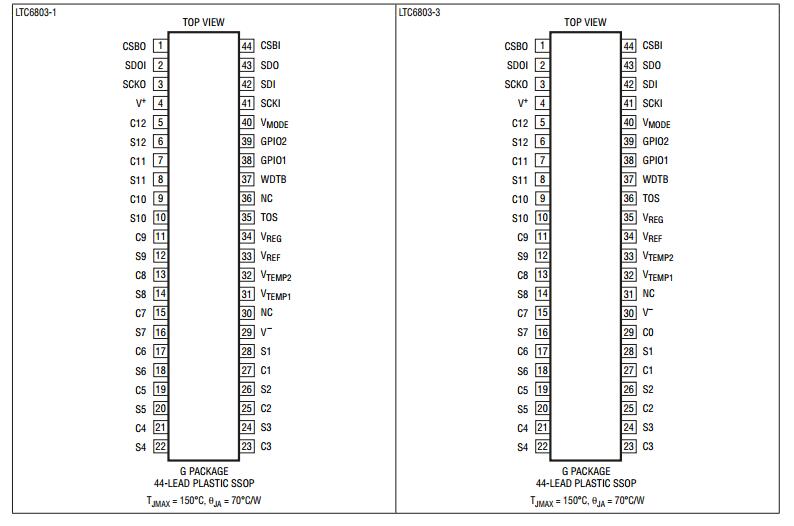

芯片引脚图

描述

ltc6803概述

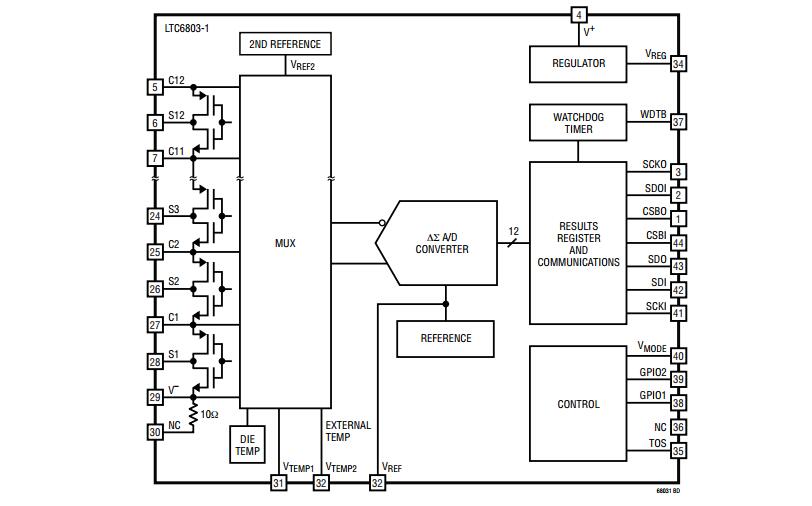

LTC6803是一款第二代高压电池监视器。2011年2月22日–凌力尔特公司(Linear Technology Corporation) 推出第二代高压电池监视器LTC®6803,该器件面向混合动力/电动汽车(HEV)、电动汽车(EV)以及其他高压、高性能电池系统。LTC6803是一款完整的电池测量IC,包含一个12位ADC、一个精确的电压基准、一个高压输入多路复用器和一个串行接口。每个LTC6803都能测量多达12个串联连接的独立电池单元。该器件的专有设计使多个LTC6803能串联叠置,而无需光耦合器或隔离器,从而允许对长串串联连接电池中的每一节电池进行精确的电压监视。

LTC6803芯片特点

可测量多达12 个串联电池的电压

可堆叠式架构

可支持多种电池化学组成和超级电容器

至相邻器件的串行接口菊式链接

0.25% 的最大总测量误差

专门针对符合ISO26262 标准的系统进行设计

可在 13ms 完成一个系统中所有电池的测量

无源电量平衡:

― 集成型电量平衡 MOSFET

― 能够驱动外部平衡 MOSFET

板上温度传感器和热敏电阻输入

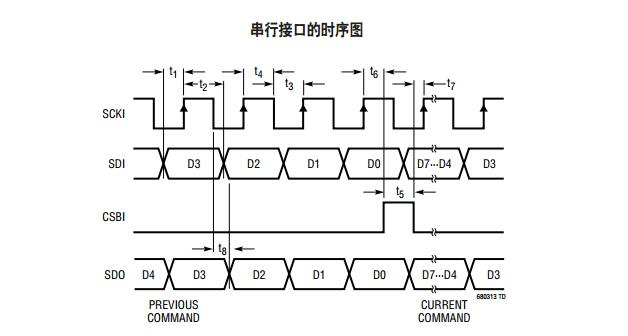

具数据包误差检验功能的 1MHz 串行接口

可在电池随机连接的情况下保持安全

内置自测试功能威廉希尔官方网站

具内置噪声滤波器的 ΔΣ 转换器

导线开路连接故障检测

12μA 待机模式电源电流

抗 EMI 的能力高

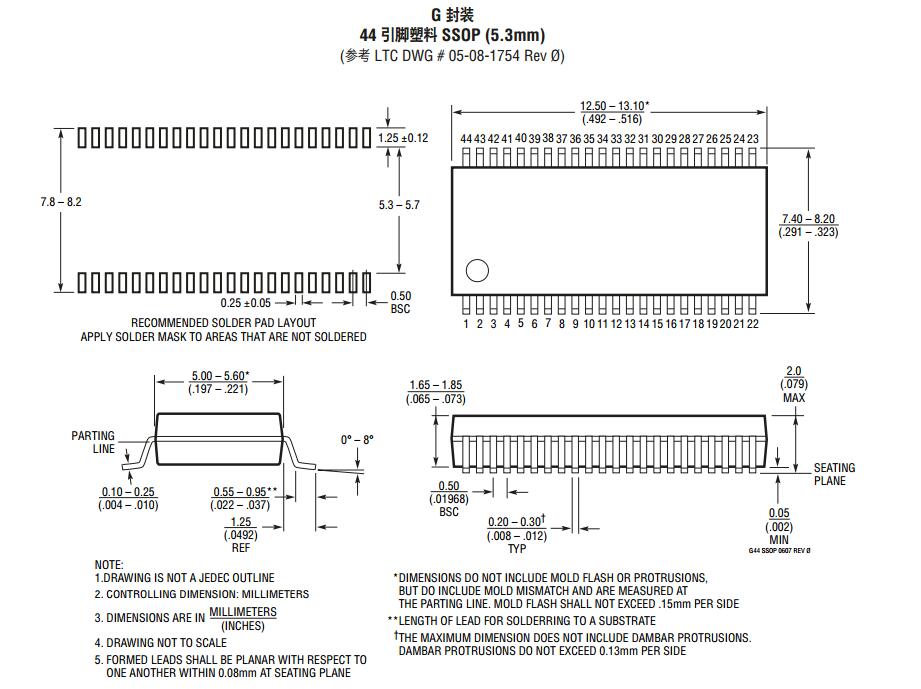

44 引脚 SSOP 封装

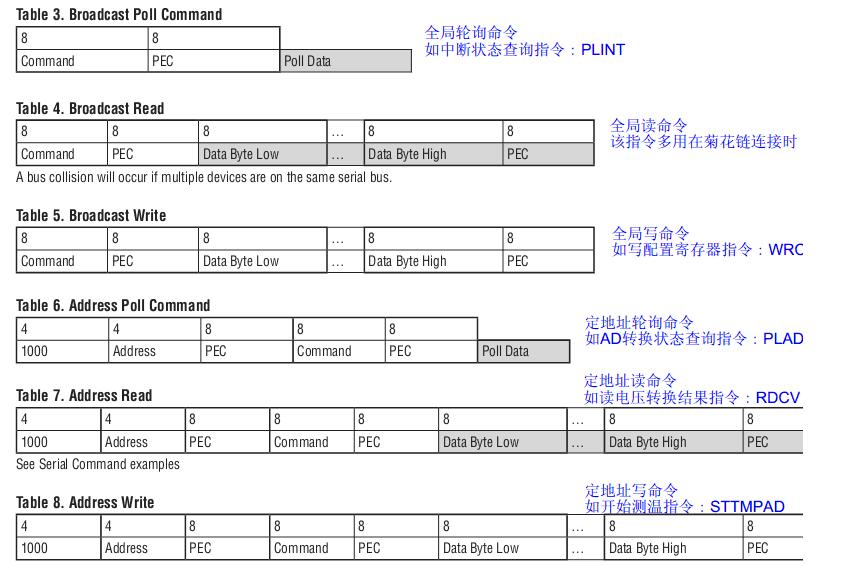

LTC6803的命令格式

LTC6803的应用领域

电动汽车和油电混合动力汽车

高功率便携式设备

后备电池系统

电动自行车、摩托车、单脚滑行车

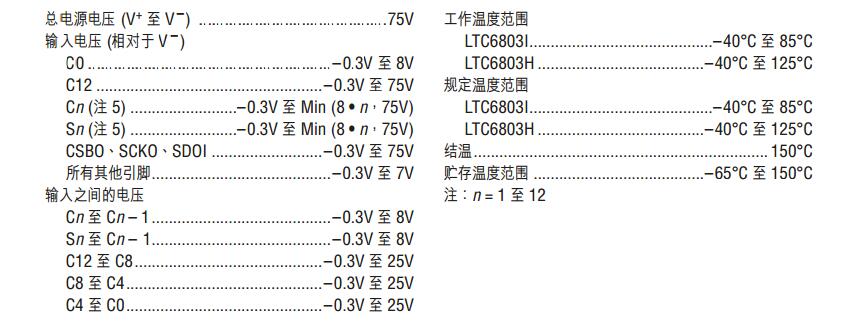

ltc6803绝对最大值

ltc6803引脚及功能

为了确保与LTC6802-1 的引脚兼容性,LTC6803-1 被配置为在内部将底端电池输入(C0)与负电源电压V-相连。LTC6803-3提供了一种独特的引出脚配置,具有一个用于底端电池的输入(C0)。这一简单的引脚功能差异为提升第一节电池(cell 1)的测量准确度、增强SPI噪声耐受性及简化布线提供了可能。更多信息请见应用信息部分中标题为“在CO上进行开尔文(Kelvin) 连接的优势”的相关描述。

CSBO (引脚1) :芯片选择输出(低态有效)。CSBO是芯片选择输入CSBI的一个缓冲版本。CSBO负责驱动菊链中的下一个IC。见“应用信息”部分中的“串行端口”。

SDOI(引脚2):串行数据1/0引脚。SDOI在其与菊链中下一个IC之间来回传送数据。见“应用信息”部分中的“串行端口”。

SCKO (引脚3):串行时钟输出。SCKO是SCKI的一个缓冲版本。SCKO用于驱动菊链中的下一个IC。见“应用信息”部分中的“串行端口”。

V+(引脚4):正电源。引脚4可连接至电池组中的最高正电压或一个隔离式电源。在正常工作条件下,V+必须大于电池组中的最高正电压。当接至隔离式电源时,可简单地通过断开V+来关断LTC6803。

C12、C11、C10、C9、C8、C7、C6、C5、C4、C3、C2、C1 (引脚5、7、9、11、13、15、17、19、21、23、25、27):C1至C12是用于监视电池电压的输入。对于LTC6803-1,底端电池的负端子连接至引脚V- (而对于LTC6803-3则连接至引脚CO)。次最低电压连接至C1,依次类推。有关将电池连接至LTC6803-1和LTC6803-3的更多详情,请见“应用信息”部分中的插图。LTC6803能监视多达12节串联连接的电池。串接的每节电池都必须具有一个大于或等于位于其下方之电池电压的共模电压。允许100mV的负电压。

S12、S11、S10、S9、S8、S7、S6、S5、S4、S3、S2、S1 (引脚6、8、10、12、14、16、18、20、22、24、26、28):S1至S12引脚用于平衡电池组里的电池。如果串联电池中的一节电池过度充电,则S输出的内部可用于对该节电池进行放电。每个S输出的内部具有一个用于放电N沟道MOSFET。见“方框图”。该NMOS的最大导通电阻为20Q。应把一个外部电阻器与NMOS相串联,以在LTC6803封装的外部散逸热量。当采用内部NMOS对电池放电时,应监视芯片温度。见“应用信息”部分中的“功率耗散和热停机”。此外,S引脚的内部还具有一个上拉PMOS。这使S引脚能用于驱动外部MOSFET的栅极,以获得较高的放电能力。

C0 (LTC6803-3上的引脚29):底端电池的负端子。C0与V-形成了开尔文(Kelvin)连接,可消除V-印制线上的电压降所产生的影响。

V- (LTC6803-1 上的引脚29/LTC6803-3 。上的引脚30):把V-连接至串联电池组中的最负电压。

NC(LTC6803-1上的引脚30/LTC6803-3.上的引脚31):该引脚未被使用并在内部通过109电阻连接至V-。它可被置于悬空状态或连接至PCB上的V-。

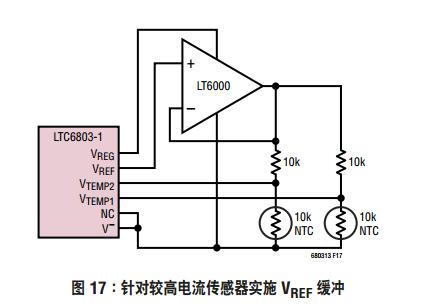

VTEMP1、VTEMP2(LTC6803-1上的引脚31、32/LTC6803-3. 上的引脚32、33):温度传感器输入。ADC负责测量VTEMPn上的电压(相对于V7)并将测量结果存储于TMP寄存器中。ADC测量以VREF引脚电压为基准。因此,可以采用连接至VREF引脚的热敏电阻与电阻器的简单组合来监温度。VTEMP输入也可以是通用的ADC输入。可测量介于0V至5.125V (相对于V-)的任何电压。

VREF (LTC6803-1上的引脚33 / LTC6803-3上的引脚34):3.065V电压基准输出。该引脚应采用一个1pF电容器进行旁路。VREF引脚能驱动一个连接至V-的100k阻性负载。较大的负载应采用一个LT6003运算放大器或相似器件加以缓冲。

VREG (LTC6803-1上的引脚34 1 LTC6803-3上的引脚35):线性稳压器输出。该引脚应采用一个1pF电容器进行旁路。VREG能向一个外部负载提供高达4mA的电流。VREG引脚不吸收电流。

TOS (LTC6803-1.上的引脚 35/ LTC6803-3上的引脚36):电池组顶端输入。当LTC6803-1或LTC6803-3是菊链中的顶端器件时,将TOS连接至VREG。否则,将TOS连接至V-。当TOS被连接至VREG时,LTC6803-1或LTC6803-3将忽略SD0I输入,而且SCKO、CSBO被关断。当TOS被连接至V一时,LTC6803-1或LTC6803-3预计数据将被传送至SDOI引脚及从SDOI引脚输出。

NC (LTC6803-1. 上的引脚36):不连接。

WDTB(引脚37):看门狗定时器输出(低态有效)。如果连续1至2.5s未接收到有效命令,则WDTB输出被置为有效。WDTB引脚是一个漏极开路NMOS输出。当其被置为有效时,它将输出下拉至V-并把配置寄存器复位至其默认状态。

GPI01、GPI02(引脚38、39):通用输入/输出。通过把一个“0”写入一个GPIO配置寄存器位,漏极开路输出被启动且该引脚被拉至V-。通过将逻辑“1”写入配置寄存器位,对应的GPIO引脚呈高阻抗。需要一个外部电阻器将该引脚拉至高达VREG。通过读取配置寄存器存储单元GPI01和GPI02的信息,即可确定这些引脚的状态。例如:倘若一个“0”被写至寄存器位GPI01,则始终回读一个“0”,这是因为输出N沟道MOSFET将引脚38拉至V-。如果一个“1”被写至寄存器位GPIO1,则引脚变至高阻抗。视引脚38上的电压的不同,回读一个“1”或“0”。LTC6803可通过GPIO接通1关断其周围的威廉希尔官方网站 ,或者从周围的某个威廉希尔官方网站 读取逻辑值。GPIO引脚不用时应连接至V-。

VMODE (引脚40):电压模式输入。当VMoDE连接至VREG时,SCKI、SDI、SDO和CSBI引脚被配置为电压输入和输出。这意味著这些引脚可接受标准的TTL逻辑电平。当LTC6803-1或LTC6803-3是菊链中的底端器件时,把VMoDE连接至VREG。当VMoDE连接至V-时,SCKI、SDI和CSBI引脚被配置为电流输入和输出,而SDO未使用。当LTC6803-1或LTC6803-3由菊链中的另一个LTC6803-1或LTC6803-3进行驱动时,把VMDE连接至/-。

SCKI(引脚41):串行时钟输入。倘若VMDE连接至VREG‘则SCKI引脚可连接至任何逻辑门(TTL电平)。假如VMODE连接至V-,那么SCKI必须由另一个LTC6803-1或LTC6803-3的SCKO引脚驱动。见“应用信息”部分中的“串行端口”。

SDI(引脚42) :串行数据输入。如果VMODE连接至VREG,则SDI引脚可连接至任何逻辑门(TTL电平)。如果VMODE连接至V-,那么SDI必须由另一个LTC6803-1或LTC6803-3的SDOI引脚驱动。见“应用信息”部分中的“串行端口”。

SD0(引脚43):串行数据输出。倘若VMODE连接至VREG,则SDO引脚是一个NMOS漏极开路输出。在SDO上需要布设一个上拉电阻器。如果VMODE连接至V-,则不使用SDO引脚。对于那些非堆栈底端的器件,当从堆栈读取数据时,SDI是一个数据输出。见“应用信息”部分中的“串行端口”。

CSBI (引脚44) :芯片选择(低态有效)输入。假如VMoDE连接至VREG:则CSBI引脚可连接至任何逻辑门(TTL电平)。如果VMODE连接至V-,那么CSBI必须由另一个LTC6803-1或LTC6803-3的CSBO引脚驱动。见“应用信息”部分中的“串行端口”。

ltc6803方框图

ltc6803时序图

ltc6803封装

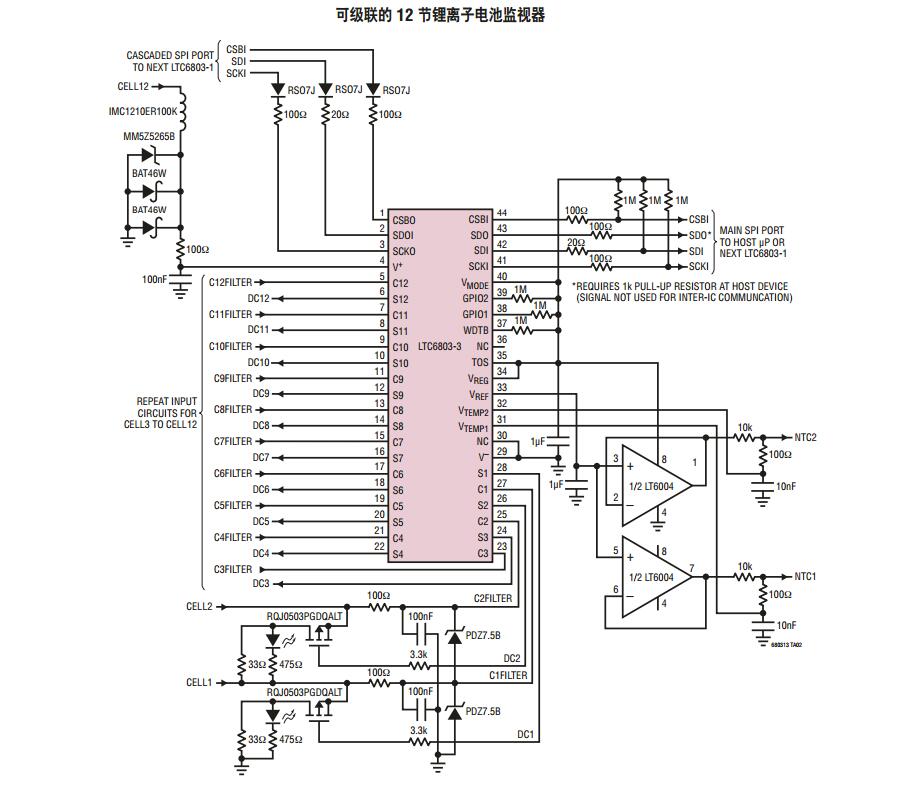

ltc6803应用威廉希尔官方网站

应用威廉希尔官方网站 一:

应用威廉希尔官方网站 二:

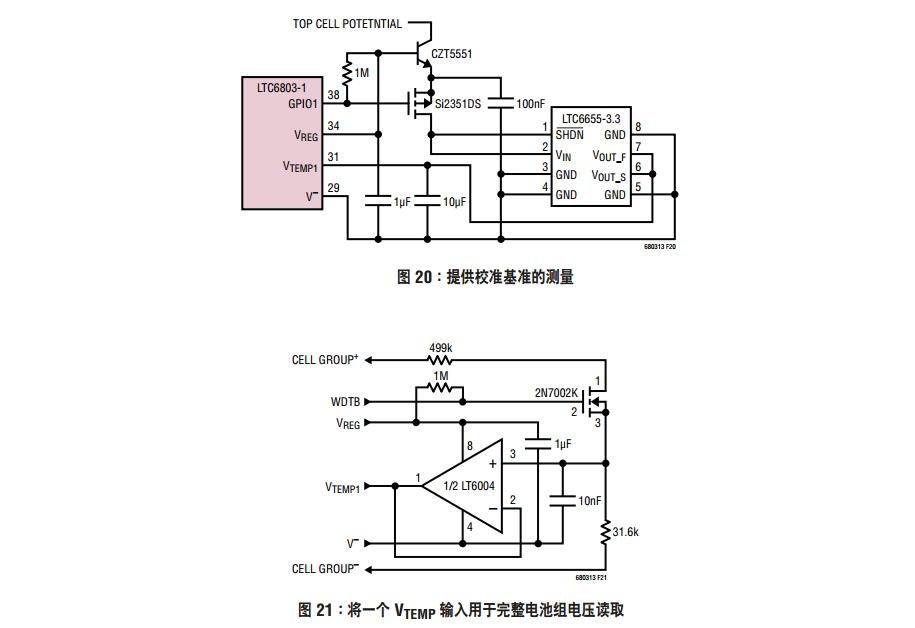

通用的VTEMP ADC输入可用于对任何0V至4V信号进行数字转换,其准确度与第1节电池的ADC输入紧密对应。提供的一个有用信号是高准确度电压基准,例如:来自LTC6655-3.3的3.300V。利用该信号的周期性读数,主机软件能校正LTC6803读数,以把准确度提升至超过内部LTC6803基准的水平和/或验证ADC操作。图20示出了一种在LTC6803-1的GPI01输出的控制下,优先选择利用电池组对一个LTC6655-3.3进行供电的方法。如果由VREG供电,那么基准IC的操作功耗将给LTC6803增加明显的热负载,因此采用一个外部高电压NPN传输晶体管从电池组形成一个局部4.4V电源(Vbe低于VREG)。GPI01信号负责控制一个PMOS FET开关,以在即将执行校准时启动基准。由于GPIO信号在停机模式中默认至逻辑高电平,因此在空闲周期中基准将自动关断。

另一个有用的信号是电池组的总电压值。这可在正常采集过程中出现操作故障时提供一种冗余的可用电池测量,或作为一种更加快捷的监视整个电池组电压的方法。图21示出了怎样采用一个阻性分压器来获得完整电池组电压的比例表示。当IC进入待机模式时(即:当WDTB变至低电平时),采用一个MOSFET使电池组上的阻性负载断接。图中示出了一个LT6004微功率运算放大器部分,用于缓冲分压器信号以保持准确度。该威廉希尔官方网站 的优点是:其转换频度大约可以比整个电池阵列的快4倍,因而提供了一个较高的采样速率选项(代价则是精度/准确度略有下降),从而为校准与电池平衡数据保留了高分辨率电池读数。

应用威廉希尔官方网站 三:

-

在哪里可以找到LTC6803元件库2016-04-05 0

-

电池监视IC芯片LTC68031相关资料分享2021-04-01 0

-

电池监视威廉希尔官方网站 LTC6803相关资料下载2021-04-16 0

-

LTC6803-1 / LTC6803-3 pdf中文资料2012-09-21 6607

-

基于STM32和LTC6803的电池管理系统设计2015-11-20 2506

-

LTC6803在镍氢电池储能管理系统中的应用2017-12-20 4145

-

基于LTC6803的低成本燃料电池单体电压监测器设计2018-02-21 6878

-

LTC6803-3在锂电检测系统中的应用2017-12-20 2567

-

基于LTC6803多节动力电池的检测系统设计2017-12-21 3761

-

基于LTC6803的电动车锂电池管理系统设计2017-12-21 3416

-

最全最详细LTC6803使用笔记总结2018-05-15 18441

-

关于 LTC6803 的特性介绍及其应用2018-06-28 5108

全部0条评论

快来发表一下你的评论吧 !