资料下载

×

通过单边带来估计时钟源的相位噪声的通用公式的详细介绍

消耗积分:0 |

格式:rar |

大小:0.21 MB |

2018-05-16

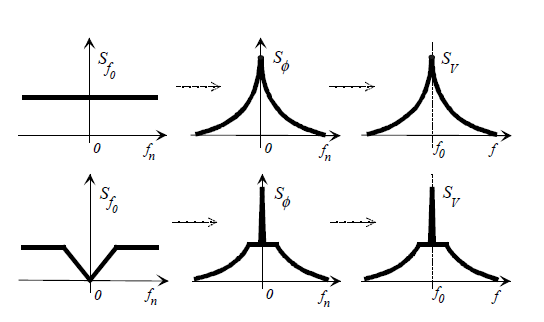

本文介绍了一种通过单边带来估计时钟源的相位噪声的通用公式。载波比(SSCR),振荡周期的周期抖动。该链接允许无缝聚合。

外部时钟源相位噪声,通常以dBC/Hz给出,与片上时钟同步威廉希尔官方网站 的相位稳定图相比,通常以PS RMS为准。这允许依次评估它们对采样威廉希尔官方网站 的总孔径抖动的影响,从而最终能够确定如系统中所示的类似于数字转换器的系统的SNR。

时域和频域数字的关系的有效性首先在双极和CMOS集成VCO的相位谱上进行了测试;此后,基于PLL的频率合成器的最流行情况已经被采用时间toApple来处理。转换技术,或专用的相位噪声测试设备。

通过使用这里提出的公式并在250FS中严格量化的优化ARTEPOLL抖动的状态所启用的最佳性能,在德克萨斯仪器ADS5420上展示,用于3G无线基础设施BTS应用的高速14B 6MSPS ADC。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

评论(0)

发评论

- 相关下载

- 相关文章