8259引脚和工作原理介绍

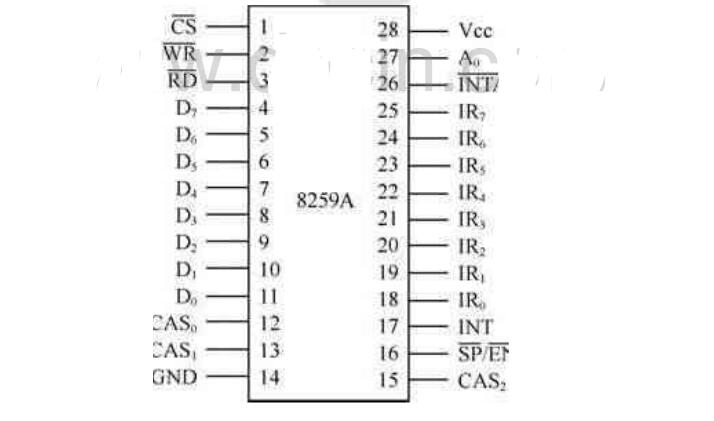

芯片引脚图

描述

8259A主要功能

①一片8259A可以接受并管理8级可屏蔽中断请求,通过8片8259A级联可扩展至63级可屏蔽中断优先控制。

②对每一级中断都可以通过程序来屏蔽或允许。

③在中断响应周期,8259A可为CPU提供相应的中断类型码。

④具有多种工作方式,并可通过编程来加以选择。

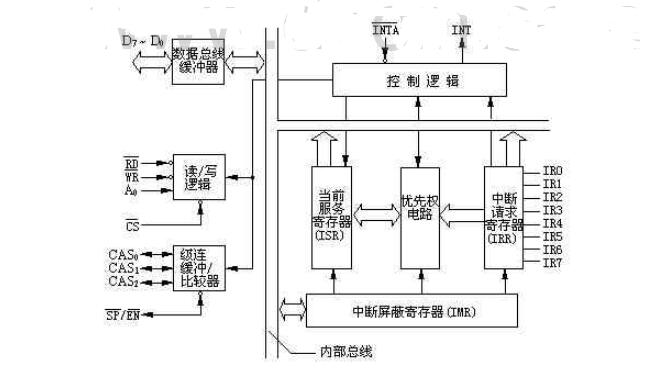

8259A内部结构

8259A引脚图

8259A与CPU相连的接口引脚:

Do~D 7:双向三态数据线,是CPU和8259A进行数据、命令状态传送的通道。

WH:写控制输入信号,低电平有效。有效时,表明当前正在向8259A写入命令字。

RD 读控制输入信号,低电平有效。有效时,表明CPU正在向8259A读数据。

Ao: 片内地址选择信号,用来指出当前8259A的哪个端口被访问。每片8259A有两端口地址。

cs 片选输入信号,低电平有效,通过地址译码逻辑威廉希尔官方网站 与地址总线相连。

INT:与CPU的INTR端相连,由8259A向CPU发出中断请求信号。

INTA:接收来自CPU的中断响应信号。8259A要求中断响应信号由两个负脉冲构成

8259A工作方式

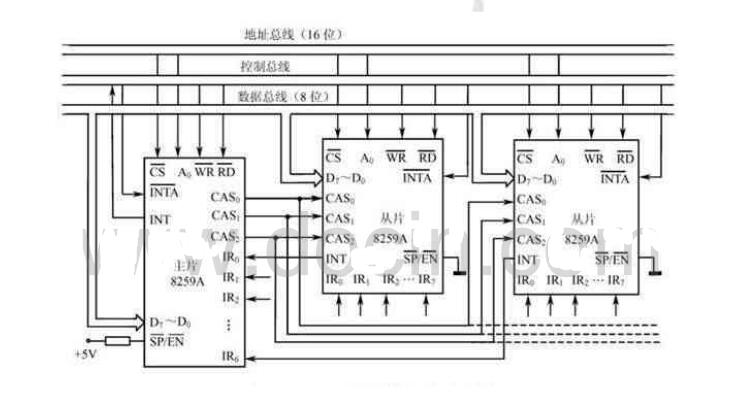

8259A的中断管理功能很强,单片可以管理8级外部中断,在多片级联方式下最多可以管理64级外部中断,并且具有中断优先权判优、中断嵌套、中断屏蔽和中断结束等多种中断管理方式。

1.中断优先权方式

8259A中断优先权的管理方式有固定优先权方式和自动循环优先权方式两种

2.中断嵌套方式

8259A的中断嵌套方式分为完全嵌套和特殊完全嵌套两种。

3.中断屏蔽方式

中断屏蔽方式是对8259A的外部中断源IR7~IRO实现屏蔽的一种中断管理方式,有普通屏蔽方式和特殊屏蔽方式两种。

4.中断结束方式

中断结束方式分为:自动结束方式、普通结束方式和特殊结束方式

5.8259A数据线与系统数据总线的连接有缓冲和非缓冲两种方式。

8259A工作原理

一个外部中断请求信号通过中断请求线IRQ,传输到IMR(中断屏蔽寄存器),IMR根据所设定的中断屏蔽字(OCW1),决定是将其丢弃还是接受。如果可以接受,则8259A将IRR(中断请求暂存寄存器)中代表此IRQ的位置置1,以表示此IRQ有中断请求信号,并同时向CPU的INTR(中断请求)管脚发送一个信号。但CPU这时可能正在执行一条指令,因此CPU不会立即响应。而当这CPU正忙着执行某条指令时,还有可能有其余的IRQ线送来中断请求,这些请求都会接受IMR的挑选。如果没有被屏蔽,那么这些请求也会被放到IRR中,也即IRR中代表它们的IRQ的相应位会被置1。

当CPU执行完一条指令时后,会检查一下INTR管脚是否有信号。如果发现有信号,就会转到中断服务,此时,CPU会立即向8259A芯片的INTA(中断应答)管脚发送一个信号。当芯片收到此信号后,判优部件开始工作,它在IRR中,挑选优先级最高的中断,将中断请求送到ISR(中断服务寄存器),也即将ISR中代表此IRQ的位置一,并将IRR中相应位置零,表明此中断正在接受CPU的处理。同时,将它的编号写入中断向量寄存器IVR的低三位(IVR正是由ICW2所指定的,不知你是否还记得ICW2的最低三位在指定时都是0,而在这里,它们被利用了!)这时,CPU还会送来第二个INTA信号,当收到此信号后,芯片将IVR中的内容,也就是此中断的中断号送上通向CPU的数据线。

这个内容看起来仿佛十分复杂,但如果我们用一个很简单的比喻来解释就好理解了。CPU就相当于一个公司的老总,而8259A芯片就相当于这个老总的秘书。现在有很多人想见老总,但老总正在打电话,于是交由秘书先行接待。每个想见老总的人都需要把自己的名片交给秘书,秘书首先看看名片,有没有老总明确表示不愿见到的人,如果没有就把它放到一个盒子里面。这时老总的电话还没打完,但不停的有人递上名片求见老总,秘书就把符合要求的名片全放在盒子里了。老总打完电话了,探出头来问秘书:有人想见我吗?这时,秘书就从盒子里挑选一个级别最高的,并把他的名片交给老总。

这里需要理解的是中断屏蔽与优先级判定并不是一回事,如果被屏蔽了,那么参加判定的机会也都没了。在默认情况下,IRQ0的优先级最高,IRQ7最低。当然我们可以更改这个设定,这样在下面有详细描述。

当芯片把中断号送上通往CPU的数据线后,就会检测ICW4中的EOI是否被置位。如果EOI被置位表示需要自动清除中断请求信号,则芯片会自动将ISR中的相应位清零。如果EOI没有被置位,则需要中断处理程序向芯片发送EOI消息,芯片收到EOI消息后才会将ISR中的相应位清零。

这里的机关存在于这样一个地方。优先权判定是存在于8259A芯片中的,假如CPU正在处理IRQ1线来的中断,这时ISR中IRQ1所对应的位是置1的。这时来了一个IRQ2的中断请求,8259A会将其同ISR中的位进行比较,发现比它高的IRQ1所对应的位被置位,于是8259A会很遗憾的告诉IRQ2:你先在IRR中等等。而如果这时来的是IRQ0,芯片会马上让其进入ISR,即将ISR中的IRQ0所对应的位置位,并向CPU发送中断请求。这时由于IRQ1还在被CPU处理,所以ISR中IRQ1的位也还是被置位的,但由于IRQ0的优先级高,所以IRQ0的位也会被置位,并向CPU发送新的中断请求。此时ISR中IRQ0与IRQ1的位都是被置位的,这种情况在多重中断时常常发生,非常正常。

如果EOI被设为自动的,那么ISR中的位总是被清零的(在EOI被置位的情况下,8259A只要向CPU发送了中断号就会将ISR中的相应位清零),也就是如果有中断来,芯片就会马上再向CPU发出中断请求,即使CPU正在处理IRQ0的中断,CPU并不知道谁的优先级高,它只会简单的响应8259A送来的中断,因此,这种情况下低优先级的中断就可能会中断高优先级的中断服务程序。所以在PC中,我们总是将EOI位清零,而在中断服务程序结束的时候才发送EOI消息。

8259A应用实例

在Intel 80486 CPU系统中,使用2片8259A管理中断,采用级联方式。主片中的8个中断请求IR7~IRO除IR2扩展从片以外,其他均为系统使用,从片中的8个中断请求IR7~IR0供用户使用。

-

uc3842引脚图 uc3842引脚功能2007-12-22 35887

-

8259引脚图引脚功能2008-01-11 8335

-

62256引脚图2008-04-01 23686

-

62128引脚图2008-04-01 9948

-

76810引脚功能2009-04-29 3399

-

LA76810引脚功能介绍2013-09-06 1406

-

uc3846工作原理(uc3846引脚功能_内部结构及应用威廉希尔官方网站 图)2018-01-25 138502

-

74ls164内部结构及其应用(74ls164引脚图及功能_工作原理)2018-01-27 109227

-

ad623中文资料汇总(ad623引脚图_工作原理及应用威廉希尔官方网站 )2018-04-02 74596

-

74ls07引脚图及功能_74ls07工作原理2018-04-04 78384

-

ad630中文资料汇总(ad630引脚图及功能_工作原理及应用威廉希尔官方网站 )2018-04-13 37279

-

8086CPU中文资料汇总(8086引脚图及功能_工作原理及应用威廉希尔官方网站 )2018-04-16 69534

-

8255芯片中文资料汇总(8255引脚图及功能_工作原理及应用威廉希尔官方网站 )2018-04-23 91519

-

8251芯片中文资料汇总(8251引脚图及功能_工作原理及应用威廉希尔官方网站 )2018-04-23 52335

-

什么是4引脚PWM接头?4引脚PWM风扇如何工作?2023-07-06 9073

全部0条评论

快来发表一下你的评论吧 !