先进封装技术WLCSP和SiP的发展现状和趋势

制造/封装

描述

关于先进封装工艺的话题从未间断,随着移动电子产品趋向轻巧、多功能、低功耗发展,高阶封装技术也开始朝着两大板块演进,一个是以晶圆级芯片封装WLCSP(Fan-In WLP、Fan-out WLP等)为首,功能指向在更小的封装面积下容纳更多的引脚数;另一板块是系统级芯片封装(SiP),功能指向封装整合多种功能芯片于一体,压缩模块体积,提升芯片系统整体功能性和灵活性。

图1:主要封装形式演进

Source:拓璞产业研究所整理,2016.9

WLCSP:晶圆级芯片封装(Wafer Level Chip Scale Package)也叫WLP。与传统封装工艺相反,WLP是先封装完后再切割,因此切完后芯片的尺寸几乎等于原来晶粒的大小,相比传统封装工艺,单颗芯片封装尺寸得到了有效控制。

如何在更小的尺寸芯片上容纳更多的引脚数目?WLP技术利用重分布层(RDL)可以直接将芯片与PCB做连接,这样就省去了传统封装DA(Die attach)段的工艺,不仅省去了DA工艺的成本,还降低了整颗封装颗粒的尺寸与厚度,同时也绕过DA工艺对良率造成的诸多影响。

起初,Fan-In WLP单位面积的引脚数相对于传统封装(如FC BGA)有所提升,但植球作业也仅限于芯片尺寸范围内,当芯片面积缩小的同时,芯片可容纳的引脚数反而减少,在这个问题的节点上,Fan-out WLP诞生,实现在芯片范围外充分利用RDL做连接,以此获取更多的引脚数。

图2:从传统封装至倒装封装及晶圆级封装结构变化示意图

Source:拓璞产业研究所整理,2016.9

SiP:将不同功能的裸芯片通过整合封装的方式,形成一个集多种功能于一体的芯片组,有效地突破了SoC(从设计端着手,将不同功能的解决方案集成与一颗裸芯片中)在整合芯片途径中的限制,极大地降低了设计端和制造端成本,也使得今后芯片整合拥有了客制化的灵活性。

另外由SiP延伸的3D堆叠式封装技术,通过在垂直方向上增加可放置晶圆的层数来进一步提高SiP的整合能力,可以说作为异质整合的标杆,SiP在超越摩尔定律方面扮演着头号角色。

图3:SiP 的基本分类

Source:拓璞产业研究所整理,2016.9

晶圆厂插足Fan-out封装工艺

台积电的InFo(Intergrated Fan-out)在分类上不仅属于WLCSP的Fan-out技术,同时也属于多晶片封装的SiP技术。

今年台积电以集成扇出型封装InFo的优势抢在三星前一举拿下iPhone7 A10全部订单,三星为了与台积电角逐,期望在下一代iphone手机夺回部分订单,也加快了布局扇形晶圆级封装技术(FoWLP),预计2017年上半年实现量产。

据统计,全球Fan-out 2016年市场规模约1.3亿美元,仍然是一片蓝海,台积电则在Fan-out市场先发制人,处于领先地位。如今Apple开始采用InFo封装技术后,Fan-out市场将会进一步被催化,后期会有更多的制造和封测厂商参与进来。

那么原本属于封测厂商业务领域的蛋糕,现在不得不面临与前端制造厂商一起分食,而随着物联网IoT、移动智能设备等电子产品快速发展,高阶封装技术Fan-out的渗透率将会不断升高。

现阶段封测厂商与制造厂商在高阶封装领域的交叉拓展将会进入一定的磨合期,这个磨合期到底会持续多久,主要取决于封测厂商在Fan-out技术领域推进的步伐,如果届时封测厂商所持Fan-out技术能够快速响应前端制造厂商产品需求,那么接下来的发展很有可能趋向共赢方向——制造端与封测端各司其职、明确分工、互惠共赢。

目前来看,在这场博弈中封测厂商处于被动地位,承担了更多压力,在台积电InFo问世之前,包括星科金朋、艾克尔、日月光、矽品等在内的封测厂商均已将Fan-out技术纳入先进制程蓝图中,下一步实力厂商如果决心拿下这幅封测蓝海图,在购入相关设备及增加研发投入方面定会不遗余力。

图4:WLCSP和SiP封装在制造产业链间的交叉拓展

Source:拓璞产业研究所整理,2016.9

SiP封装技术侵蚀后端模组组装利润

如果说封测厂商在Fan-out技术方面正面对着来自制造端压力,SiP技术则为封测厂商带来了一份大礼。SiP封装工艺不仅仅是将多功能芯片整合于一体,还将组装模块的体积大幅地缩小,甚至可以跳过PCB等模组连接工艺。

也就是说,封测厂商通过SiP技术,将业务领域向下游大幅覆盖至组装及模块厂,那么处于下游的模块组装厂商,原本利润就低,如今又要面临来自封测端竞争的压力,随着SiP技术在智能手机、VR/AR、智能穿戴设备等越来越多的应用,SiP在制造产业链中的交叉拓展将会更加深入。

未来趋势判断:因SiP产生的交叉份额会基于在封测端技术和成本的优势,封测厂商将占取主导地位,这对后端组装厂营收份额核心技术与管理模式将会产生一定的影响;但是终端组装厂商在系统组装方面仍具备贴近市场的优势,这就要求封测端与终端组装厂商之间由竞争慢慢转向垂直整合模式。

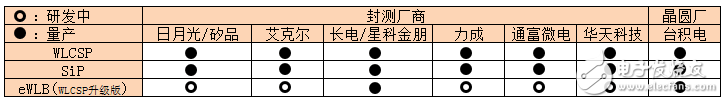

表1:各主要封测厂商与台积电在Fan-out及SiP封测技术现况

Source:拓璞产业研究所整理,2016.9

在物联网、VR/AR、智能手机、智能穿戴设备等热点的强力推动下,高阶先进封装技术Fan-out WLP及 SiP在封测产品中的渗透率会逐渐升高,介于晶圆厂、封测厂及后端模组组装厂之间的竞争将会愈演愈烈,原有产业链结构是否会在未来的博弈中重新划分?一方面要看封测厂商在Fan-out技术开发的效率,另一方面还要看封测厂商在大肆布局SiP的道路上对后端系统组装厂垂直整合的态度,可以说先进封装技术WLCSP与SiP的蝴蝶效应已开始蔓延。

-

SiP(系统级封装)技术的应用与发展趋势2018-08-23 0

-

先进封装技术的发展趋势2018-11-23 0

-

FPGA的发展现状如何?2021-04-08 0

-

有关音频编码标准的发展现状及其趋势2021-04-14 0

-

汽车用基础电子元器件发展现状与趋势是什么?2021-05-17 0

-

探讨智能视频分析技术的应用现状与发展趋势2021-06-03 0

-

广播电视发展现状及趋势2021-07-21 0

-

云计算产业发展现状及趋势2021-07-27 0

-

浅析变频器发展现状和趋势2021-09-03 0

-

先进封装技术WLCSP和SiP的发展现状和趋势分析2020-08-12 2144

-

SiP与Chiplet成先进封装技术发展热点2020-09-17 9723

-

SiP封装技术与WLCSP的现状分析,未来的趋势将是如何2020-09-26 1263

-

先进封装技术FC/WLCSP的应用与发展2022-05-06 850

-

LGA‐SiP封装技术解析2023-05-19 2047

-

深度解读工控安全技术发展现状与应用趋势2023-05-25 3748

全部0条评论

快来发表一下你的评论吧 !