片上总线与板上总线存在若干明显差异

电子说

描述

随着超大规模集成威廉希尔官方网站 的迅速发展,半导体工业进入深亚微米时代,器件特征尺寸越来越小,芯片规模越来越大,可以在单芯片上集成上百万到数亿只晶体管。如此密集的集成度使我们现在能够在一小块芯片上把以前由CPU和外设等数块芯片实现的功能集成起来,由单片集成威廉希尔官方网站 构成功能强大的、完整的系统,这就是我们通常所说的片上系统。

IP复用是片上系统时代的核心技术之一。由于IP核的设计千差万别,它们要能够直接连接,就要遵守相同的接口标准。在片上系统中,处理器核和所有外设通过共享总线互通互联,因此这些IP核必须遵守相同的总线规范。总线规范定义的是IP核之间的通用接口,因此它定义了一套标准的信号和总线周期,以连接不同的模块,而不是试图去规范IP核的功能和接口如何实现。一个片上总线(On-Chip Bus,OCB)规范一般需要定义各个模块之间初始化、仲裁、请求传输、响应、发送接收等过程中驱动、时序、策略等关系。

芯片与威廉希尔官方网站 板的资源和环境的不同,导致片上总线与板上总线存在若干明显差异,包括:

①片上总线多采用单向信号线,而板上总线多采用三态信号。片上三态总线无论在功耗、速度、可测性上都存在很大缺陷,而且一旦出现多驱动情况便会损毁芯片(比如若应该输出"Z"的信号实际输出为"1",而另有一个信号输出为"0",就形成一个低电阻通路,导致局部电流过大,热量难以及时释放,从而增加芯片功耗和大大降低芯片寿命)。由于片上布线资源较为丰富,因此片上总线多采用单向信号线。由于威廉希尔官方网站 板上布线资源较为昂贵,因此板上总线多采用三态总线,但是由于三态总线的功耗问题和速度限制,目前板上总线也在向串行和非三态方向发展,如USB和PCI Express。

②片上总线比板上总线更加简单灵活。首先片上总线结构要简单,这样可以占用较少的逻辑单元;其次时序要简单,以利于提高总线的速度;第三接口要简单,如此可减少与IP核连接的复杂度。片上系统应用广泛,不同的应用对总线的要求各异,因此片上总线具有较大的灵活性。其一,多数片上总线的数据和地址宽度都可变,其二,部分片上总线的互连结构可变,如Wishbone总线支持点到点、数据流、共享总线和交叉开关四种互连方式;其三,部分片上总线的仲裁机制灵活可变,如Wishbone总线的仲裁机制可以完全由用户定制。而板上总线则较为死板,时序也更加苛刻。

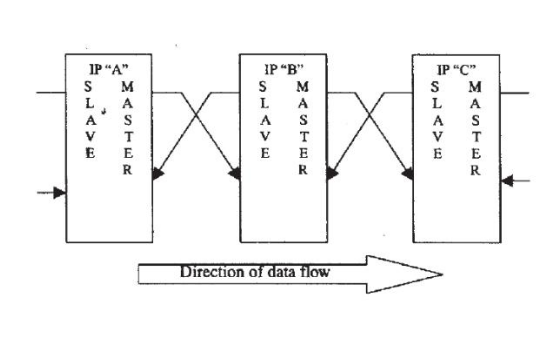

目前比较常见的片上总线规范有ARM公司的AMBA、Silicore的Wishbone、IBM公司的CoreConnect和Altera公司的Avalon。其他三种总线各有特点,其适用范围也不同。AMBA 总线规范因ARM处理器的广泛使用而拥有众多第三方支持,被ARM公司90%以上的合作伙伴采用,已成为广泛支持的现有互连标准之一。IBM公司的CoreConnect因为IBM的业界地位也有广泛的应用。Avalon主要用于Altera公司系列FPGA中,最大的优点在于其配置的简单性,可由EDA工具快速生成。这三种片上总线虽然都是公开标准,但都不是免费的。而Wishbone则是一个真正开放和免费的规范。它最先是由Silicore公司提出的,目前由OpenCores组织维护。由于其开放性,因此OpenCores上的免费的IP核,大多数都采用Wishbone标准。Wishbone的优势除开放、免费、拥有众多免费IP核外,还有简单、灵活、轻量的特点,特别适合大型IP内部的小型IP之间的互联。在很多OpenRISC处理器设计中,各个模块间的互联接口中大量的采用了Wishbone总线规范。

Wishbone已被OPENCORE 联盟采用,并且有可能成为IEEE标准。因此,Wishbone 总线从技术上讲简单、灵活、功能强大及易于移植,从经济角度考虑又全部免费,易于全面推广。我们认为它极有可能成为未来SoC片上总线的通用标准,其前景看好。

Lattice在MachXO3等系列的产品中采用基于Wishbone总线的IP核设计,包括软核和一些硬核(Harden I2C、SPI、Timer/Counter)。学习Wishbone的基本原理,对我们在使用和设计IP时都是很有帮助的。Wishbone作为一个轻量级片上总线,比AMBA等总线简单的多,很适合片上总线的入门者学习。

- 相关推荐

- 芯片

- 集成威廉希尔官方网站

- 总线

-

主从式片上总线系统交易级的实现2009-04-11 506

-

SOPC设计中的两种片上总线分析2011-12-15 1355

-

AMBA片上总线在SoC芯片设计中的应用是什么?2021-05-28 0

-

片上外设总线矩阵内存映射存储器区域功能2021-08-04 0

-

求解ARM的On-Chip Bus片上总线规范是什么2022-04-21 0

-

一种面向应用优化的片上总线调度策略2009-11-18 391

-

AHB片上系统总线的建模与验证2009-11-30 832

-

基于Wishbone片上总线的IP核的互联2010-01-13 523

-

基于AMBA片上总线的片上系统2010-09-01 2105

-

AMBA片上总线在基于IP复用的SoC设计中的应用2017-11-30 1139

-

三种总线的逻辑结构描述及在片上系统中的应用2020-04-04 4304

-

如何利用总线缓冲器挪动主PCB上的I2C器件2021-05-31 6861

-

CAN总线及其在PLC上的应用2021-04-20 730

-

AMBA总线知识之AHB(上)2023-05-04 2493

全部0条评论

快来发表一下你的评论吧 !