如何有效的处理高di/dt负载瞬态?

描述

就许多中央处理器 (CPU) 而言,规范要求电源必须能够提供大而快速的充电输出电流,特别是当处理器变换工作模式的时候。例如,在 1V 的系统中,100 A/uS 负载瞬态可能会要求将电源电压稳定在 3% 以内。解决这一问题的关键就是要认识到 这不仅仅是电源的问题,电源分配系统也是一个重要因素,而且在一款解决方案中我们是很难将这二者严格地划清界限。

这些高 di/dt 要求的意义就在于电压源必须具有非常低的电感。重新整理下面的公式并求解得到允许的电源电感:

在快速负载电流瞬态通道中电感仅为 0.3 nH。为了便于比较,我们来看一个四层威廉希尔官方网站 板上的0.1 英寸 (0.25 cm) 宽威廉希尔官方网站 板线迹所具有的电感大约为 0.7 nH/英寸 (0.3 nH/cm)。IC 封装中接合线的典型电感在1 nH 范围内,印刷威廉希尔官方网站 板的过孔电感在0.2 nH 范围内。

此外,还有一个与旁路电容有关的串联电感,如图 1 所示。顶部的曲线是贴装在四层威廉希尔官方网站 板上的一个22 uF、X5R、16V、1210 陶瓷电容的阻抗。正如我们所期望的那样(100 kHz 以下),阻抗随着频率的增加而下降。然而,在800 kHz时有一个串联电感,此时电容会变得有电感性。该电感(其可以从电容值和谐振频率计算得出)为 1.7 nH,其大大高于我们 0.3 nH 的目标值。幸运的是,您可以使用并联电容以降低有效的 ESL。图 1 底部的曲线为两个并联电容的阻抗。有趣的是谐振变得稍微低了一些,这表明有效电感并不是绝对的一半。基于谐振频率,就两个并联的电容而言,新电感则为 1.0 nH 或ESL 下降 40%,而非下降 50%。这一结果可以归结为两个原因:互连电感和两个电容之间的互感。

图 1 并联电容阻抗寄生现象衰减效果

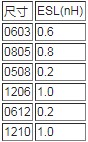

电流通道的环路尺寸在一定程度上决定了连接组件中的寄生电感,组件尺寸决定了环路的面积。尺寸与电感相关系数如表 1 所示,其显示了各种尺寸陶瓷表面贴装电容的电容电感。一般来说,体积越大的电容具有更大的电感。该表不包括威廉希尔官方网站 板上贴装电容的电感,在我们以前的测量中该电感由 1 nH 增加到了 1.7 nH。另一个有趣的问题是端接的位置对电感有很大的影响。0805 电容在电容的较短一侧有端接而0508 电容则在较长的一侧有端接。这几乎将电流通道分为了两半,从而大降低了电感。这种变化了的结构将电感降低了四分之一。

表 1 陶瓷 SMT 电容尺寸会影响寄生电感

总之,高 di/dt 负载需要仔细考虑旁路问题以保持电源动态稳压。表面贴装电容需要非常靠近负载以最小化其互连电感。电容具有可能避免大量去耦的寄生电感。降低这一寄生电感的并联电容是有效的,但互连和互感减弱了这一效果。使用具有更短电流通道的电容也是有效的。这可以用体积较小的部件或具有交流端接(其使用了更短的尺寸用于电流)的部件来实施。

-

如何处理高didt负载瞬态#didtEE_Voky 2022-08-17

-

电源设计#3 简单估算负载瞬态响应2020-07-30 0

-

如何处理高di/dt负载瞬态(上)2012-04-20 2329

-

如何处理高di/dt负载瞬态(下)2012-04-23 1662

-

通过实施有源滤波,减少噪声敏感、高瞬态应用的负载电容2016-01-06 960

-

实施有源滤波,减少噪声敏感、高瞬态应用的负载电容2016-06-01 664

-

基于两级di/dt检测IGBT模块短路策略2016-08-17 5695

-

Si827x数据表:具有高瞬态(dV-dt)抗扰度的4种放大器I2016-12-25 695

-

基于小功率电子负载实现快速负载瞬态测试2022-01-12 1976

-

在高dI/dt时代设计开关模式电源2022-07-28 768

-

小功率电子负载实现快速负载瞬态测试2022-10-28 513

-

“dv/dt”和“di/dt”值:这些值的水平对固态继电器有什么影响?2023-02-20 7880

-

电源的线路和负载瞬态测试2023-03-17 2442

全部0条评论

快来发表一下你的评论吧 !