基于0.35 μmSi CMOS平面工艺设计了SiGe HBT低噪声放大器

描述

基于0.35 μm Si CMOS 平面工艺制定了放大器单芯片集成的工艺流程。为了进一步降低放大器的噪声系数,在制作放大器中SiGe 器件时,采用钛硅合金(TiSi2)来减小晶体管基极电阻。由于没有使用占片面积大的螺旋电感,最终研制出的SiGe HBT LNA 芯片面积仅为0.282 mm2。测试结果表明,在工作频带0.2-1.2 GHz 内,LNA 噪声系数低至2.5 dB,增益高达26.7 dB,输入输出端口反射系数分别小于-7.4 dB 和-10 dB。

1 引言

低噪声放大器(LNA)是射频/微波通讯装置中的核心组件,它位于接受机的前端,好的噪声性能可以提高接受机的灵敏度和扩大动态范围(SFDR)的上限,足够的增益保障放大微弱的接收信号,因此要求放大器提供优异的噪声和增益特性。

与混合集成LNA 相比,单片集成LNA 具有重复生产能力好、威廉希尔官方网站 损耗少,结构紧凑和功耗低等一系列优点,可以大大缩小通讯设备的体积和成本。

从目前报道的有关单片集成LNA文献来看,国内研制的LNA 性能较弱,仍处于起步阶段,缺乏成熟的开发经验,与国外存在一定差距;并且早期采用III-V 器件实现的较多,但是III-V 器件不能与成熟的Si 平面工艺兼容,不利于集成,导致成本高,而SiGe HBT 克服了这个缺点,不但具有高集成度和优越的性价比,还具有优良的频率特性、增益特性和噪声特性,因此SiGe HBT 非常适于作单片集成LNA 的有源器件。

本文采用SiGe HBT 研制出一款单片集成宽带LNA,给出了放大器设计的基本思路,基于0.35 μmSi CMOS 平面工艺制定了放大器单芯片集成的工艺流程,并最终研制出一款SiGe HBT LNA。本研究结果对我国设计开发射频/微波单片集成LNA,尤其对设计开发基于Si CMOS 工艺的单片集成LNA具有重要意义。

2 单片集成SiGe HBT LNA 的威廉希尔官方网站 结构及设计

2.1 威廉希尔官方网站 结构

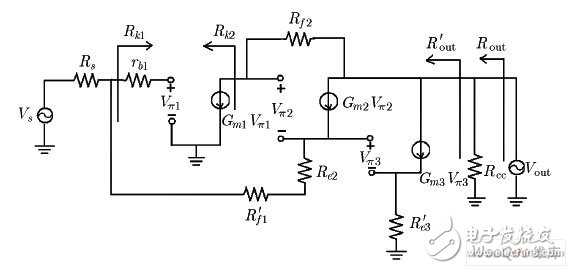

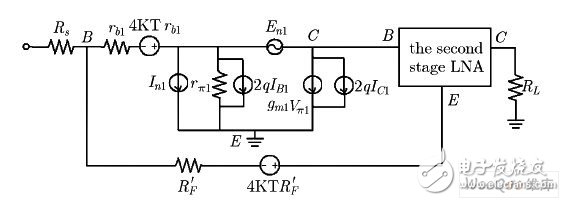

为了制作方便和减小芯片面积,本文设计的LNA 采用复合型电阻负反馈结构,没有使用占片面积大的螺旋电感。图1 是本文设计的SiGe HBTLNA的威廉希尔官方网站 结构图。图中Q1,Q2和Q3是SiGe HBT,其中Q2 和Q3 构成一个达林顿对,可以提高LNA 的系统增益。系统并联反馈电阻(Rf1 和Re3a),局部并联反馈电阻(Rf2)和局部串联反馈电阻(Re2 和Re3b)构成复合型负反馈结构。

图1 采用复合型电阻反馈结构的SiGe HBT LNA 威廉希尔官方网站 结构示意图

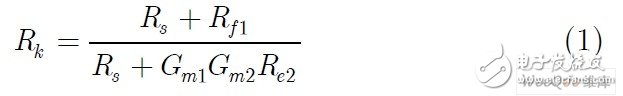

2.2 端口匹配

为了保障信号在整个射频接收机中不失真的传输和降低信号传输能量的泄漏,LNA 需要具备良好的端口匹配。在本节中,将分析SiGe HBT LNA 的端口阻抗并进行优化。图2 给出了图1 中LNA 的交流等效威廉希尔官方网站 。由于LNA 的信号传输能量泄漏主要发生在输出端口,从图中可以看出,从 Q1 输出端看进去的输出阻抗Rk 可表示为:

图2 SiGe HBT LNA 的交流等效威廉希尔官方网站 。

从Q3 输出端看进去的输出阻抗R'out 为:

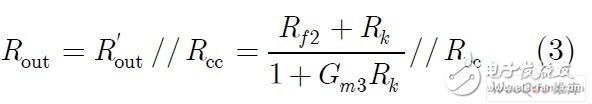

式中GmD 是达林顿对的跨导。LNA 的输出阻抗Rout可表示为:

在一定的偏置下,提供偏置电流的反馈电阻是定值,因此式(1)中的Rf1,式(2)-式(3)中的Rf2 和Rcc 是定值,并且LNA 中的3 个SiGe HBT 的跨导也是定值。分析式(3)可知,适当调整Re2,可改善Rout。图3 给出了SiGe HBT LNA 的输出阻抗Rout与Re2 的关系。从图中可以看出,Rout 随着Re2 的增大而增大,并且当Re2 为21Ω 时,Rout 达到50 Ω,LNA 输出端口达到最佳匹配。

图3 SiGe HBT LNA 的输出阻抗Rout 与Re2 的关系

2.3 威廉希尔官方网站 的噪声特性

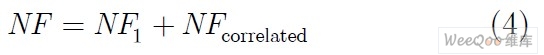

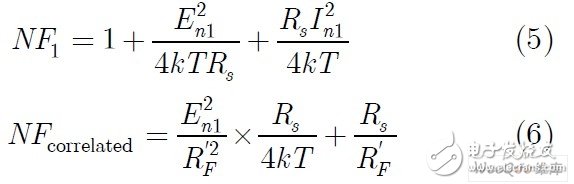

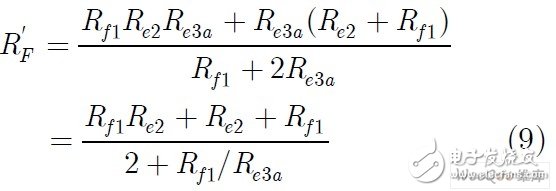

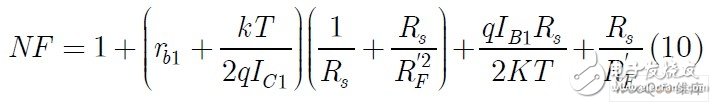

多级LNA 的噪声性能主要决定于第1 级LNA的噪声系数。考虑到本文设计的LNA 有多级反馈支路,因此分析系统噪声系数还应该考虑反馈支路的噪声。此时,放大器的系统噪声系数可表示为:

其中NF1和NFcorrelated分别是第1 级放大器和反馈支路的噪声系数。图4 是SiGe HBT LNA 的小信号等效噪声模型,其中rb1 是Q1 的基极电阻,En1 和In1分别是Q1 的等效噪声电压源和电流源。

图4 SiGe HBT LNA 的小信号噪声模型

通过分析图4 中等效噪声模型, NF1 和NFcorrelated 可写为:

其中k 是波尔兹曼常数,T 是室温,En1 和In1 为:

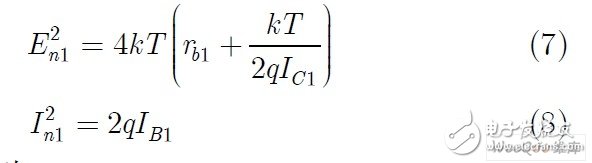

R‘F 可表示为:

式(7)和式(8)中,Rs 是系统源阻抗,在匹配良好时可认为是50 Ω,IC1 和IB1 分别为Q1 的集电极和基极电流。将式(5)-式(8)代入式(4),系统噪声系数可表示为:

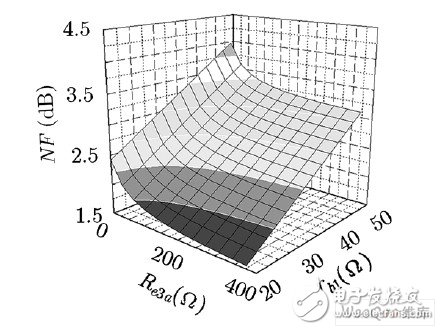

式中仅rb1 和R‘F 是变量,结合式(9)可知,在一定偏置下,提供Q1 基级电流的Rf1 是定值,同时由2.2节分析可知,获得最佳输出端口匹配时Re2 为21 Ω,因此rb1 和Re3a 是式(10)的自变量。图5 为SiGe HBTLNA 的噪声系数NF 随rb1 和Re3a 的变化。可以看出,增大Re3a 可降低系统NF,考虑到Re3a 直接影响LNA 中Q3 的工作电压,最终确定Re3a 为310Ω。

图5 SiGe HBT LNA 的噪声系数NF 与rb1、Re3a 的关系

另外,还可以通过减小rb1 降低噪声系数,由于钛硅合金(TiSi2)具有低电阻率以及良好的与硅材料吸附的能力,因此本文制作LNA 中的SiGe HBT 时,引入金属钛(Ti)形成钛硅合金来减小rb1,结合实际工艺水平,确定rb1 为28 Ω。

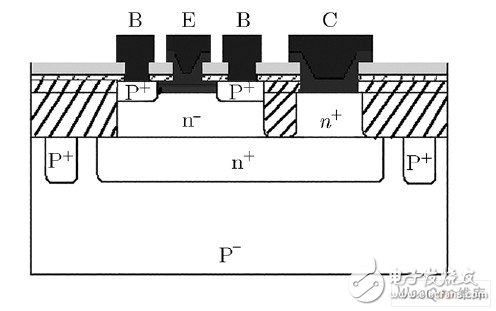

3 器件结构和威廉希尔官方网站 制造

本文基于0.35 μm Si CMOS 平面工艺制定了放大器单芯片集成的工艺流程,并制作出一款单片集成SiGe HBT LNA。图6 是SiGe HBT 的截面图,考虑到工艺的难易程度,本文选用的SiGe HBT 结构为一种多晶硅发射极自对准结构。

图6 SiGe HBT 的截面示意图

工艺流程如下:

(1)选用电阻率为20Ω·cm 的P 型衬底硅片制作N+埋层,注入As,高温退火推结,利用CVD 生长N? 外延层。

(2)生长氧化层。光刻隔离区,刻蚀隔离区氧化层和部分N? 外延层。光刻P+沟阻,B 离子注入。

高温生长SiO2,表面平坦化。

(3)光刻穿透区,腐蚀去除穿透区氧化层。集电区扩P 穿透。在有源区利用MBE 差分外延SiGe 基区。外延之后,涂光刻胶,刻(有源区外)多晶硅。

(4)生长SiO2,淀积Si3N4,刻集电区、基区、发射区欧姆孔内Si3N4 和SiO2。淀积多晶硅,形成侧墙,光刻基区,B 离子注入。光刻集电极和发射极。

(5)溅射金属Ti,经过快速热退火,形成钛硅合金TiSi2,降低基区和发射区接触电阻。TiSi2 形成以后,溅射多层金属(TiW/AlCu),完成金属互联及反馈电阻制作。

(6)去胶,合金。

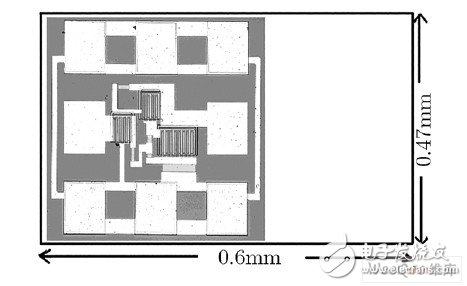

图7 是最终完成的平面集成SiGe HBT LNA 芯片实物的显微照片。LNA 芯片面积仅为0.282 mm2(0.6 mm×0.47 mm),比文献[6]中单片集成SiGeHBT LNA 芯片面积小(0.78×0.66 mm2),这是因为没有使用大面积的在片螺旋电感。

图7 基于0.35-μm Si CMOS 平面工艺制作的单片集成SiGe HBT LNA 芯片图

4 实验结果

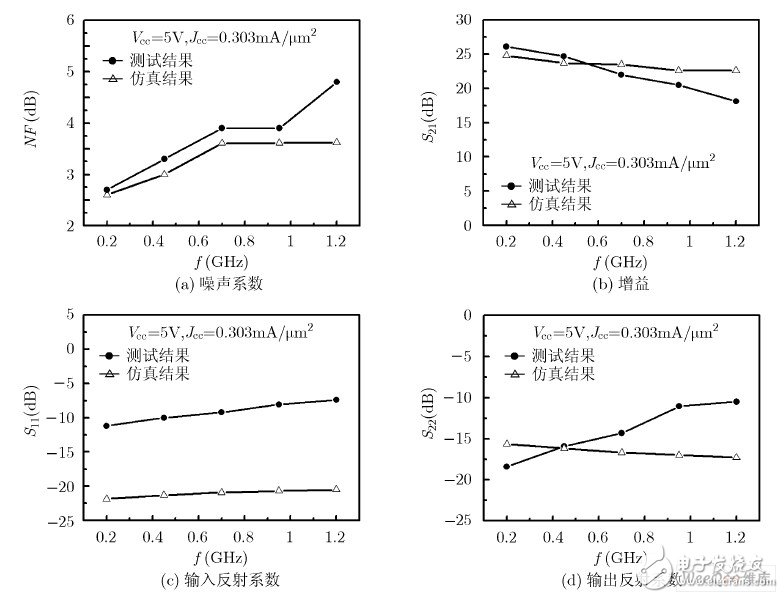

图8 是本文研制的单片SiGe HBT LNA 仿真结果和测试结果对比。从图8(a)和8(b)中可以看出,工作频率从0.2 GHz 上升至1.2 GHz,噪声系数始终小于4.8 dB,最小值低至2.5 dB,增益为18.1-26.7dB。在0.2-1.0 GHz 频带内,仿真结果较好地预测了实际测试结果。

图8 单片SiGe HBT LNA 测试结果与仿真结果对比

图8(c)展示了LNA 的输出端口匹配情况。在整个频带内,输入端口反射系数S11 的实测结果小于-7.4 dB,与仿真结果的偏离值保持在8 dB 左右。

原因可能是在实测中,LNA 的衬底损耗难免影响了输入阻抗,使其偏离了设计时的预期值50 Ω。

图8(d)给出了LNA 的输出端口匹配情况。在整个频带内,输出阻抗反射系数S22 的实测结果小于-10 dB。分析式(3)认为,系统输出阻抗由LNA 的输出电阻与偏置电阻并联而成。在低频时(0.2-0.4GHz),实际制作出的LNA 芯片衬底损耗与寄生效应修正了LNA 的输出阻抗,使系统输出阻抗实测值比仿真值更接近于理想值50 Ω,所以频率较低时,实测结果优于仿真结果。随着频率进一步增大,放大器中电阻在高频下不再是纯实数电阻,其中偏置电阻的虚部值随着频率的增大而加剧影响系统输出阻抗,使输出阻抗实测值逐渐偏离50 Ω,所以在高频时(0.4-1.2 GHz),仿真结果优于实测结果,并随着频率的增加,两者差值增大。虽然图8(c)和8(d)中端口阻抗的实测结果与仿真结果差别较大,但是在绝大部分频带范围内还是小于-10 dB,显示LNA 是具有良好的输入输出匹配。

5 结论

本文研制了一款具有多重电阻反馈结构的单片SiGe HBT 低噪声放大器,通过灵活优化复合型反馈支路中的不同电阻,同时实现了低噪声和良好端口匹配,解决了单一电阻反馈LNA 中的缺点,即需要花费巨大精力反复折中偏置、噪声性能和端口匹配。基于0.35 μm Si CMOS 平面工艺,制定了放大器单芯片集成的工艺流程,并提出在制造SiGe 器件时,采用钛硅合金(TiSi2)来减小rb1,达到进一步降低放大器噪声的目的。基于上述工艺技术研制的单片SiGe HBT LNA 芯片面积仅为0.282 mm2。在端口匹配方面,虽然测试结果与仿真结果存在一定差异,但是其在大部分工作频率范围内仍小于-10 dB,因此本文研制出的LNA 匹配性能良好,并且仿真结果较好地预测了端口阻抗变化趋势;噪声系数和增益方面,测试结果与仿真结果符合较好,反映出设计方法和设计结构的正确性。

-

低噪声放大器,低噪声放大器型号参数2017-09-11 0

-

如何利用Cadence设计COMS低噪声放大器?2021-04-12 0

-

低噪声放大器介绍2021-07-27 0

-

S波段雷达接收机前端低噪声放大器2009-11-01 795

-

利用Cadence设计COMS低噪声放大器2009-07-06 2862

-

低噪声放大器设计的理论基础2009-10-20 6048

-

1.6GHz低噪声放大器(特瑞仕)2009-11-02 732

-

低噪声放大器,低噪声放大器是什么意思2010-03-05 3713

-

3GHz CMOS低噪声放大器优化设计2010-04-13 1658

-

Ku波段低噪声放大器的设计与仿真2011-10-13 915

-

双频带低噪声放大器实现方案2011-10-14 464

-

CMOS基毫米波低噪声放大器的研究2011-12-16 641

-

245GHz+CMOS工艺低噪声放大器的设计.pdf2017-03-05 845

-

低噪声放大器简介2023-01-07 2016

-

低噪声放大器的设计原则2023-07-25 1932

全部0条评论

快来发表一下你的评论吧 !