基于FPGA静态和动态功耗解决方案介绍

描述

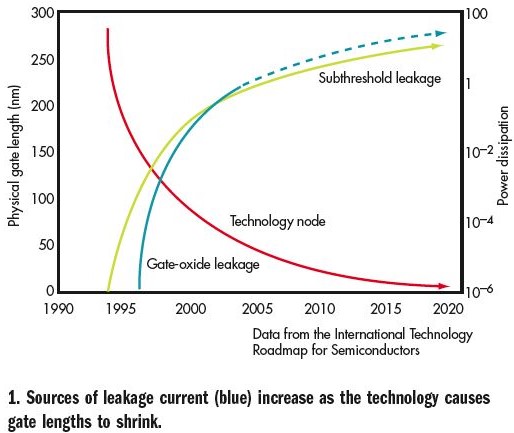

传统上,数字逻辑并不耗费大量静态功耗,但随着工艺节点的不断精微,这一情况在发生显著变化。现在,随着工艺尺度的不断缩微,数字逻辑中的漏电流成为FPGA的主要挑战。因在65nm工艺节点静态功耗会显著增加,所以,若不采取降耗措施,则功耗将成为一个关键问题。因各种原因导致的漏电流的增加,静态功耗将会显著增加(图1)。

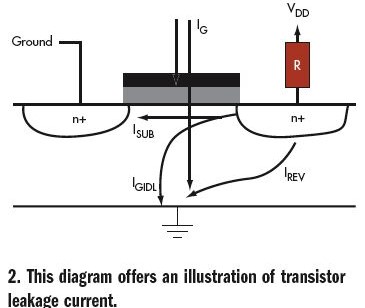

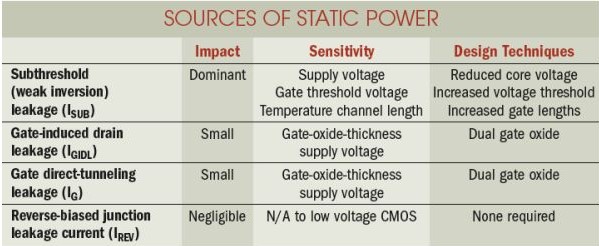

功耗由静态功耗和动态功耗组成。静态功耗是FPGA在被编程目标文件(.pof)编程时、但时钟不工作的状态下所需的功耗。数字和模拟逻辑都消耗静态功耗。在模拟系统中,静态功耗主要包括由其接口模拟威廉希尔官方网站 的静态电流决定的功耗(图2和表)。

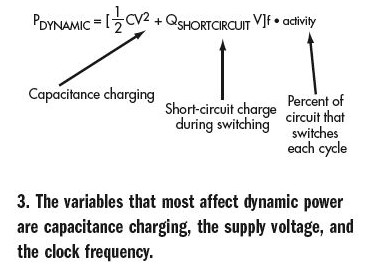

动态功耗是当器件工作时增加的功耗,它由切换信号及容性负载的充放电引起。影响动态功耗的主要变量是电容充电、工作电压和时钟频率(图3)。

借助工艺节点的不断缩微带来的减小电容和降低电压的好处,动态功耗的降低遵从摩尔定律。挑战在于,伴随每一工艺节点的缩微以及最高时钟频率的增加所引发的问题。虽然就相同的威廉希尔官方网站 来说,其功耗随每一工艺节点的缩微在一直下降,但同时FPGA的容量在翻番,且最高时钟频率也在不断增加。

FPGA架构

在架构、工艺技术和威廉希尔官方网站 技术方面的进步有助于解决这些功耗挑战。Altera的Stratix III FPGA就是这样一种产品。

Altera的可编程电源技术(Programmable Power Technology)有助于降低高端FPGA的功耗。传统上,所有高性能的FPGA都由高性能的建构实现,其中,每一逻辑单元(LE)都以大的漏电功耗为代价来提供最佳性能。

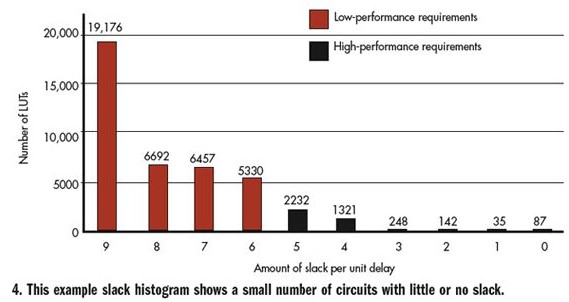

可编程电源技术利用如下事实:设计中的许多威廉希尔官方网站 具有剩余能力,所以并不需要最高性能的逻辑。图4显示的是一个典型的剩余能力柱状图,其中,大多路径(左侧)具有剩余,只有不多的关键路径(右侧)需要最高性能的逻辑以满足时序要求。

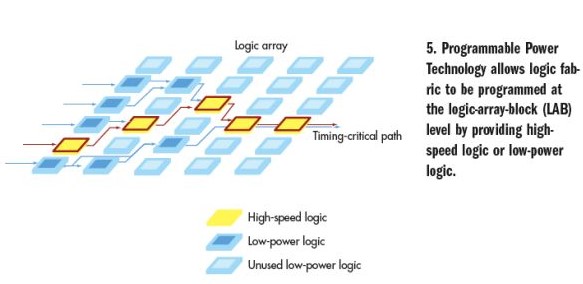

采用可编程电源技术,根据特定逻辑路径所需的是高速还是低速逻辑,通过提供高速或低速逻辑的方法,可对Stratix III的逻辑构造在逻辑阵列块(LAB)级进行编程(图5)。基于这种思路,选出所占比例很小的对时序有苛刻要求的威廉希尔官方网站 进行高速设定,而剩下的实行低功耗设定,采用这种方法,可将低功耗逻辑的漏电功耗降低70%。将不使用的逻辑、以及DSP块和TriMatrix存储器设定为低功耗模式将进一步降低功耗。

可选核电压

可选核电压允许设计师根据性能需求采用0.9或1.1V核电压。0.9V核电压提供整体上最低的动态和漏电功耗;而1.1V核电压提供整体上的最高性能。动态功耗与核电压的平方成正比,而静态功耗是核电压的2.5次方。

在板卡设计时,可选核电压输入可被设定为0.9 V或1.1 V。该核电压为核构造内的所有LAB、存储器和DSP功能提供工作电源。可选核电压影响构造性能,所以,若在软件中选择了器件和速度等级,则还需进行核电压选择。该软件利用与所选核电压相对应的时序和功耗模型来实现全部依赖时序和依赖功耗的分析和优化。

当选择采用哪种核电压时,设计师必须考虑由时序分析得出的系统性能需求。若采用0.9 V就能满足系统性能要求,则肯定比采用1.1 V所用的功耗低。

技术融合

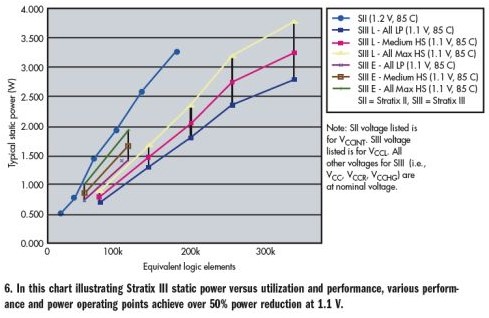

在1.1 V,将可编程电源技术和可选核电压结合起来,可提供降耗50%以上的各种性能和功耗工作点(图6)。基于所用的各种资源(如:DSP块和TriMatrix存储器块),静态功耗会显著不同。

根据核电压和高速逻辑与低功耗逻辑比例的不同,总合起来的静态和动态功耗也各异。在许多设计中,当不需要FPGA的最高性能时,可将设计的整体功耗降低50%以上。

工艺和威廉希尔官方网站 技术

半导体行业通过在设备、工艺技术、设计工具和威廉希尔官方网站 技术方面的巨大投入一直在不懈地迎击随着工艺尺度的缩微所带来的不断挑战。特别是业界面对的随着工艺尺度的缩微而不断增加的漏电流问题。因此,采用了在65nm(及更精微)工艺节点许多广为人知的技术在保证或提升性能的同时来管理漏电功耗,这些技术有:铜布线、低k电介质、多阀值晶体管、可变栅长晶体管、三闸级氧化层、超薄栅氧化层、应变硅。

最低功耗、最高性能

为得到高效率和性能,Stratix III FPGA借力一个自适应逻辑模块(ALM)逻辑架构和多路径(MultiTrack)互连构造。这种结合允许以更少布线整合更多逻辑。

ALM技术(据说可比其它架构实现多80%的逻辑功能)包括一个8输入可分割(fracturable)查找表(LUT)、两个2位累加器和两个寄存器。

多路径互连提供不同LAB间的单跳式(onehop)连接能力且可通过由一个LAB到达另一个LAB所需“跳”的数量来测量。增加连通所需的“跳”也就增加了电容;“跳”的越少,则为满足性能所需的高速逻辑就越少。多路径互连提供单“跳”连通性,因此所需的功耗最低(图7)。

在Stratix III FPGA中采用了分级时钟技术以支持多达360个独立时钟。每一时钟网络的覆盖范围可被控制在一个LAB内。具有共同时钟的逻辑被组合进LAB。时钟仅覆盖到采用该时钟的逻辑域。所有其它时钟信号全部被关闭以把功耗降至最低。

省电的存储器接口

双数据速率(DDR)存储器接口是目前设计最常用的I/O接口,它们可能会相当耗电。为解决这些功耗问题,设计师可求助动态片上终止和DDR3。

当读写外部存储器时,同时拥有一个串行和并行终止阻抗匹配缓冲器至关重要。当写存储器时,若有一个50?的过渡线,则需一个串接阻抗为50?的匹配缓冲器。当读存储器时,则需一个50?的并接终止电阻连至终止电压。这种处理不仅用于DDR型接口,也用于RLDRAM和QDRRAM。

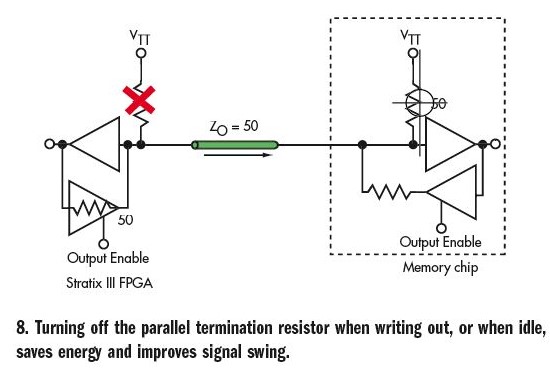

通过支持动态片上终止,根据执行的是读还是写操作,FPGA设计师可将并接终止电阻置为“通”或“断”(开路)状态。在写存储器时,FPGA输出驱动器阻抗必须匹配传输线。但,连至VTT的并接电阻既耗电又减低了信号摆幅。为避免这种情况,可将该电阻关断(图8)。

在读存储器时,接通并接电阻以终止传输线以便减少恶化信号完整性及影响可靠读取数据能力的反射。

当总线无论执行来自FPGA的写操作还是空闲时,都将显著体现动态片上终止的好处。首先,功耗得以极大降低——在一个72位的DDR2总线上,可降低1.6 W的静态功耗。另外,当写操作时,可获得一个纯粹的串接线终止。最后,它不再需要大量的板上终止电阻,从而降低了板成本和复杂性。

因DDR3工作在1.5 V(DDR2是1.8 V),所以,DDR3比DDR2省电30%以上。例如,一个带72脚、具有片上终止的200MHz或400Mbit/s存储器仅一个接口的功耗就是3.9W。采用动态片上终止(其中,在执行写或空闲时,并行终止电阻关断)可降耗1.6 W。若同时采用DDR3和动态片上终止,功耗将降至1.6W,从而一共节省了2.3W。这些数据是仅就一个接口来说的(也即,FPGA中的4个存储器接口共将省电9.2W)。

向极小的65nm及更精微工艺节点的迈进,能带来摩尔定律所预期的密度和性能方面的好处。但,性能的提升导致功耗的巨大增加,从而带来将耗费不可承受功耗的风险。

若不采用降耗措施,静态功耗将显著增加。另外,若没有专门的功耗优化举措,动态功耗将随着逻辑容量的增加和开关频率的升高而增加。

以能力非凡并具创新的架构结合工艺技术和威廉希尔官方网站 技巧方面的进步可应对这些功耗挑战,它们为当今基于FPGA的日益复杂的设计提供了一个有效和可升级的方案。

-

#硬声创作季 #FPGA FPGA-17-02 按键抖动现象介绍与解决方案分析-1水管工 2022-10-29

-

#硬声创作季 #FPGA FPGA-17-02 按键抖动现象介绍与解决方案分析-2水管工 2022-10-29

-

超低功耗FPGA解决方案助力机器学习2018-05-23 0

-

#硬声创作季 #FPGA FPGA-17-02 按键抖动现象介绍与解决方案分析-3水管工 2022-10-29

-

FPGA系统功耗瓶颈的突破2018-10-23 0

-

FPGA中静态功耗的分布及降低静态功耗措施2020-04-28 0

-

实现降低FPGA设计的动态功耗的解决方案2020-05-13 0

-

如何在进行板级设计时,降低系统的静态与动态功耗?2021-04-08 0

-

如何采用创新降耗技术应对FPGA静态和动态功耗的挑战?2021-04-30 0

-

FPGA架构的功耗及影响功耗的用户选择方案2010-08-27 1791

-

FPGA系统设计的静态功耗和动态功耗分析与进行仿真建模2020-01-16 9038

-

基于FPGA的低功耗设计方案2022-11-24 1219

-

集成电源解决方案-Altera FPGA应用介绍2023-11-28 214

-

浅析CMOS威廉希尔官方网站 的静态功耗和动态功耗2024-04-01 6066

-

FPGA如何估算分析功耗2024-07-18 1922

全部0条评论

快来发表一下你的评论吧 !