基于DSP和CPLD技术实现ADC多路信号采集系统设计

描述

引言

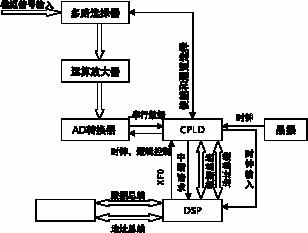

随着现代电子技术的应用和发展,数字信号处理的内容日益复杂,而adc是实现从模拟到数字转换的一个必然过程。针对这种情况,利用数字信号处理器和可编程逻辑器件提出了多路adc系统的设计方法,实现了对动态多路模拟输入信号的采样传输以及处理,简化了威廉希尔官方网站 设计,可编程逻辑器件使得系统的通用性和可移植性得到良好的扩展。系统框图如图1所示。

系统硬件设计

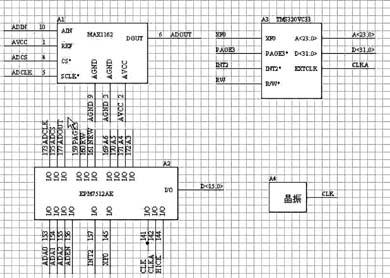

本设计所采用的adc器件是maxim公司的生产的低功耗16位模数转换器(adc)max1162。max1162采用逐次逼近型 adc结构,具有自动关断、1.1μs快速唤醒和兼容于spi/qspi/microwire的高速接口,采用+5v单模拟电源,并且具有独立的数字电源引脚,允许芯片直接和+2.7~+5.25v的数字逻辑接口。ref引脚接外部参考电压,用于设定模拟输入电压范围,与模拟地之间连接一个4.7μf的电解电容;avdd引脚是+5v电源供应输入端,与模拟地之间接一个0.1μf的电容;agnd是模拟地;cs是片选输入,低有效。当为高时,系统处于断电模式,由高变低时,激活系统到正常运行模式,同时初始化一次转换。本系统选择作为ad的使能信号;sclk是串行时钟输入,驱动模数转换进程;dout是串行数据输出,数据状态在sclk的下降沿改变;dgnd是数字地;dvdd是数字电压供应,与数字地之间接一个0.1μf的电容;ain是模拟信号输入端。

该adc系统的中央控制单元采用ti(德州仪器)公司的浮点数字信号处理器tms320vc33-150,tms320vc33的地址总线为24位,程序寻址范围可达16m,数据总线为32位,内部具有34k×32bit的sram,可根据需要映射在程序或数据空间,拥有一路串行口,可以构成传输8、16、24、32位的数据,其传输模式可以设置为突发模式或者是连续模式。两个32位的通用定时器,能够用来按照规定的时间间隔与芯片内部通信或者是和外部通信。

使用x9241实现高分辨率的软件代码

为了方便理解实现控制的细节,我们提供了c语言源代码(代码由xicor公司提供,我们做了一定的修改)。用户只需要自己再编写适用于不同单片机的i2c硬件接口函数(函数名称同程序中介绍一致),在应用程序中加入我们提供的源代码,简单的调用程序中介绍的5个函数,就可以方便地实现dcp的高分辨率控制。

关于x9241实现高分辨率的软件源代码,工程师可到http://www.icbase. com/download/x9241.c去下载。

本系统考虑到主要应用在adc中,所以就直接采用tms320vc33的数据总线和地址总线,没有再附加额外的威廉希尔官方网站 ,使得adc的采样速度和转换精度得到良好的保证。同时还利用了int2和xf0引脚,作为dsp接收数据的中断信号和adc的使能信号。int2是外部中断引脚,由外部的数据输入触发中断;xf0即外部标志输出引脚,受软件控制,可以用来向外部器件发送信号,该引脚的状态由i/o标志寄存器决定,iof=0x22,即置xf0为通用目的输出引脚,同时该引脚输出0;若iof=0x26,则置xf0为通用目的输出引脚,同时该引脚输出为1。本系统利用软件指令对xf0进行置高置低,控制adc的启动转换和停止。

emp7512ae基于eeprom技术,采用多电压i/o接口技术,系统内核供应电压为3.3v,而i/0引脚与2.5v、3.3v、5.0v逻辑电平相互兼容。epm7512ae有10 000个可用门、512个宏单元、32个逻辑阵列块和212个用户可用i/0引脚。cpld在系统中的主要功能是:给adc转换提供时钟信号,控制adc转换的使能和复位,由于采用的adc芯片是串行输出的,cpld还实现对串行数据的输入转为并行数据的输出,然后直接和tms320vc33的数据总线相连接。同时cpld产生脉冲信号,在adc转换完成后,数据暂存在cpld中,该脉冲向cpu申请中断,提示有数据需要接收。另外,cpld的一个关键作用就是,实现路数的动态选择,目前设计的该系统最多路数为8路。cpld和dsp及ad芯片的具体硬件连接图如图2所示。

使用x9241实现高分辨率的软件代码

为了方便理解实现控制的细节,我们提供了c语言源代码(代码由xicor公司提供,我们做了一定的修改)。用户只需要自己再编写适用于不同单片机的i2c硬件接口函数(函数名称同程序中介绍一致),在应用程序中加入我们提供的源代码,简单的调用程序中介绍的5个函数,就可以方便地实现dcp的高分辨率控制。

关于x9241实现高分辨率的软件源代码,工程师可到http://www.icbase. com/download/x9241.c去下载。

下面给出vhdl语言的主要程序部分。

begin

adcs 《= synthesized_wire_12;

ada 《= synthesized_wire_2;

gdfx_temp_signal_1 《= (l & l & h & h & h & l);

gdfx_temp_signal_0 《= (h & l & h & h & l);

u1 : lpm_bustri_0----三态总线缓冲器,允许采样的数据输出到dsp的数据总线上

port map(enabledt =》 drd,

data =》 ado,

tridata =》 d);

u2 : lpm_counter_1----计数器,把数据总线宽度改为3位

port map(sload =》 synthesized_wire_0,

clock =》 synthesized_wire_1,

aload =》 xfa0,

data =》 cmd(2 downto 0),

q =》 synthesized_wire_2);

u3 : lpm_dff_1---d触发器,数据总线宽度为8位,接收来自于dsp的数据

port map(clock =》 cmdck,

data =》 d(7 downto 0),

q =》 cmd);

u4 : lpm_compare_1---比较器,比较cmd(5..3)和cmd(2..0)的值,即轮询采样通道

port map(dataa =》 cmd(5 downto 3),

datab =》 synthesized_wire_2,

aeb =》 synthesized_wire_0);

synthesized_wire_1 《= not(aq(4));

nrw《= not rw;

cmdck《= not( not page3 and(not rw)and a6 and a5 and a4 and (not a3));

----通道控制地址编码

drd 《= not page3 and rw and a6 and a5 and a4 and a3;----采样地址编码

clka 《= not(clk);

u5 : lpm_counter_2---产生计数脉冲

port map(sload =》 synthesized_wire_3,

clock =》 hfp(5),

data =》 gdfx_temp_signal_0,

eq =》 sq,

q =》 aq);

u5 : lpm_dff_5---缓冲器

port map(clock =》 synthesized_wire_12,

data =》 synthesized_wire_5,

q =》 ado);

synthesized_wire_12 《= sq(12) or 0 or xfa0;

synthesized_wire_3 《= xfa0 or sq(14);

aden 《= not(xfa0);

synthesized_wire_10 《= hfp(5) and hfp(4) and hfp(0) and synthesized_wire_6 and synthesized_wire_7 and synthesized_wire_8;

synthesized_wire_7 《= not(hfp(2));

synthesized_wire_6 《= not(hfp(3));

inta2 《= xfa0 or synthesized_wire_9;

u6 : lpm_shiftreg_1----串行数据输入转为并行数据输出

port map(shiftin =》 adout,

clock =》 hfp(5),

q =》 synthesized_wire_5);

u7 : lpm_counter_3---产生时钟信号

port map(sload =》 synthesized_wire_10,

clock =》 h1ck,

data =》 gdfx_temp_signal_1,

q =》 hfp);

synthesized_wire_8 《= not(hfp(1));

adsck 《= not(hfp(5));

synthesized_wire_9 《= not(synthesized_wire_12);

h 《= 1;

l 《= 0;

end;

把该vhdl程序写入到epm7512ae芯片中的,对数据进行采样编程就简单了许多。在.cmd文件的memory段中加入adport :org=0x00c00070,len=9。然后通过自定义数据段把数组adport[8]映射到段adport中。下面给出用c编写的采样主要程序。

main()

{

……

iof = 0x26;/*置max1162数据输出端为高阻态*/

adport[0] = 0x28;

/*采样通道选择:0通道~5通道,总共6路;若设adport[0]=0x38,则通道为:0通道~7通道,总共8路。同理可进行其他设置*/

ie = 4;/*中断使能*/

iof = 0x22;/*启动adc*/

/* adport[0]对应地址为0x00c00070,配置寄存器有6位,0、1、2位对应起始通道,3、4、5位对应结束通道。adport[8]对应地址为0x00c00078,是控制寄存器*/

……

}

在中断服务子程序接收采样的数据,程序如下。

c_int02()

{

ad[adi++] = adport[8];/*把采集的数据十六进制数据存入数组ad中*/

if(adi》0x7ff) /*存入的数据大小为2k×16bit,根据内存大小动态改变*/

adi &= ox7ff;

}

结论

经过实际验证,本adc系统在低成本的情况下的采样精度达到了13位,这在16位的adc芯片中达到很好的水平,并被应用到高精度的工业控制中。利用tms320vc33和epm7512ae,灵活方便地实现了对高精度模数转换器max1162的控制和动态多通道采样,简化了系统设计的复杂性,同时使得dsp的编程处理变得非常高效简洁。若应用在要求更加严格的场面,本系统有待做进一步的改进,把adc芯片更换为并行输出,同时把cpld芯片更换为cycloneii fpga,dsp芯片用tms320c6713,同时加入噪声抑制设计,这样整个系统性能将会显著提高。在一定的条件下,和adc模块相类似,本系统可以经过扩充,实现更多路的信号采集。

-

双DSP的多路视频监控系统设计2011-05-03 0

-

利用DSP系统实现多路测量信号扩频传输实现2019-07-08 0

-

怎么利用AD7892SQ和CPLD设计一个多路信号采集威廉希尔官方网站 ?2021-05-08 0

-

基于CPLD和DSP的线阵CC 检测系统的设计2009-08-13 569

-

基于DSP和DSP/BIOS的实时雷达信号采集与处理系统2010-01-16 529

-

多路测量信号扩频传输的DSP系统实现2010-02-24 647

-

CPLD在多路高速同步数据采集系统中的应用2009-03-28 993

-

利用CPLD实现多路数据采集2009-05-05 1805

-

基于DSP+CPLD的智能IED设计2011-07-02 1416

-

基于DSP的声雷达信号采集系统2011-08-17 1562

-

基于CPLD的多路音频采集系统2016-01-21 644

-

基于CPLD控制的通用视频采集模块详述2017-10-20 829

-

如何DSP设计语音信号采集系统的论文说明2019-01-24 871

-

如何使用FPGA和ARM设计和实现多路视频采集系统2019-11-19 1137

-

采用复杂可编程逻辑器件实现多路信号采集系统的设计2020-03-03 1507

全部0条评论

快来发表一下你的评论吧 !