采用VHDL语言和PLD的可控纳秒级脉冲信号发生器的设计

描述

随着电子技术的迅速发展,高速信号触发源已经广泛应用于通讯、雷达等各种电子系统的测试和精确控制中。这就要求有一个稳定性好、纳秒上升沿、可控的脉冲发生器。但是,国内至今还没有合乎这些要求的商用脉冲发生器。即使在国际上普遍使用的加拿大生产的AVI-N型脉冲发生器也存在着幅度小、重复率低、易损坏等缺点。针对此现状,设计一款高速脉冲信号发生器是非常有意义的。可编程逻辑器件(PLD)经历了PAL,GAL,CPLD和FPGA几个发展阶段,技术日趋成熟。采用VHDL语言对PLD进行编程设计具有更改灵活、调试方便、操作性强、系统可靠性高等众多优点,并有利于硬件设计的保护,防止他人对威廉希尔官方网站

的分析、仿照。因此,利用PLD器件为核心构造高速脉冲信号发生器是一种有效的方法。

1 基本原理

设计采用的XILINX公司的复杂可编程逻辑器件(CPLD)几乎可适用于所有的门阵列和各种规模的数字集成威廉希尔官方网站 ,他以其编程方便、集成度高、速度快、价格低等特点越来越受到设计者的欢迎。选用的CPLD为XILINX公司的XC9572XL,属于XC9500系列,是目前业界速度较快的高集成度可编程逻辑器件。

CPLD开发软件用ISE 6.0+ModelSim 5.7SE,该软件是一个完全集成化、易学易用的可编程逻辑设计环境,并且广泛支持各种硬件描述语言。他还具有与结构无关性、多平台运行、丰富的设计库和模块化的工具等许多功能特点。

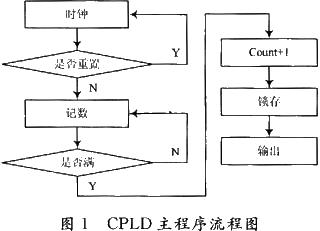

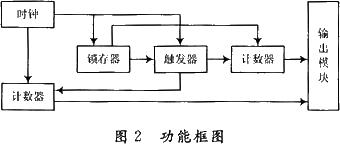

CPLD主程序流程图如图1所示,时针信号是整个程序的关键,通过时钟对各个模块进行精确控制,实现基本功能。时钟信号的精准度决定了输出脉冲信号的精准度。时钟源采用了4脚晶振,可以输出一个稳定的时钟信号。CPLD内部威廉希尔官方网站 资源分配如图2所示。

时钟信号和复位信号作为输入信号,控制脉冲信号的输出。系统分4个模块,包括计数器、锁存器、触发器和数据输出模块。时钟信号和复位信号分别加在计数器和触发器上,计数器计数通过锁存,在时钟信号作用下同步触发输出信号。当复位信号到来时,计数器重新清零计数。

当时钟的上升沿到来时对高频时钟进行计数,CPLD内部建立一个5位计数器,计数器满后自动重置为0,输出端把计数器的各位进行输出,计数器满后也输出一个高电平。第一级输出端一共有7个,可以实现对时钟的2,4,8,16,32,64分频以及单脉冲输出。在CPLD内部再建立一个3位计数器,对前级4分频信号再做计数,调节占空比,控制脉冲输出,同时对一级分频信号进行相与输出。设置一个复位端,当高电平时候,对威廉希尔官方网站

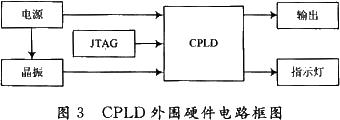

进行复位,计数器重新开始工作。通过复位端可以很好地控制脉冲输出,并且输出信号脉冲宽度在不同的分频接口可以得到不同的脉冲宽度信号,也可以通过修改程序实现脉冲宽度的改变。CPLD外围硬件威廉希尔官方网站

包括了电源、晶振、输出端口、指示灯,如图3所示。

本设计选用的外部计数时钟频率为100 MHz,因此所产生脉冲的周期最小是10 ns,脉宽调节最小为5 ns,调节步长为5 ns。该脉冲发生器可以实现多路输出,脉冲输出共有9路,其中1路可以实现单脉冲输出,其余8路可以输出不同脉宽的纳秒级脉冲。若要提高脉冲发生器的精度,应提高计数时钟的频率。同时选用速度等级更高的PLD。若要增加脉冲周期及脉宽的可调范围,则应选用容量更大的PLD。

2 仿真验证

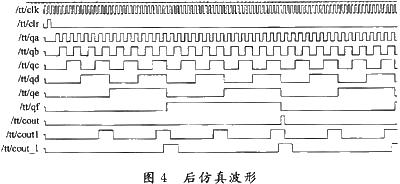

仿真是验证设计的一个重要环节,如果仿真没有通过,设计就必须重来,以便硬件调试的胜利通过。在ISE中,建立仿真文件并调用ModelSim 6.0对设计进行行为仿真。在第2个脉冲到来时进行计数器置零,开始计数,对每个输出端口的波形都进行仿真测试。从仿真波形中可以预测出,可编程器件成功地对脉冲进行控制,然后分频输出,达到预定的要求。

行为仿真只是对VHDL语言进行逻辑综合后仿真,布局布线后仿真则是在具体器件和硬件资源分配后,利用从布局布线中提取的一些信息,其中包括了目标器件及互连线的时延、电阻、电容等信息,并考虑走线之间的相互影响后产生的仿真波形。图4是布局布线后仿真图,可以看到在CLR信号有效开始,输出端经过4个周期的延迟后才响应到有效的复位信号,这个说明器件延时加上互连线延时为4个周期,但是这并不影响设计输出脉冲的质量,在其他电子设计中却要考虑到这个延迟。

3 试验结果

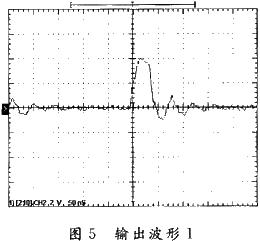

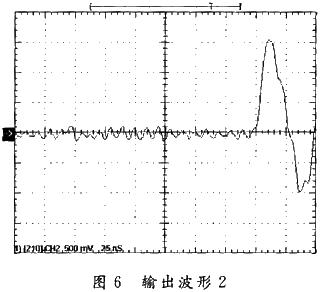

做好威廉希尔官方网站

版,调试程序成功后,用型号为TektronixTDS210示波器测出两个端口的输出波形如图5和图6所示。图5中波形幅度为3.98 V,峰峰值为4.98 V,脉冲宽度为37.8 ns,上升沿为16.7 ns;图6波形幅度为1.53 V,峰峰值为2.51 V,脉冲宽度为19.8 ns,上升沿为9.7 ns。在示波器中显示,得到纳秒脉冲信号非常稳定,可以作为一个稳定的纳秒信号源。每个脉冲过后都有一个小的负脉冲,并且上升沿和下降沿并没有像仿真时短,主要原因是:一是仿真在一个相对理想的条件下进行的,对器件资源在威廉希尔官方网站

中的实际体积忽略;二是芯片的微加工制造工艺不精确,寄生电容电阻的大小没有精确计算,可以在输出端加电容接地减小过脉冲。

4 结 语

本文利用XILINX公司的复杂可编程逻辑器件,结合VHDL语言,提出了一种可控纳秒级脉冲信号发生器的设计方法,并且通过仿真验证,得到脉冲宽度最小为19.8 ns,上升沿为9.7 ns的脉冲。在千伏高压纳秒脉冲发生系统中,采用MOS管、二极管、脉冲形成线等作为核心器件,该信号源必不可少的要一个触发源。利用可控高速信号发生器作为触发源,可以有效地实现对千伏高压的精确控制。在高速数字系统中,数据在器件间的串行传输速率可以达到几百Mb/s。此时,由于时钟周期非常小(通常只有几纳秒),为了保证高速数据的可靠接收,数据与时钟的相对位置要求非常严格,以避免发生数据的错位或在数据变化边沿对数据采样,亦可采用该多路高速信号发生器。简便可靠的纳秒信号发生器在电子系统设计中将越来越具有使用价值。

-

求一份利用PLD构造高速脉冲信号发生器的方案2021-04-14 0

-

正弦波信号发生器VHDL源代码2008-01-02 2052

-

Rogowski线圈信号电阻对纳秒级脉冲大电流的响应2009-10-31 492

-

基于SoPC的脉冲发生器2011-01-04 475

-

纳秒级窄脉冲发生器威廉希尔官方网站2009-02-28 3136

-

延时可控高压脉冲发生器的设计2009-07-15 2086

-

基于ECL门威廉希尔官方网站 的UWB信号发生器的设计2009-11-20 1618

-

纳秒级高压频率脉冲发生器的实现2011-09-09 1640

-

脉冲信号发生器原理2017-10-26 22249

-

脉冲信号发生器设计2018-08-21 19929

-

高压纳秒脉冲发生器2022-07-01 636

-

什么是信号发生器 信号发生器类型总结2022-08-02 4889

-

脉冲发生器输出是1吗?信号发生器怎么只发一个脉冲?2023-08-24 2037

-

脉冲发生器是什么意思?脉冲发生器怎么使用?2023-08-24 3870

-

信号发生器如何发出双脉冲?2023-12-21 2152

全部0条评论

快来发表一下你的评论吧 !