基于CY7C68013芯片接口和可编程特性的数据采集系统的设计

描述

在现代电子系统中,在信号测量、图像处理、音视频信号处理等一些高速、大容量的信号采集和传输过程中,数据的实时采集和实时传输受到人们越来越广泛的重视。现在通用的数据采集卡一般是PCI卡或是ISA卡,这些采集卡存在诸多缺点,比如安装不方便、传输速度慢、受计算机插槽数量、地址、中断等资源的限制.可扩展性差。

LJSB(Universal Serial Bus),其中文名称为“通用串行总线”。他是为了解决计算机外设种类口益增加与有限的主板插槽和端r丁之间的矛盾.由Intel,Microsoft,IBM,NEC,lucent等7家厂商共同制定的总线标准。目前,常用的LISB 2.O版本支持的最高传输速度可达到480 Mb/s.他以速度快、成本低、可靠性高、支持即插即用和热插拔等优点,迅速得到众多PC厂商的大力支持。同时,开发这种基于uSB 2.0的高速数据采集系统,代表了现代数据采集和传输系统的发展趋势,他也将被越来越多的用户所接受。

1 系统硬件整体设计

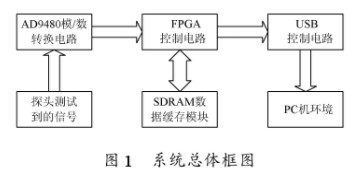

该系统总体框架为PC机(能支持USB 2.O协议的计算机)、A/D转换模块、FPGA控制模块、LYSB控制模块,如图l所示。

从整体上看结构可分为2个部分:高速数据采集模块的设计;USB 2.O高速数据传输系统。

1.1数据采集模块

该系统主要由l片高速AD 芯片、1片SDRAM和l片A1tera公司的FPGA构成。由于系统设计采样速度最大为1()0 MHz.据采样定理,采样频率至少应在200MHz以上,所以A/D芯片采用Analog公司的高速A/D芯片AD9480。该芯片转换精度8 b.单一3.3 V电源供电,低功耗,最高工作速度为250 MS/s,采用差分形式、LVDS电平输出,经过测试可以很好地满足系统要求。

为了满足数据采集中高速实时流数据的应用,避免FIFO溢出,本系统通过FPGA及SDRAM构造一个大容量的FIFO,可以提供一个低成本并且能满足高速实时流数据传输的方案。

低速数据采集系统常使用MCU作为CPU来控制,但在高速数据采集系统中,采样速度往往受MCU速度的影响,而且随着速度的提高,ADC,SDRAM和MCtJ之间的时序同步问题也显示出来,因此系统使用了高速FPGA芯片来控制ADC和SDRAM,从而很好地解决了时序精度和同步的问题。

FPGA选择A1tera公司的CYCLONE系列高性价比产品EPlC6T144C8。他基于1.5 V,O.3 μm及全层铜SRAM工艺,其密度增加至20 060个逻辑元件(LE),RAM增加至288 kb。他具有锁相环以及DDR SDR和速度周期RAM(FCRAM)存储器所需的专用双数据(DDR)接口等。CYCLONE器件支持多种I/O口标准,包括640 Mb/s的LVDS,以及速率为33 MHz和66 MHz,数据宽度为32 b和64 b的PCI。FPGA实现的功能逻辑主要有:实现对ADC的控制,开始A/D转换;为ADC同步提供SDRAM地址计数和写信号,把每次A/D转换的结果直接存入SDRAM,并自动增加地址;当地址计数器达到最大时,发出RAMFULL中断信号,提示SDRAM已满。

FPGA的功能逻辑用VHDL语言实现,其编译和仿真使用Altera公司的QuartusⅡ5.1,使用ByteBlastⅡ并行编程电缆和JTAG口下载编程和配置文件。

1.2 USB 2.0高速数据传输

用于USB设备开发的芯片通常有2种类型:一种是MCU集成在芯片里面,如CYPRESS的EZ-USB;另一种是纯粹的USB接口芯片,仅处理USB通信,使用时必须由外部微控制器(MCU)进行控制,如Philips的PDIUSBD1 2,National Semiconductor的USBN9604等。在本设计中经过论证分析,采用第一种类型,采用Cypress公司的EZ-USB FX2系列的CY7C68013芯片。

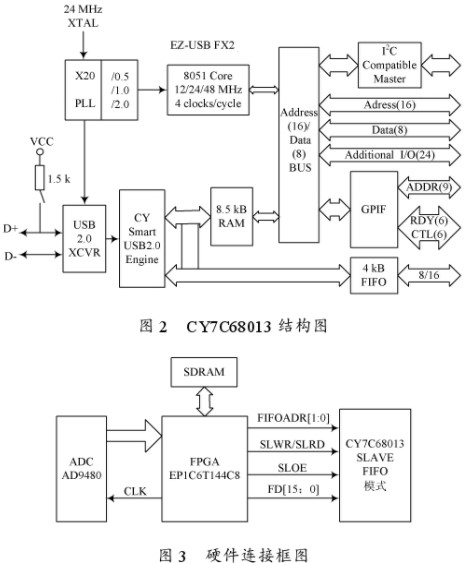

1.2.1 EZ-USB FX2(CY7C68013)芯片

Cypress公司的EZ-USB FX2系列芯片是最早符合USB 2.0协议的微控制器之一,他集成了符合USB 2.O协议的收发器(transceiver),串行接口引擎(SIE),增强型的8051内核以及可编程的外围接口。FX2系列芯片独特的结构使得数据传输速度最高可达56 Mb/s,最大限度地满足了USB 2.O的带宽。CY7C68013集成标准8051内核,且具有下列增强特性:可以达到48 MHz时钟;每条指令占4个时钟周期;2个USARTS;3个定时/计数器;扩展的中断系统;2个数据指针。

805l程序从内部RAM开始运行,借助如下3种方式进行程序装载:通过USB下载,从E2PROM中装载;通过外部存储器设备。内部集成了达4 kB的FIFO,用户程序发送数据时,直接从FIFO里读取,保证了数据高速传输,与外部实现透明数据传输。

1.2.2 硬件连接

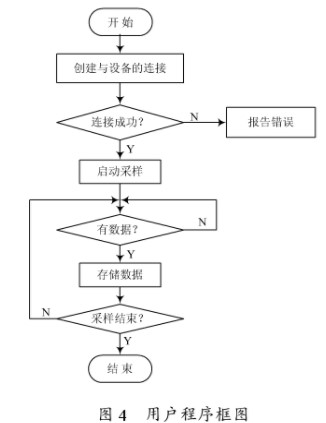

根据系统对数据传输的速度和实时性的要求,配置CY7C68013工作的接口模式为Slave FIFO模式。当进行数据采集时,硬件连接方式如图3所示。

A/D转换器的采样时钟同时作为CY7C68013的Slave F=IFO模式的读写控制时钟,即CY7C68013的接口时钟连接到IFCLK引脚。SLWR/SLRD是CY7C68013Slave FIFO的写使能/读允许信号。FPGA向CY7C268013Slave FIFO提供Slave FIFO输出允许信号SLOE,仅在数据输出时有效。FD[15:0]为16 b双向数据总线。FI-FOADR[1:0]为端点FIFO选择信号。在数据输入时固定为OO,选择端点2;在数据输出时固定为10,选择端点6。

2 系统程序设计

USB系统的软件设计可分为3部分:固件设计、驱动程序设计和用户端的应用程序设计。

2.1 固件(firmware)设计

固件程序实际上就是单片机方面的软件设计,他是所有基于微控制器及其外围威廉希尔官方网站 的功能设备正常工作必不可少的部分,其作用就是辅助硬件。

2.1.1 软件设计的主要功能

与软件设计主要有以下几种功能:初始化工作,包括设置一些特殊功能寄存器的初值以实现所需的设备属性或者功能,例如开中断,使能端点,配置端口等;辅助硬件完成设备的重新枚举过程,包括模拟设备的断开与重新连接,对接收到的设置包进行分析判断,从而对主机的设备请求作出适当的响应,完成主机对设备的配置任务;对中断的处理;数据的接收和发送;外围威廉希尔官方网站 的控制。

Cypress公司为了简化和加速用户使用EZ-USBFX2芯片进行USB外设的开发过程,提供了一个完整的固件程序的架构,可以在KEILC5l环境下开发,用户只需要提供一个USB描述符表,添加其他端点接收和发送数据的通信代码,以及控制外围威廉希尔官方网站 的程序代码。由于开发框架的引入,大大缩短了用户的研发周期。

2.1.2 软件设计的框架

该框架由以下几部分组成:

(1)Fw.C中包含了程序框架的MAIN函数,管理整个51内核的运行,因为Cypress对这个部分的功能进行了精心划分,一般是不用改动的。

(2)用户必须将PERIPH.C实例化,他负责系统周边器件的互联。固件的设计主要针对这个文件,用户必须根据自己系统的需要,实例化这个文件,以实现自己的功能。在这个文件中有几个函数是比较关键的,在这里做特别说明:

TD_Init函数 负责对USB端点进行初始化设置。在FX2再次枚举和开始任务分配前被调用,其目的是初始化各个端口以及各端口的先入先出缓冲区。

TD_Poll函数 负责系统中循环任务的处理。他主要是对各个端点的状态进行查询,处理各种OUT或IN端点的交互。值得说明的一点是,这种处理只是辅助性质的,大部分工作由硬件自动完成。

DR-VendorCmnd函数 主要负责用户自定义命令的译码工作,用户请求通过端点O传输给内核。由于CY7C68013上SIE硬件的支持,用户只需查询固定地址单元即可获得当前的命令代码。

DSCR.A51是描述表文件,负责USB设备的描述工作,CY7C68013在上电后自动利用其中的VID和PID取代默认的VID和:PID。两个包含文件EZtJSB.LIB和US-BJMPTB.OBJ,前者是EZUSB函数库的二进制文件,后者是USB的中断向量表。

固件调试,使用Cypress提供的EZ-LISB controlpanel,具体的操作读者可以参考其自带帮助。对编译好的固件代码,Cypress为LISB总线设备开发者提供了2种方法向。EZ一USB芯片下载8051固件代码:

一种是主机通过软件下载固件从主机上下载8051固件代码,他为用户提供了很大的灵活性。这种方法充分利用EZ-USB内部的8 k RAM来装载8051代码和数据。由于EZ-USB具有重新枚举的能力,所以在初始化枚举以后,用户不需要断开设备就可以装载新的。设备描述符和8051程序代码都能通过主机中的磁盘文件下载;另外一种是由E2PROM通过I2C口来下载固件。EZ-USB支持外部E2PROM通过总线来下载固件,这种方式使开发者可以从外围硬件下载8051程序代码。

2.2驱动程序设计

USB设备驱动程序是开发USB外设的一个关键,他在整个系统中处于主机端应用程序和设备端Firmware之间。他的主要作用是使操作系统能够识别USB设备,并建立起主机端和设备端之间的通讯。

USB驱动程序属于先进的wDM(Win32 Driver Mod-e1)驱动程序模式,支持即插即用功能。在wDM驱动程序模式中,每个硬件设备至少有2个驱动程序:一个为功能驱动程序,即硬件设备的驱动程序,他了解USB外设硬件工作的所有细节,负责初始化I/O操作;另一个为总线驱动程序,他负责管理USB外设与主机的连接,如检测接入主机的USB设备,并确定设备的资源使用情况等。总线驱动程序要负责枚举总线,并为每个设备创建一个PDO(物理设备对象)。当总线驱动程序发现有设备接人或拔出总线时,他要向上层驱动程序报告事件的发生。功能驱动程序位于总线驱动程序的上层,他要为设备创建一个FDO(功能设备对象)。USB驱动程序也称客户驱动程序,他从不直接与硬件对话,仅靠创建USB请求块URB,并使用USB驱动程序接口USBDI将URB提交到总线驱动程序就可以完成硬件操作。

在windows操作系统下,开发wDM驱动程序可以有2种选择:一种是选择微软公司的DDK(驱动程序开发包)。DDK提供了创建wDM驱动程序的开发环境,并提供了用于开发Windows 2000和Windows XP驱动程序的头文件、库函数、源代码、各种工具和文档资料;另一种选择是使用一些驱动程序的辅助开发工具,比如Driver Stu-dio,windriver等,这些开发工具可以根据用户的需求,为用户自动生成驱动程序,用户只需要在生成驱动程序前,在向导框中按照提示填入自己的需求,并对生成的驱动程序做一些小的修改即可。

Cypress FX2开发包提供了一个通用的驱动程序,可被用于基于EZ-uSB系列芯片的uSB设备。该程序可不加修改经DDK编译后直接使用,在应用中可以看到其运行稳定。当然,用户也可以以这个驱动程序为起点,创建自己的驱动程序。 2.3应用程序设计

应用程序设计以驱动程序为桥梁,对15SB设备进行命令控制,处理uSB设备传回的数据,例如波形显示、频谱分析等。采集系统的主机端工作在Windows操作系统下,所以主机端应用程序的设计需要windows平台下的开发工具如Visual C++,C++Builder。等。主机端软件的关键是实现从uSB设备读取指定数量的数据以及向USB设备发送指定数量的数据,另外,还有向USB设备发送USB标准设备请求和特定的命令,这种命令包括厂商定义的命令和用户自定义的命令。

CypreSS FX2开发包提供的EZ-USB通用驱动程序为主机端的用户态应用程序提供IJSB标准设备请求和数据传输的接口。所有用户态程序访问EZ USB通用驱动程序都是通过I/OControl调用。用户态程序首先通过调用Win32函数CreatFile()得到设备驱动程序的句柄。然后调用win32函数DeviceloControl(),通过得到的句柄把I/O Control Code(IOCTL)和相关的输入输出缓冲区提交给驱动程序。用户程序框图如图4所示。

3 结 语

随着笔记本电脑的迅速普及,高性能便携式采集系统将会受到工程师们越来越多的青睐,尤其是在RS 232接口已被大多数笔记本电脑摈弃的今天,对基于USB接口的数据采集系统的需求就变得更加迫切。在该高速同步数据采集系统的设计中,CY7C68013芯片灵活的接口和可编程特性简化了外部硬件的设计,提高了系统的可靠性,且利于设备的生产与调试。另外,设备的可热插拔特性使该系统具有便携式的特点,使用方便,无需关机重启或打开机箱进行安装。事实证明,该基于2.0接口的高速数据采集系统完全满足设计和使用要求。

-

求大侠帮忙 CY7C68013 与CPLD通信问题2013-03-05 0

-

cy7c68013开发包及驱动2009-04-11 1830

-

基于CY7C68013的USB数据采集系统2009-09-14 747

-

USB2.0接口芯片CY7C68013的固件程序开发2009-04-11 4787

-

CY7C68013器件中文手册2011-01-21 850

-

CY7C68013 GPIF可视化编程软件2011-04-29 1017

-

基于CY7C68013的CCD图像传输系统2011-05-17 1080

-

基于CY7C68013A的并口转USB口数据采集系统设计2011-08-29 1578

-

基于CY7C68013的高速数据通信接口设计2011-09-08 853

-

CY7C68013的固件程序开发方法2011-09-09 1663

-

基于USB2.0芯片CY7C68013的高速数据通信接口设计2011-09-21 1334

-

CY7C68013和FPGA的数据通信2012-03-28 10692

-

cy7c68013数据手册2016-01-22 1104

-

USB2.0微控制器CY7C68013的数据采集系统的设计2016-01-22 880

-

采用CY7C68013芯片的系统固件程序设计2016-01-22 1031

全部0条评论

快来发表一下你的评论吧 !