PCIe总线的信号介绍

接口/总线/驱动

描述

本篇主要介绍PCIe总线相关的信号。

PCIe总线相关的信号主要分为以下几类:

辅助信号线

数据线

电源

1、Auxiliary Signals

The auxiliary signals are provided on the connector to assist with certain system level functionality or implementation. These signals are not required by the PCI Express architecture. The optional low speed signals are defined to use the +3.3V or +3.3Vaux supplies, as they are the lowest common voltage available.

1.1、PERST#信号

该信号为全局复位信号,由处理器系统提供(RC),处理器系统需要为PCIe插槽和PCIe设备提供该复位信号。PCIe设备使用该信号复位内部逻辑。当该信号有效时,PCIe设备将进行复位操作。PCIe总线定义了多种复位方式,其中Cold Reset和Warm Reset这两种复位方式的实现与该信号有关。

为了支持热插拔,在原理图设计时,在该引脚和GND之间接一个1000pF的电容,热插拔时能进行复位。

1.2、REFCLK+和REFCLK-信号

在一个处理器系统中,可能含有许多PCIe设备,这些设备可以作为Add-In card与PCIe插槽连接,也可以作为内置模块,与处理器系统提供的PCIe链路直接相连,而不需要经过PCIe插槽。PCIe设备与PCIe插槽都具有REFCLK+和REFCLK-信号,其中PCIe插槽使用这组信号与处理器系统同步。

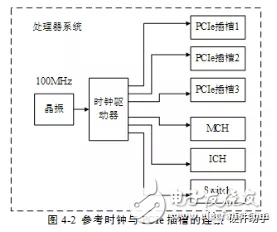

在一个处理器系统中,通常采用专用逻辑向PCIe插槽提供REFCLK+和REFCLK-信号。其中100MHz的时钟源由晶振提供,并经过一个“一推多”的差分时钟驱动器生成多个同相位的时钟源,与PCIe插槽一一对应连接。

PCIe的REFCLK+/-使用的是LPHCSL电平。

V3.0中关于Refclk的说明如下:

V4.0中关于Refclk的说明如下:

Common Refclk Rx architectures are characterized by the Tx and Rx sharing the same Refclk source. A single Refclk source drives both the Generator and the DUT. It is typical that SSC would be applied.

A data clocked Rx architecture is characterized by requiring the receiver’s CDR to track the entirety of the low frequency jitter, including SSC. Since the Tx and Rx do not share a common Refclk, the jitter transfer function includes only the Tx PLL transfer function plus the lowpass characteristics of the CDR.

The 8.0 GT/s PCI Express Base Specification does not explicitly define the requirements for a separate Refclk architecture. This is the identical position taken by the base specification for 2.5 GT/s and 5.0 GT/s.

When tolerancing a PCI Express Rx in a separate Refclk architecture, the generator and DUT are furnished with separate Refclks that each are within ±300 PPM of the nominal frequency of 100 MHz. SSC must be turned off for both Refclk sources. These limitations are required to guarantee proper operation of the buffering and flow control in the Rx.

PCIe插槽需要使用参考时钟,其频率范围为100MHz±300ppm,单端摆幅为0~0.7V。处理器系统需要为每一个PCIe插槽、MCH、ICH和Switch提供参考时钟。而且要求在一个处理器系统中,时钟驱动器产生的参考时钟信号到每一个PCIe插槽(MCH、ICH和Swith)的距离差在15英寸之内。通常信号的传播速度接近光速,约为6 in/ns,由此可见,不同PCIe插槽间REFCLK+和REFCLK-信号的传送延时差最大约为2.5ns。

当PCIe设备作为Add-In卡连接在PCIe插槽时,可以直接使用PCIe插槽提供的REFCLK+和REFCLK-信号,也可以使用独立的参考时钟,只要这个参考时钟在100MHz±300ppm范围内即可。内置的PCIe设备与Add-In卡在处理REFCLK+和REFCLK-信号时使用的方法类似,但是PCIe设备可以使用独立的参考时钟,而不使用REFCLK+和REFCLK-信号。

在PCIe设备配置空间的Link Control Register中,含有一个“Common Clock Configuration”位。当该位为1时,表示该设备与PCIe链路的对端设备使用“同相位”的参考时钟;如果为0,表示该设备与PCIe链路的对端设备使用的参考时钟是异步的。

在PCIe设备中,“Common Clock Configuration”位的缺省值为0,此时PCIe设备使用的参考时钟与对端设备没有任何联系,PCIe链路两端设备使用的参考时钟可以异步设置。这个异步时钟设置方法对于使用PCIe链路进行远程连接时尤为重要。

在一个处理器系统中,如果使用PCIe链路进行机箱到机箱间的互连,因为参考时钟可以异步设置,机箱到机箱之间进行数据传送时仅需要差分信号线即可,而不需要参考时钟,从而极大降低了连接难度。

1.3、WAKE#信号

当PCIe设备进入休眠状态,主电源已经停止供电时,PCIe设备使用该信号向处理器系统提交唤醒请求,使处理器系统重新为该PCIe设备提供主电源Vcc。在PCIe总线中,WAKE#信号是可选的,因此使用WAKE#信号唤醒PCIe设备的机制也是可选的。值得注意的是产生该信号的硬件逻辑必须使用辅助电源Vaux供电。

WAKE#是一个Open Drain信号,一个处理器的所有PCIe设备可以将WAKE#信号进行线与后,统一发送给处理器系统的电源控制器。当某个PCIe设备需要被唤醒时,该设备首先置WAKE#信号有效,然后再经过一段延时之后,处理器系统开始为该设备提供主电源Vcc,并使用PERST#信号对该设备进行复位操作。此时WAKE#信号需要始终保持为低,当主电源Vcc上电完成之后,PERST#信号也将置为无效并结束复位,WAKE#信号也将随之置为无效,结束整个唤醒过程。

PCIe设备除了可以使用WAKE#信号实现唤醒功能外,还可以使用Beacon信号实现唤醒功能。与WAKE#信号实现唤醒功能不同,Beacon使用In-band信号,即差分信号D+和D-实现唤醒功能。Beacon信号DC平衡,由一组通过D+和D-信号生成的脉冲信号组成。这些脉冲信号宽度的最小值为2ns,最大值为16us。当PCIe设备准备退出L2状态(该状态为PCIe设备使用的一种低功耗状态)时,可以使用Beacon信号,提交唤醒请求。

1.4、SMCLK和SMDAT信号

SMCLK和SMDAT信号与x86处理器的SMBus(System Mangement Bus)相关。SMBus于1995年由Intel提出,SMBus由SMCLK和SMDAT信号组成。SMBus源于I2C总线,但是与I2C总线存在一些差异。

SMBus的最高总线频率为100KHz,而I2C总线可以支持400KHz和2MHz的总线频率。此外SMBus上的从设备具有超时功能,当从设备发现主设备发出的时钟信号保持低电平超过35ms时,将引发从设备的超时复位。在正常情况下,SMBus的主设备使用的总线频率最低为10KHz,以避免从设备在正常使用过程中出现超时。

在SMbus中,如果主设备需要复位从设备时,可以使用这种超时机制。而I2C总线只能使用硬件信号才能实现这种复位操作,在I2C总线中,如果从设备出现错误时,单纯通过主设备是无法复位从设备的。

SMBus还支持Alert Response机制。当从设备产生一个中断时,并不会立即清除该中断,直到主设备向0b0001100地址发出命令。

1.5、JTAG信号

JTAG(Joint Test Action Group)是一种国际标准测试协议,与IEEE 1149.1兼容,主要用于芯片内部测试。目前绝大多数器件都支持JTAG测试标准。JTAG信号由TRST#、TCK、TDI、TDO和TMS信号组成。其中TRST#为复位信号;TCK为时钟信号;TDI和TDO分别与数据输入和数据输出对应;而TMS信号为模式选择。

1.6、PRSNT1#和PRSNT2#信号

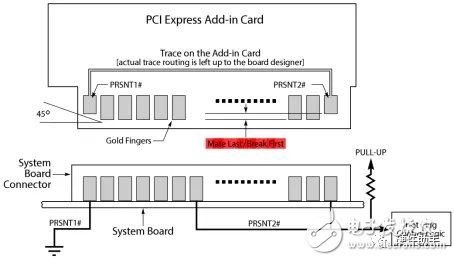

PRSNT1#和PRSNT2#信号与PCIe设备的热插拔相关。在基于PCIe总线的Add-in卡中,PRSNT1#和PRSNT2#信号直接相连,而在处理器主板中,PRSNT1#信号接地,而PRSNT2#信号通过上拉电阻接为高。

当Add-In卡没有插入时,处理器主板的PRSNT2#信号由上拉电阻接为高,而当Add-In卡插入时主板的PRSNT2#信号将与PRSNT1#信号通过Add-In卡连通,此时PRSNT2#信号为低。处理器主板的热插拔控制逻辑将捕获这个“低电平”,得知Add-In卡已经插入,从而触发系统软件进行相应地处理。

Add-In卡拔出的工作机制与插入类似。当Add-in卡连接在处理器主板时,处理器主板的PRSNT2#信号为低,当Add-In卡拔出后,处理器主板的PRSNT2#信号为高。处理器主板的热插拔控制逻辑将捕获这个“高电平”,得知Add-In卡已经被拔出,从而触发系统软件进行相应地处理。

不同的处理器系统处理PCIe设备热拔插的过程并不相同,在一个实际的处理器系统中,热拔插设备的实现也远比上图中的示例复杂得多。值得注意的是,在实现热拔插功能时,Add-in Card需要使用“长短针”结构。

PRSNT1#和PRSNT2#信号使用的金手指长度是其他信号的一半。因此当PCIe设备插入插槽时,PRSNT1#和PRSNT2#信号在其他金手指与PCIe插槽完全接触,并经过一段延时后,才能与插槽完全接触;当PCIe设备从PCIe插槽中拔出时,这两个信号首先与PCIe插槽断连,再经过一段延时后,其他信号才能与插槽断连。系统软件可以使用这段延时,进行一些热拔插处理。

2、数据信号

PCIe链路使用“端到端的数据传送方式”,发送端和接收端中都含有TX(发送逻辑)和RX(接收逻辑),PCIe总线链路的一个数据通路(Lane)中,由两组差分信号,共4根信号线组成,TXn/TXp和RXn/RXp,x1就包含一个Lane,x2就包含两个Lane。

3、电源

PCIe接口的电源包括+12V、+3.3V、+3.3Vaux三种。每一种电源的供电能力将在后面的文章《PCIx系列之“PCIe总线电源管理”》中有详细说明。

以上就是针对PCIe总线的信号介绍,后续会针对电源管理、复位、AC耦合电容、硬件威廉希尔官方网站 设计等方面介绍PCIe总线。

-

PC介绍之PCIE、总线、内存、电源相关资料分享2021-12-28 0

-

基于PCIe总线的超高速信号采集卡的设计2011-01-06 1874

-

Pcie串行总线介绍#高速接口我是Coder 2021-08-11

-

PCIE总线基本资料2012-08-06 0

-

PCIE总线的FPGA设计方法2015-10-30 0

-

PCIE总线详细资料2016-02-15 0

-

PCIe总线的复位方式是什么?2019-10-16 0

-

pcie总线基础知识 精选资料推荐2021-07-29 0

-

PCIe总线和PCI总线有哪些不同之处呢2021-10-26 0

-

PCIE总线的多DSP系统接口设计2017-10-31 1020

-

PCIe总线AC耦合及高速信号调整技术2020-12-22 12951

-

PCIe总线的电源管理之去耦电容2020-12-22 7434

-

全面介绍PCIe总线的基础知识2021-12-14 1081

-

PC介绍之PCIE、总线、内存、电源2022-01-06 735

-

PCIe 9110IM PCIe总线转CAN设备手册2022-10-17 538

全部0条评论

快来发表一下你的评论吧 !